Key Benefits

- 降低基于 Arm 内核的系统级芯片开发风险

- 易于使用,效率更高

- 加速达成 PPA 目标

- 利用 PPA 推动技术和专业知识完成最后收敛

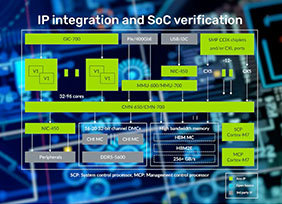

Arm 与 EDA 供应商合作开发了 EDA 参考流程。Cadence 与 ARM 紧密合作,基于 ARM®的设计,成功优化了我们的全流程数字电路设计解决方案。与使用通用 EDA 参考流程相比,使用由此开发出的数字实现参考流程能更有效地完成基于 Arm 内核的系统级芯片(SoC)的实现,更快地达成功耗、性能和面积(PPA)目标。

Arm 采用 Cadence® 的工具来开发自己的 IP。我们在早期就可以接触 Arm 内核,从而调整工具算法、功能和选项,并可以在 Arm 内核正式发布之前优化我们的流程。得益于以上几点,我们能够在通用 EDA 参考流程的结果基础上,改善 PPA 结果并缩短了周转时间(TAT)。

该流程适用于多种 Arm Cortex®-A、Cortex-R、Cortex-M 和 NeoverseTM 核心、多媒体产品(GPU、显示控制器、视频控制器)和互连核心。您将获得针对这些 CPU 和 GPU 配置以及热门晶圆代工厂工艺技术(包括FinFET和其他先进节点)的最佳脚本、布局方案和文档。

PPA可预测的快速运行周期

当您使用 Cadence 的 RTL 到签核流程来实现 Arm 内核时,我们会有经验丰富、与ARM密切合作构建参考流程的研发人员和产品工程师来参与整个实现流程。这些技术专家还拥有丰富的提升PPA的经验,完成过全球多个先进 Arm 设计的流片,涵盖 40nm 到 10 nm 及以下的各种工艺等级。

我们与 Arm 的早期合作为 Cadence 的数字实现参考流程提供了支持。借助我们的参考流程,您将获得适用于 Arm 处理器的从 RTL 到 GDSII 的设计技术,从而缩短芯片设计周期,并实现可预测的 PPA 结果。请联系您的 Cadence 销售代表以获取更多信息。这些流程还通过 Arm POP ™ IP 内核加速硬化技术进行了优化。使用这些流程,您将能够高效地生产基于 Arm 大小核 ™ 处理系统的系统级芯片。

针对低功耗进行优化

Cadence 提供了一套全面的解决方案,用于基于 Arm 的系统级芯片的设计、验证和功耗优化:

- 使用 Xcelium 仿真器和 Palladium® Z1 仿真平台,可以加速 Arm 内核在所有功耗模式下的功能验证

- Joules™ RTL Power Solution 有助于在设计的早期阶段准确估算功耗,并确定实际系统使用场景下的峰值功耗

- Genus™ Synthesis Solution 和 Innovus™ Implementation System 有助于同时优化漏电功耗和动态功耗,并且实现性能最大化和面积最小化

- Conformal® Low Power 是业界领先的低功耗形式化验证工具,通常用于验证基于 Arm 的系统级芯片设计

- Cadence签核工具,包括 Tempus™ Timing Signoff Solution、Quantus™ Extraction Solution 和 Voltus™ IC Power Integrity Solution,有助于加快签核速度,助您成功完成基于 Arm 的系统级芯片的流片任务

- 低功耗流程中的所有工具均支持业界标准的 CPF 和 IEEE 1801 格式来描述基于 Arm 的系统级芯片的功耗意图

We partnered closely with Cadence to utilize the Innovus Implementation System during the development of our ARM Cortex-A72 processor. This demonstrated a 5X runtime improvement over previous projects and will deliver more than 2.6GHz performance within our area target.

Noel Hurley, General Manager, CPU Group, ARM