概述

高速的仿真器,用于 IP 和系统级芯片验证收敛

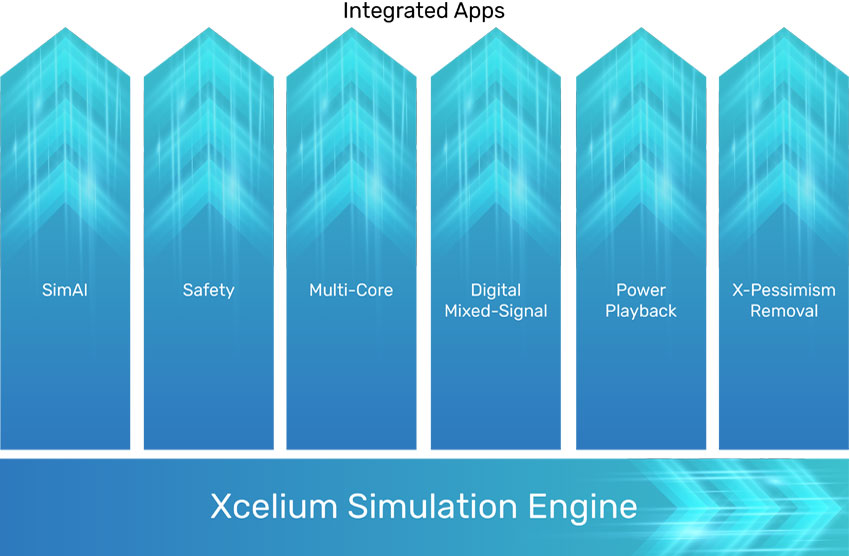

Cadence® Xcelium™ Logic Simulation 可为 SystemVerilog、VHDL、SystemC®、e、UVM、混合信号、低功耗和X态传播(X-propagation)提供业内优异的核心引擎性能。它对特定领域有相应的App,包括混合信号、基于机器学习的测试压缩和功能安全,助力设计团队尽早实现对 IP 和系统级芯片 (SoC) 设计的验证收敛。

核心优势

行业领先的软件仿真

广泛的语言支持

支持 SystemVerilog、VHDL、SystemC、e、UVM 和 IEEE UPF 标准

卓越的性能

自动化并行和增量构建技术,以支持大型SoC设计的编译,以及一流的仿真引擎以实现理想的回归吞吐量,包括一个多核引擎,以加速长时间运行的测试用例。

利用App实现加速

Xcelium App,如混合信号、基于机器学习的测试压缩和功能安全,便于混合和匹配整个设计和验证周期所需的不同技术

Xcelium SimAI App 发挥了机器学习技术的强大优势。它能根据 Xcelium 仿真器中运行的回归结果建立模型,从而根据具体目标生成新的回归结果。其中包括对整个设计或特定区域进行高效的浸泡测试,并提高回归效率。该应用还具备一项独特的功能,即查找关联错误,利用难以发现的故障信息找到与之关联的错误。凭借这些先进的机器学习技术,SimAI 有望显著提高设计效率,为用户带来巨大的性能飞跃。

Xcelium Mixed-Signal App 支持与 Cadence Spectre SPICE 模拟电路仿真器的协同仿真,以及基于先进的 SystemVerilog 实数模型的仿真。

Xcelium Multi-Core (MC) App 可实现 Xcelium 内核级多线程处理,显著缩短长时间运行的高活跃性测试运行时间,例如门级设计测试模式仿真。

Xcelium X-Pessimism Removal (XPR) App 采用先进算法,使软件仿真中 “X” 值的传播更加准确,从而缩短调试时间。

Podcast Series

Espresso and Electronics – Quick Sips of EDA Wisdom

客户案例

Xcelium Logic Simulator 客户评价

相关产品

Xcelium 仿真是更广泛的 Cadence 验证全流程的一部分,支持公司的智能系统设计™ (Intelligent System Design™) 战略,旨在实现 SoC 卓越设计。

Scale your tools with Cadence OnCloud Marketplace

Learn MoreTraining and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.

Find Answers in cadence technical forums