数字先进节点

为极具挑战性的鳍式场效电晶体 (FinFET) 设计实现最佳结果质量

Key Benefits

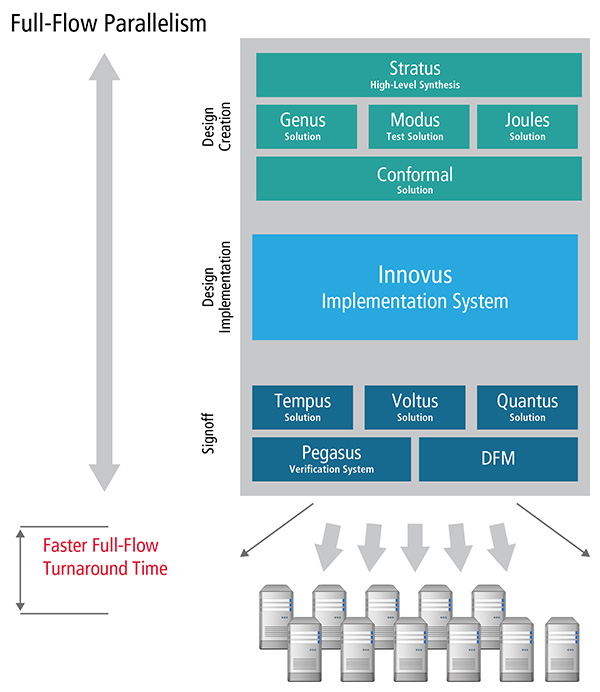

- 大规模并行技术,有助于处理大规模数据和复杂的先进节点

- 通过集成引擎提供智能算法,实现最佳 PPA 目标

- 全方位的全流程集成数字工具集,用于设计创建、实现和签核,加快先进节点的设计收敛速度

- Cerebrus™ Intelligent Chip Explorer 机器学习驱动的自动先进节点流程优化能够加速实现最佳 PPA 目标

应对先进节点的挑战

先进的 FinFET 系统和采用 FD-SOI 技术的平面系统改善了功率、性能和面积(PPA) 目标,但也带来了其他设计挑战。Cadence 开发了颠覆性的全流程数字工具集,以应对在设计创建、实现和签核阶段的这些设计挑战。在与晶体管打交道时,设计人员可能会遇到以下问题:

- 降低了漏电功耗,但动态功耗更为重要

- 当单次光刻不足时,会使用DPT来增强特征密度

- 多高度的单元库需要最佳的综合和放置,以达到最佳密度

- 摆放和优化必须考虑新的先进节点基础层约束

- 较大的设备端口电容会增加导线上的总电容

- 设计在低电压状态下运行,因此设计流程需要处理较低的Vdd电压

- 随着驱动强度的提高和高电阻导线的出现,电迁移 (EM) 和绝缘阻抗问题变得愈发重要

- 片上差异的影响凸显,必须通过正确的统计算法加以缓解

- 晶体管自热效应会影响信号 RMS 电流

Cadence® Full-Flow Digital Implementation and Signoff 工具可解决并支持当今的 FinFET 和更先进的FD-SOI 设计中的所有特殊要求。这些工具可预防并纠正有害的光刻热点、随机缺陷、片上工艺偏差以及由于化学机械抛光而引起的偏差。Cadence Innovus ™ Implementation System 通过基于规则和模型的设计同步分析(通过资格预审并与晶圆代工厂工艺仿真紧密相关),可将前期风险降至最低,并防止出现意外的重新设计和后期迭代。

DPT设计及其他功能

随着设计工艺发展到 20nm 以下,晶圆厂正在采用DPT来提高特征密度,因为单次光刻曝光通常无法提供足够的分辨率。在 16nm 和 14nm 级别,形状彼此接近,以至于单次光刻会产生许多干涉效应,因此需要使用多次光刻。使用两次光刻,每次可印刷一个双节距导线的掩膜。当两次光刻均完成后,将创建一个单个布局,导线间距达到最小。

7nm 工艺节点需要在设计过程中进行明确的全流程着色。RC 特征取决于颜色,即使在同一金属层上也是如此。随着晶圆代工厂陆续采用 5nm 和 3nm 工艺节点,需要采用极紫外光刻技术 (EUV),由此带来了额外的实现规则,如复杂的多高度标准单元库和准确度更高的库表征。用于集成电路设计的老旧软件无法提供所需的 DPT 或显式着色功能。不必担心,Cadence 开发了实现和签核工具,可帮助设计师应对此类问题和其他微型几何形状的影响。

针对先进节点进行优化的数字工具集

从统一的软件架构开始,Cadence 重新设计了用于先进节点的数字工具集。该集成数字架构以核心通用引擎和全流程优化为基础。在一处添加新功能后,多个应用皆可受益。借此,软件的智能程度得以提升,减少了漏洞数量,可为更新的节点提供快速特征部署,实现准确的早期预测和收敛相关性。

Cadence 全流程数字解决方案提供了大规模并行化,可为您带来诸多优势。其他单点工具流程由于缺乏并行性而效率低下,综合(synthesis)与实施(implementation)之间以及优化与签核之间存在多个瓶颈。通过使用全流程并行机制,Cadence 避免了这些瓶颈,并加快了运行时间。

您可以从 Cadence Genus ™ Synthesis Solution 开始创建设计,该解决方案利用物理方法,用于早期设计阶段的部件摆放、预测拥塞、层分配、可感知层的缓冲、RTL 优化、以及改善面积、时序和功耗目标。借助统一的布局引擎、全局布线引擎、延迟计算和寄生参数提取,Genus 解决方案可助力您准备设计,成功进入实现阶段。

Cadence Innovus Implementation System 为着色、DPT和针对高性能计算要求的独特“过孔支柱”(via-pillar) 方法提供全面的支持。GigaPlace ™ Engine 采用了一种前瞻性的布局摆放方法,涵盖了一些针对先进节点的功能,包括活动驱动的布局、裕量驱动 (slack-driven) 和电源驱动的布局、可感知引脚接入的布局以及 IR 驱动的布局。NanoRoute ™ Advanced Digital Router 针对包括多个 CPU 和其他复杂逻辑的高度复杂型设计进行了优化。GigaOpt ™ Optimizer 考虑了先进节点的特征,例如选择正确的层以实现最佳优化。具有层感知功能的布线驱动优化技术可大大改善时序收敛。

签核速度和效率

在过去的几年中,Cadence 引入了全面改进的工具,以支持先进节点签核。这些工具全部相互集成,包括:Quantus™ Extraction Solution;Liberate™ Characterization 产品组合,用于针对特征提取、差异建模、基础 IP 验证提供稳健的解决方案,适用范围广泛,从标准单元、I/O,复杂的多位单元,到存储器和混合信号区块;Tempus™ Timing Signoff Solution,用于签核静态时序和分析;Voltus™ IC Power Integrity Solution和Pegasus™ Verification System,用于大规模并行物理签核和 DRC、LVS 以及 DFM。

这些先进的签核工具与 Cadence 综合和实现工具集完全集成,使设计人员可以在整个设计过程中使用一套集成的工具流程。

总之,Cadence 的先进节点数字实现解决方案采用了大规模并行化技术,具有共享的引擎基础设施和设计同步签核功能,为在先进节点上使用 FinFET 或 FD-SOI 技术设计突破性产品提供了独特而全面的解决方案。

-

相关产品

- Innovus Implementation System<sub></sub>

- Quantus Extraction Solution

- Tempus Timing Solution

- Voltus IC Power Integrity Solution

- Physical Verification System

- Genus Synthesis Solution

- Liberate Trio Characterization Suite

- Liberate MX Memory Characterization

- Liberate AMS Mixed-Signal Characterization

- Liberate LV Library Validation Solution

- Liberate Variety Statistical Characterization

- Spectre Accelerated Parallel Simulator

- Spectre eXtensive Partitioning Simulator (XPS)

-

Cadence 扩充系统 IP 产品组合,推出 NoC 以优化电子系统连接性 06/25/2024