面向 Arm AMBA 协议的 Verification IP

经过验证的全面解决方案可满足广泛的系统级芯片验证需求

Key Benefits

- 全面的解决方案可改善系统级芯片质量和性能

- 可靠的结果有助于实现可预测的验证计划

- 易于使用的一致性产品可提高生产率

在系统级芯片 (SoC) 功能验证方面,最耗时的一个环节是创建可准确激发和及时响应待验证设计接口的测试平台。典型的系统级芯片通常包含数十个标准接口和多层互连结构,因此,Verification IP (VIP) 在建模过程中将所有这些接口变成可插入测试平台并与待验证设计一起进行仿真的组件,从而带来巨大的优势。这样可以大大减少验证工程师的工作量,节省时间并提高产品质量。

性能验证

如今,许多系统级芯片使用复杂的互连结构 IP 来连接多个处理器内核、高速缓存、存储器以及许多其他 IP 模块。这些互连结构使新一代低功耗服务器和高性能移动设备成为可能。然而,这些互连结构更加复杂,需要使用 VIP 解决方案来验证数据完整性、系统级芯片性能和协议合规性。

面向 Arm® AMBA® 协议的 Cadence® Verification IP 是全面的系统级芯片验证解决方案,使用:

- 仿真 VIP 和基于断言的 VIP 进行协议合规性验证

- Interconnect Validator 进行数据完整性分析

- Interconnect Workbench 进行性能验证

- Indago Protocol Debug App 进行简化调试

- Accelerated VIP 进行硬件/软件验证

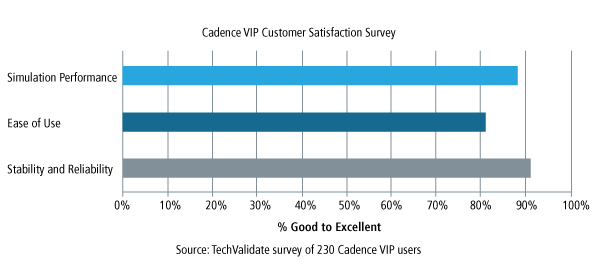

备受客户青睐

十多年来,面向 AMBA 协议的 Cadence VIP 一直在不断发展和改进。大量客户已使用 Cadence VIP 验证了数千种基于 AMBA 的设计。

博客 VIEW ALL