Cadence® Joules™ RTL Design Studio 协助RTL 设计人员更迅速更准确的获取功耗、性能、面积和拥塞 (PPAC) 这类会影响物理实现的指标。前端设计人员可以定位问题在版图中的位置,追查对应的源代码,通过这些自动化的引导,提升RTL质量以实现更好的 PPAC 。同时,这种在早期对设计调整处理的方式,有助于实现工程师合理分配资源,解决在 RTL 层面无法修复的问题。

概述

Cadence® Joules™ RTL Design Studio 协助RTL 设计人员更迅速更准确的获取功耗、性能、面积和拥塞 (PPAC) 这类会影响物理实现的指标。前端设计人员可以定位问题在版图中的位置,追查对应的源代码,通过这些自动化的引导,提升RTL质量以实现更好的 PPAC 。同时,这种在早期对设计调整处理的方式,有助于实现工程师合理分配资源,解决在 RTL 层面无法修复的问题。

过去,RTL 工程师与实现工程师各自独立,导致前端和实现过程的脱节。这一脱节也致使前后端团队间存在冗余迭代,增加了设计周期,同时也严重影响了产品上市时间。在将设计交付到物理实现前,应该解决主要的时序和拥塞问题。如果在设计早期就有足够准确的预估和智能的调试手段,那么在 RTL 编码和架构1阶段就能解决 20%-40% 的物理实现问题。

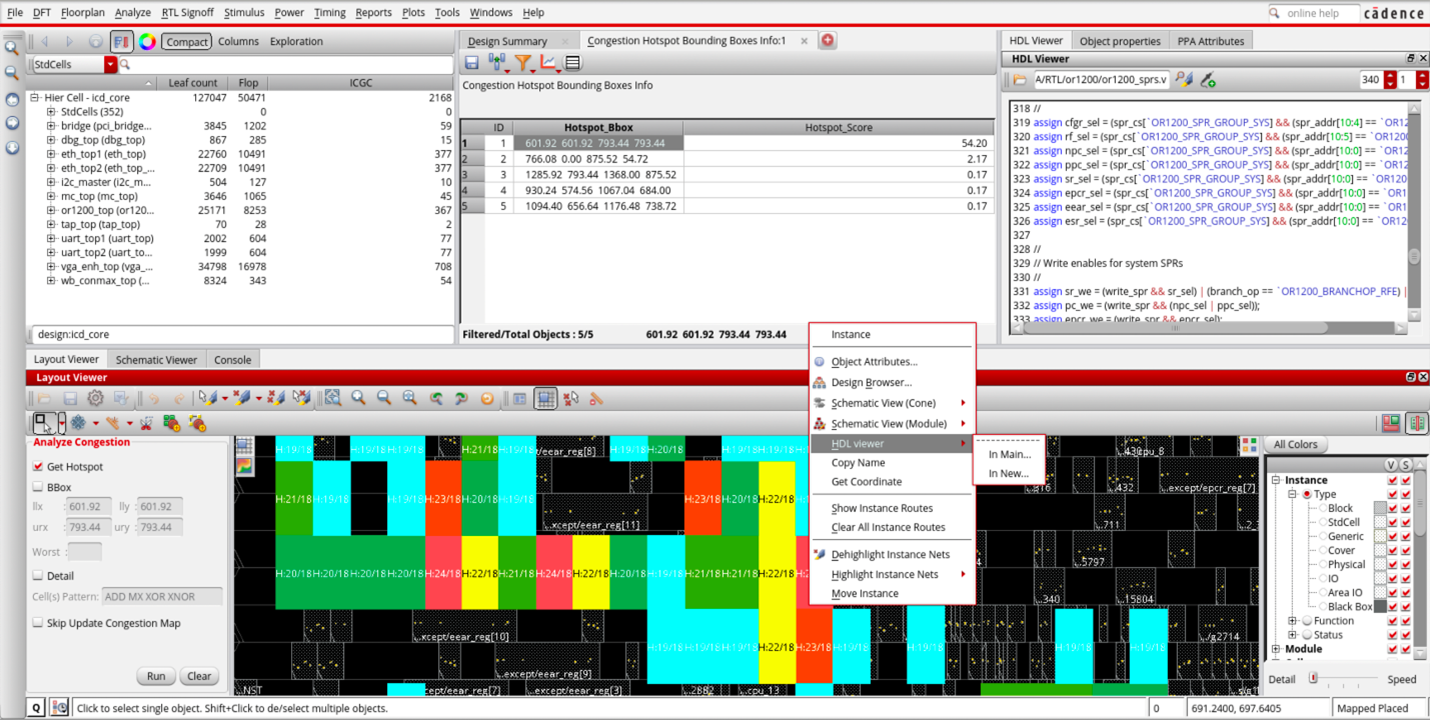

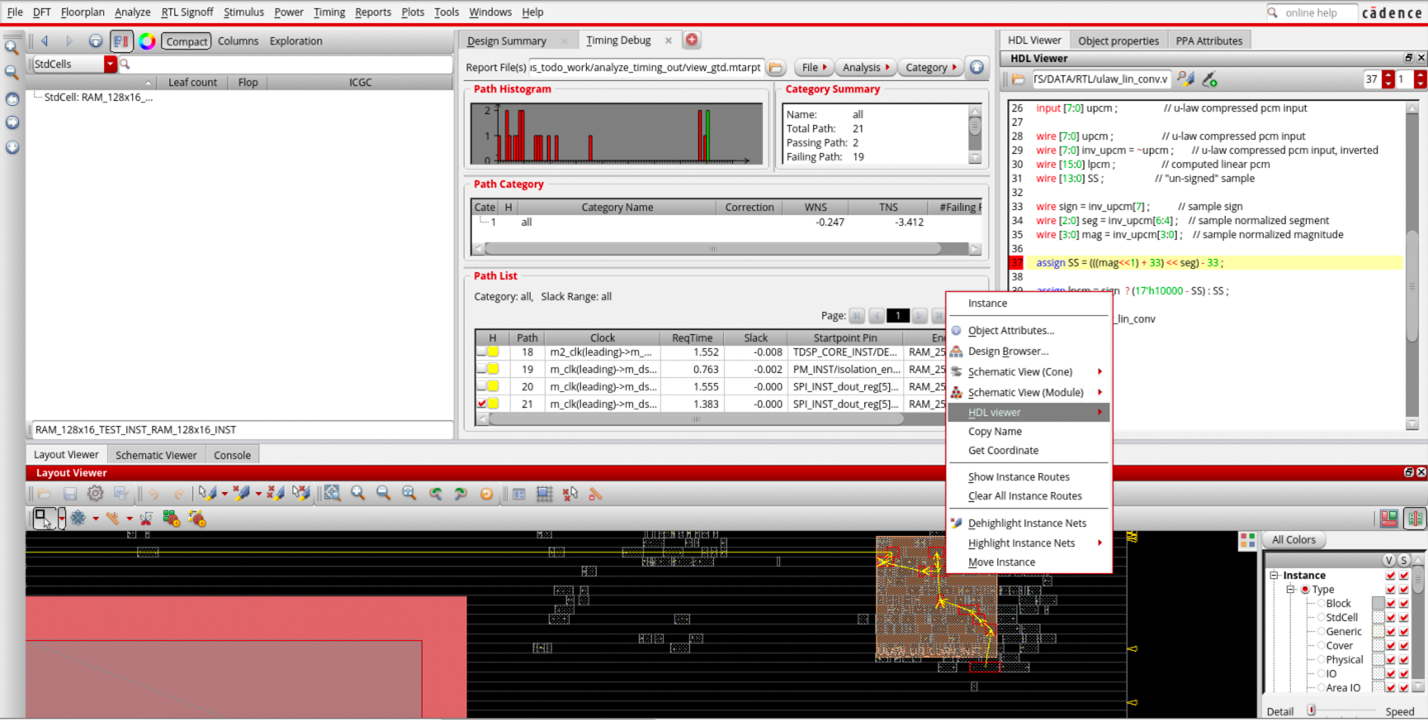

Joules RTL Design Studio 协助前端设计人员全面优化代码,确保代码交付质量,实现 PPAC 目标。该解决方案使用 Cadence 的核心引擎来计算 PPAC预估值 ,包括业界优异的的Innovus™ Implementation System、Genus™ Synthesis Solution 和 Joules RTL Power Solution,高准确度让用户有足够把握做出决定。Joules RTL Design Studio 搭载了独特的智能调试辅助系统。这一系统对违例的可能原因进行归类,提供建议协助设计者发现解决 RTL 问题,最终打造出更智能、更高效的产品。

Joules RTL Design Studio 与生成式 AI 解决方案——Cadence Cerebrus™ Intelligent Chip Explorer 紧密集成,便于探索不同的设计场景,如布局优化,频率电压考量。此外,它还与 Cadence Joint Enterprise Data and AI Platform 集成,有助于和不同版本 RTL 或前代项目比对,进行深入分析。

操作系统平台支持

Joules RTL Design Studio 支持:

Cadence服务与支持

参考文献

- Vanderlip, Jeff."Physical RTL optimization solves problems early."EETimes DesignLines.November 15, 2002.