Power-Aware Verification Methodology

最大程度减少后期错误,缩短调试周期

Key Benefits

- 验证功耗优化设计

- 确保功耗管理特性不违反设计意图

- 通过完全集成化的流程,全方位验证您的系统级芯片(SoC)

功耗优化技术正在为电子设计的物理和功能行为带来新的复杂性。Cadence 的兼顾电源影响的验证方法(power-aware verification methodology)是功能验证计划不可或缺的一部分,它有助于验证功耗优化而不会影响设计意图,从而最大程度地减少后期错误,缩短调试周期。毕竟,在不考虑功耗意图的情况下进行仿真,就像使用“黑匣子”里的 RTL 代码进行仿真一样。

此方法将兼顾电源影响的分析(power-aware elaboration)与形式化分析和仿真相结合。通过兼顾电源影响的分析(power-aware elaboration),设计中的所有区块以及功耗管理特性皆可部署到位,以便通过电源意图验证设计。功耗意图可以引入电源/接地网络、电压电平、电源开关、隔离单元和状态保持寄存器。任何验证技术(模拟、仿真、原型设计或形式化验证)都可以应用于兼顾电源影响的分析(power-aware elaboration)。

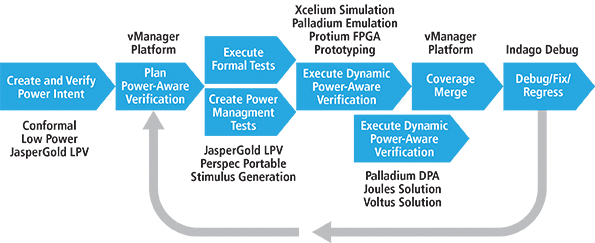

通过前期时间和精力投入,学习和应用此流程中的工具,可以避免在后期花费更长的时间来查找和修复设计问题。图 1 概述了功耗感知验证方法的关键步骤。

Power-Aware的流程步骤

步骤 0:写入并擦除 CPF/UPF 功耗意图

- 可以使用 Cadence® Conformal® Equivalence Checker 筛选预仿真功耗意图,在无需使用测试向量的情况下,对百万门级设计进行形式化验证和调试

- 确保可以使用 Cadence JasperGold® Low-Power Verification 应用对功耗意图进行验证,该应用可以使用静态和动态电源优化技术详尽地验证设计功能

步骤 1:创建兼顾电源影响的和具备功耗特性验证的计划

- 通过功耗功能和验证方法组织测试;利用 Cadence vManager™ Metric-Driven Signoff Platform 规范化计划和管理流程

- 区分区块(block)级别和系统级芯片(SoC)级别,在区块(block)级别进行尽可能多的测试

- 选择一个平台来验证每个条目;使用静态/形式化引擎来覆盖尽可能多的测试计划,以避免动态测试覆盖率不完整带来的风险

步骤 2:使用 JasperGold Low Power Verification 应用来执行验证计划中的形式化验证部分,该应用将自动为以下过程创建兼顾电源影响的 RTL:

- 兼顾电源影响的属性检查

- 使用 SEC 进行功耗优化

- 检查由功耗意图引入的新 X 源

- 详尽验证电源启动和断开的序列

步骤 3:为均衡验证计划创建动态测试

- 将所有验证测试转变为兼顾电源影响的验证测试

- 生成可跨验证引擎、可移植的测试和检查

- Cadence Perspec™ System Verifier 作为可移植激励生成器,可用于验证功耗管理功能

步骤 4:在指定的引擎上执行动态测试。针对每一种类型的测试选用效果最佳的引擎。例如:

- Cadence Xcelium™ Parallel Logic Simulation 用于验证是否正确实现了 Common Power Format (CPF) 或 Unified Power Format (UPF) 文件中所述的功耗意图,包括:

- 逻辑网表电源域复位、初始化和控制行为

- 物理网表,包含布局和布线后期缓冲以及时钟网络

- IP 接口和电源域在系统级芯片(SoC)级别的交互

- 测试如 BIST 和扫描链这样无等效 RTL 的结构(

- Cadence Palladium Z1 适用于较长或“深度”的测试,例如硬件/软件集成和软件电源状态控制

- Cadence Protium™ S1 FPGA-Based Prototyping Platform 是为软件开发人员提供的宝贵工具,可用于验证功耗控制和应用软件是否能够按预期协同工作

步骤 5:合并覆盖率指标报告,使用 vManager Metric-Driven Signoff Platform 查看、报告和管理覆盖率

步骤 6:正常的调试/修复/回归周期。如果功耗意图有所更改,需重复所有测试。根据设计和实施团队对功耗意图进行的更改,自动触发回归分析

-

Cadence 扩充系统 IP 产品组合,推出 NoC 以优化电子系统连接性 06/25/2024