Key Benefits

- 10X productivity creating SoC tests for complex system scenario verification

- Correct-by-construction generation of complex concurrent multi-core/multi-threaded tests

- Verify more corner cases with automatic use-case amplification of state space and timing exploration on the fastest verification engines

- Easy portability of test intent and test suite to derivative projects

- Supports Accellera Portable Test and Stimulus Specification (PSS)

- Downloadable PSS Methodology and Library: Includes documentation of the library, PSS best practices, and practical examples, plus the PSS source for the library. Request Download

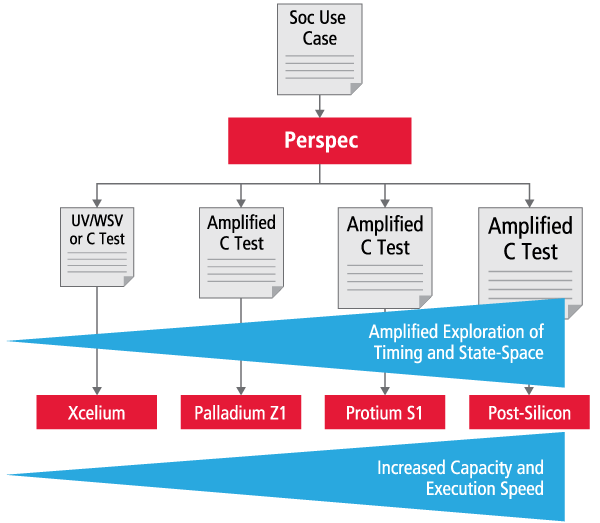

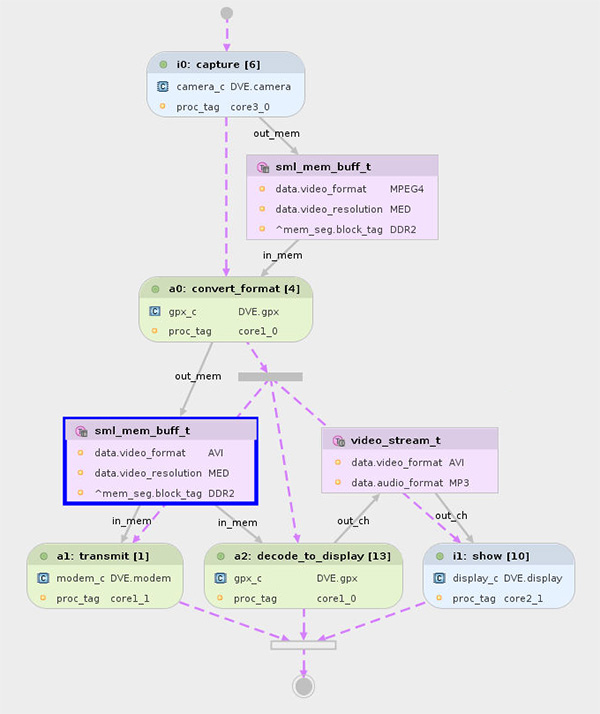

Frustrated by all of the manual effort and time you’re spending developing complex system-level coverage-driven tests to verify your system on a chip (SoC)? Cadence® Perspec™ System Verifier automates this entire process, reducing complex use-case scenario development from weeks to just days. Compared to manual test development, you’ll be able to generate 10X more tests 10X faster using this platform solution. In addition, with its integrated debugging capability, you’ll be equipped to reproduce, find, and fix complex SoC-level bugs in order to improve the overall quality of your SoC.

By applying an appropriate level of abstraction, the Perspec System Verifier can meet the growing challenges of validating SoC performance, function, and power.

The platform is portable, supporting reuse across:

- SoC scope, from IP to the system level, including hardware-aware software

- Domain experts create the model and describe scenarios, enabling verification and validation engineers to create system-wide tests

- Generated tests run out of the box on all Cadence verification engines

Using the Perspec System Verifier, you'll benefit from completeness of measurement, with coverage of functionality, flows, and dependencies. You'll also gain knowledge transfer advantages, since the formal, model-based system description supports knowledge sharing between different groups, particularly hardware and software engineers.

Key Features

- Downloadable PSS Methodology and Library: includes documentation of the library, PSS best practices, and practical examples, plus the PSS source for the library. Request Download

- Goal-directed and true constraint solving

- Multi-platform, multi-language solution leveraging existing standards and proven techniques

- Automatic use-case amplification of state space and timing exploration on fast verification engines

- Connect portable stimulus to UVM testbenches for IP and subsystem verification and stimulus portability

- Coverage and automatic filling capabilities

- Debug and coverage logging built into the generated C tests to speed both debug and analysis of coverage results

Customer Testimonials

NOTE: A Cadence account is required to access the presentation files.

- Using PSS: An Automotive Case Study by Infineon Technologies

- SoC Power Management Test Scenarios with Portable Stimulus by AMD

- PSS in Real Life by Texas Instruments

- Enable Complex CPU System’s Coverage Closure by SW-Driven Stimulus with Structural Coverage Beyond Accelerated Emulator by MediaTek

- Automated Test Generation to Verify CPU Subsystem for System Level Low Power Management by Perspec by MediaTek

- Make Stimuli Portable by Using Perspec System Verifier by Texas Instruments

- Cadence Perspec System Verifier Usage at Sub-System/SoC/Silicon Level for Infineon Aurix Microcontrollers by Infineon

- Cadence Perspec System Verifier on a Real SoC Verification of a MSP430 Mixed-Signal Microcontroller by Texas Instruments

- Enabling Verification of Complex System Scenarios Using Perspec System Verifier by STMicroelectronics

- Automated Test Generation to Verify IP Modified for System Level Power Management by STMicroelectronics

- Renesas Accelerates IoT Design Using the Cadence Perspec System Verifier by Renesas

We found that the Perspec technology easily detected issues caused by complex combinations of power mode settings and transitions. The technology can help us dramatically improve productivity and deliver our designs to IoT application developers much faster.

Toshinori Inoshita, Renesas

With the Perspec approach we get a lot of interesting scenarios “for free” which are difficult to achieve in a directed test. … In case of failures, the scenario viewer helps to understand the intended execution flow.

Thorsten Klose, Infineon

[It was] easy to generate complex scenarios using [Perspec] Composer drag and drop composition and scenario completion. [The] graphical scenario representation enables collaboration.

Smitha Kaginele and Murthy Hari, Microsemi

This [Perspec] flow facilitates [absorption of] late design changes rapidly due to automation in the testbench and test case generation.

Vivek Goyal and Vijay Rajan Machingauth, Samsung

[Perspec] Verification Engineer increased confidence in power sequence support. [This] methodology could be applied to any low-power (LP) verification.

Christophe Lamard, STMicroelectronics

[Perspec] system model changes can easily regenerate all test cases. Generated stimulus code is very well readable based on templates with the same look and feel as traditional stimuli.

Frank Donner, Texas Instruments

Perspec improves RTL regression efficiency and quality, ...[and] enables software/hardware co-verification.

Hsuan-Ming Chou, Osmond Yao, and Dennis Hsu, MediaTek

Training and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.

Find Answers in cadence technical forums