Power-Aware Signal Integrity Analysis

Complete DDR, LPDDR, and GDDR power-aware SI solution

Key Benefits

- Allows concurrent simulation of reflection, loss, crosstalk, and SSO effects

- Provides power-aware transistor-to-behavioral I/O model creation

- Features comprehensive JEDEC-based post-processing of waveforms for measurements

What is power-aware signal integrity analysis? Some tools stop at only supporting power-aware I/O modeling standards, but not Cadence® Sigrity™ technology. We can help you meet your requirements for:

- Accurate extraction of coupled signal, power, and ground across chip, package, and PCB

- Creating and reading power-aware IBIS models

- JEDEC’s specifications for the latest memory interfaces and bit-error rates (BERs)

Convert Transistor-Level Models to Power-Aware IBIS Models

Sigrity Transistor-to-Behavioral Model Conversion (T2B™) converts IBIS models from transistor to behavioral, enabling accurate and efficient power-aware bus simulations in hours instead of the days it would take with transistor-level models.

Accurately Model Signals on the IC Redistribution Layer Coupled to IC Power and Ground

Sigrity XcitePI™ Extraction for chip-level extraction of signal power and ground interconnect from the I/O to the bump with header information enabling push button connectivity to the extracted package model.

Full Package Modeling Using a Blend of Full-Wave 3D and Hybrid Solver Technology

Sigrity XtractIM™ technology and 3D-EM technology work together to create a complete package model regardless of package type, for coupled signal, power, and ground interconnect models. Also included is package assessment, bridging the gap between the package designer and package characterization engineer.

Get Fast, Accurate Electrical Modeling of PCBs

Sigrity PowerSI™ technology extracts coupled signal, power, and ground from PCBs. Included in the extracted model is header information enabling push-button connectivity to the extracted package model(s) and/or connector model(s).

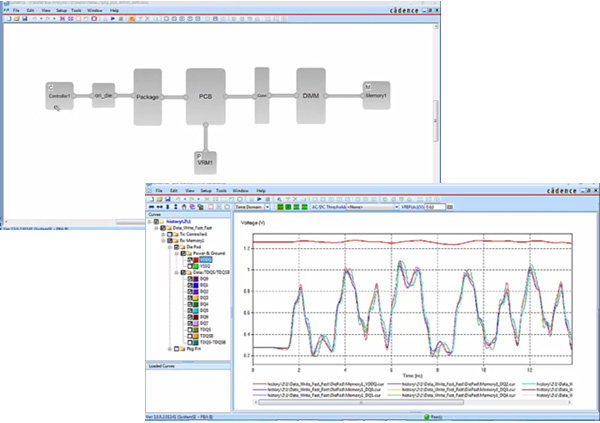

Explore and Validate DDR and LPDDR Interfaces Quickly

Sigrity SystemSI™ technology provides easy connectivity of power-aware IBIS models and power-aware interconnect models. Simulation results exhaustively determine worst-case conditions and compares those results to JEDEC compliance requirements, allowing you to sign off your DDR4 interface including BER requirements.

Features

- Easy-to-use block-level schematic environment

- Hybrid solver for efficient S-parameter extraction of large interconnect structures

- 3D full-wave solver for detailed extraction of high-frequency structures

- S-parameter tuning, checking, and broadband SPICE model conversion

Additional Resources:

培训 & 支持