RC抽出ツールQuantusのもう一つの機能 ~ 基板ノイズ解析

半導体回路の設計では、レイアウトから寄生RCの抽出を行い、Spectre®等の回路シミュレータを用いて回路が正常に動作するか確認を行うことが必要不可欠です。正しいシミュレーション結果を得るためには、高精度なRC抽出ツールが必要で、ケイデンスでは、Cadence® Quantus™ Extraction Solution(以下Quantus)を提供してこの要求に答えています。さらにQuantusには、回路のRCを抽出する機能以外にも、もう一つユニークな機能として、Substrate Noise Analysis / Surface Noise Distribution Analysis (SNA/SND)という基板ノイズ解析が組み込まれています。

SerDes等の高周波回路による基板ノイズのアナログ回路等への影響は大きく、設計での対策が重要になっています。今回は、その対策を検討する上で重要な基板ノイズ解析としてのQuantusの機能について紹介させていただきます。

Substrate Noise Analysis Flow

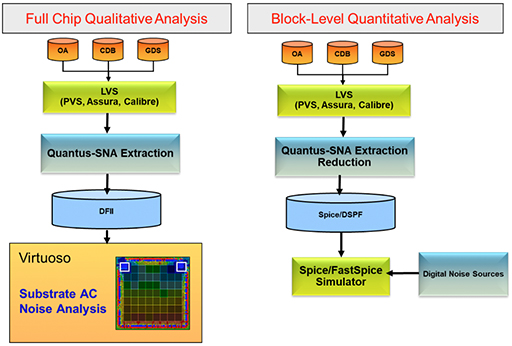

図1:基板ノイズ解析フロー

図1が基板ノイズ解析フローになりますが、基本的に通常のXtorレベルのQuantusのフローと同じで(Cellレベルでは使えません)、LVSを通して作られたデータから抽出を行い、Virtuoso®上で表示可能なExtracted_View (DFⅡ)か、各種回路シミュレータに適用可能なSPICE/DSPFネットリストを作成します。なお、基板を抽出したネットはサイズによってはSpectre等回路シミュレータでは扱えないほど大きくなることもありますが、その場合にはExtracted_Viewを使うことで、Virtuoso上での簡易解析による基板ノイズのカラーマップ表示を行うことができます。

Substrate Extraction

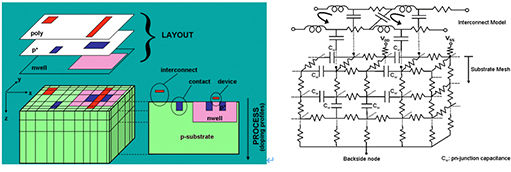

図2:基板の3D-RCメッシュ

Quantusでは回路動作の確認のためには、デバイスとその上位の配線層を抽出しますが、基板ノイズ解析用にはデバイスの下のsubstrate層を、深さも考慮した3D構造のRCメッシュ構造として出力します。配線層と同時に抽出することもできますし、基板のみの抽出も可能です。また周波数を考慮したRCの縮退機能を持っており、大きくなりがちな基板の3D RCメッシュをコンパクト化することも可能です。ただし基板の抽出には通常の抽出用のライブラリ(qrcTechFile)とは別に基板抽出用のライブラリが必要になります。

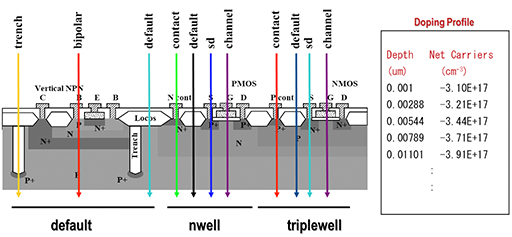

図3:Doping Profile

3D構造の抽出を行うために、各デバイスの構造毎に深さに対するプロセス情報が必要となり、これに関してはチップの製造元に要求して入手していただく必要があります。

Surface Noise Distribution Analysis (SND)

SPICEネットを出力することで、回路シミュレータを使った詳細な解析が可能になりますが、Extracted_Viewを出力することで、あくまで簡易的な解析にはなりますが、視覚的にノイズの伝搬を判断するためのカラーマップを表示することも出来ます。

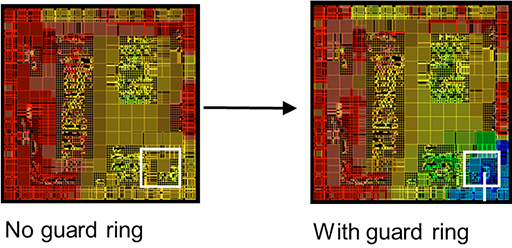

図4:What-If解析

図4は、カラーマップの表示例ですが、このようにガードリングの有り無しでのWhat-If解析を行い、ノイズ削減効果を視覚的に判断することが可能です。

図5:深さによるノイズの変化

また3D構造で抽出していますので、深さを考慮したノイズを確認することもできます。図5は、同じノイズ解析で、異なる深さでのノイズ伝番の様子を表示したものです。Zが深さを表しており、深くなるとノイズがのっていないことがわかります。これによって、ガードリングの下からのノイズの回りこみ量なども確認することが可能です。

まとめ

以上、ご紹介してきましたように、Quantusは回路の寄生素子抽出だけでなく、基板の3D-RC抽出、さらには簡易的な基板ノイズ解析によるカラーマップ表示、それによってWhat/If分析も可能にするなど、他社にはないユニークな特徴をもったソリューションを提供しています。基板ノイズの対策は今後も重要な課題ですので、Quantusのソリューションをご活用いただければと思います。

フィールドエンジニアリング&サービス本部

デジタル&サインオフ テクニカルリーダー

堀越 賢剛

Latest Issue

- 新製品Fidelity CFD : CFDの可能性を解き放つ

- Quantus FS (Field Solver) 最新機能のご紹介

- Cadence Online Support (COS) サイトで字幕付きのビデオがリリースされました。

- Cadence Topics: CadenceLIVE Japan 2022開催!

- チップレット活用の時代へ向けたケイデンスIntegrity 3D-ICプラットフォーム

- 革新的なマシンラーニングベースの設計システム製品Cerebrus Intelligent Chip Explorer

- 自動運転シミュレーションができる車載向けエッジAIの自動ハードウェア設計・検証環境

- Cadence AWR Design Environmentの進歩

- PCBデザイン管理環境Allegro Pulseを利用することで本領発揮するAllegro System Capture

- Allegro In-Design AnalysisにSigrity PowerSI/Clarity 3D Solverを統合

- サインオフDRC/LVS/FILLをインプリ全体で適用し圧倒的な設計期間短縮を可能にするPegasus Signoff Verify Design Flowの紹介

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues