PCBデザイン管理環境Allegro Pulseを利用することで本領発揮するAllegro System Capture

Allegro®/OrCAD® 17.4-2019で初登場したPCBデザイン管理環境のAllegro Pulseは、従来のライブラリ管理環境Allegro EDMと統合されているため、Allegro EDMのバージョンアップとしてもご利用が可能ですが、論理設計環境であるAllegro System CaptureをこのPulseサーバーに接続することでより効果を発揮します。

今日は、Allegro Pulseのサーバーに接続した、Allegro System Captureで、どのような利点があるかを中心に、ご紹介させて頂きます。

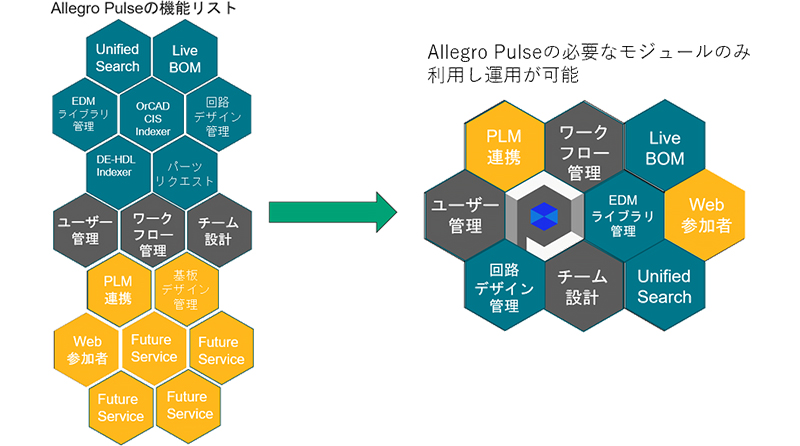

Allegro Pulseは、モジュラーアーキテクチャーを導入しており、顧客に必要なソリューション・機能を段階的に追加し、運用が可能です。

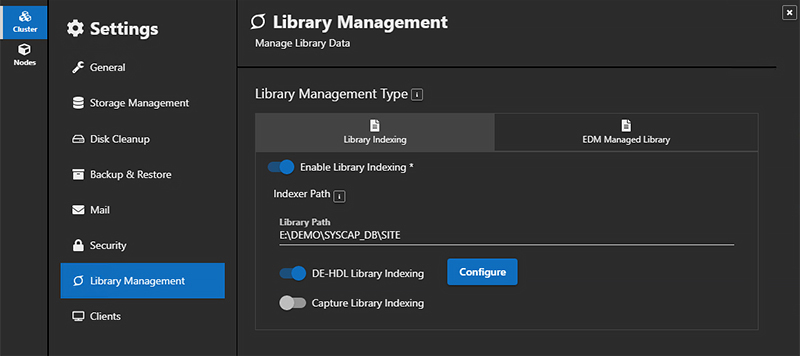

Allegro Pulseにとって、Allegro EDMは、モジュールの1つに過ぎないため、Allegro EDMでライブラリ管理が必須という訳ではありません。 Allegro System Captureは、お客様がお使いのAllegro Design Entry HDLやOrCAD Capture CISの既存ライブラリを参照することができますので、Pulseサーバーに接続した場合でも、既存ライブラリをそのままご利用頂けます。

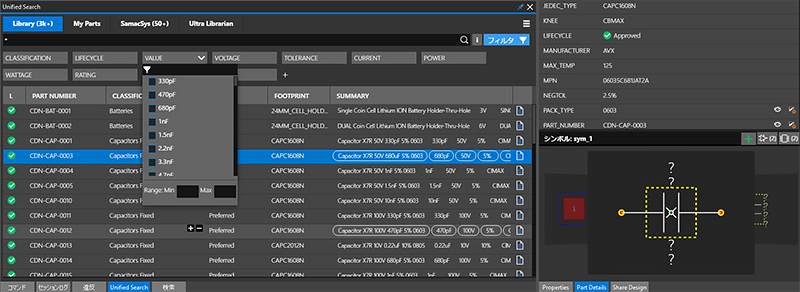

一つ目の利点は、ライブラリ検索の強化です。回路設計者の皆様は、ライブラリ検索のスピードに満足していますでしょうか?

Allegro System Captureは、ライブラリ検索を高速化するIndexデータを生成できますが、Pulseサーバーをご利用頂ければ、サーバーが自動的にこれらの処理を行ってくれます。

また、Allegro System Captureは、通常フリーテキスト検索で部品を検索しますが、EDMでライブラリ管理をしている場合、ブール演算子と範囲演算子や、ライブラリデータに基づいたフィルタリング機能を使った検索が行えます。

Unified Search参考記事:

ASCENT: Unified Searchを使って最適な部品を見つける

ASCENT: Ready-GOで設計スタート! ライブラリの用意がなくても大丈夫

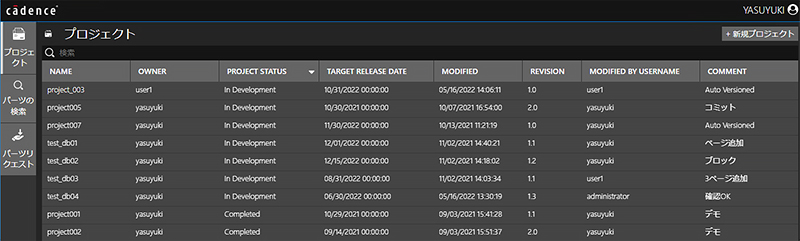

2つ目は、Allegro PulseでのSystem Captureプロジェクトの管理です。

プロジェクトのバージョン管理は万全でしょうか?

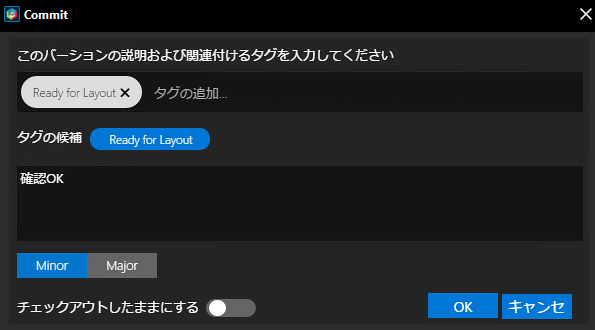

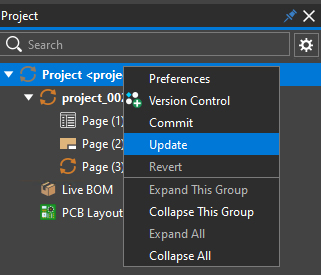

Pulseサーバーに接続したAllegro System Captureは、Commitコマンドを行うことで、確実にPulseサーバーに格納され、バージョン管理されます。

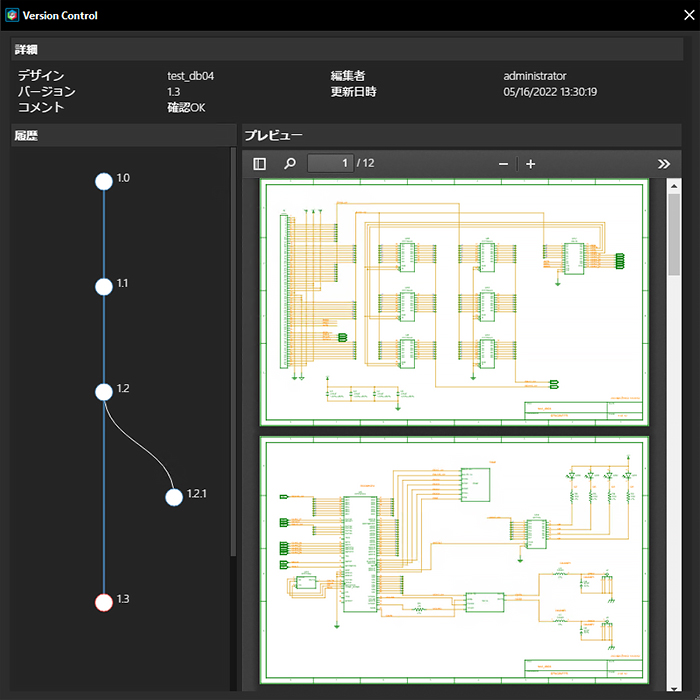

Allegro System CaptureのVersion Controlコマンドで、通常のSaveやCommitコマンドでの変更履歴をCommit時のコメントと合わせ視覚的に確認ができます。

また、必要に応じ、過去のバージョンを開いて、再編集や、別プロジェクトとして保存することも可能です。

3つ目は、強力かつ簡単なチーム設計です。

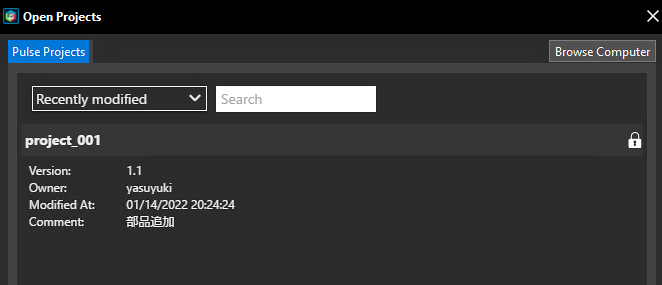

Pulseサーバーにプロジェクトデータが保存されることにより、ベーシックなチーム設計(Follow-the-Sun Team Design)が可能になり、他の設計者とプロジェクト単位で排他制御が可能となります。

白色の鍵マークが出ているプロジェクトは、他ユーザーが編集中です。

鍵マークが出ていた場合でもREAD ONLYマークが表示され、その回路図を参照することができます。

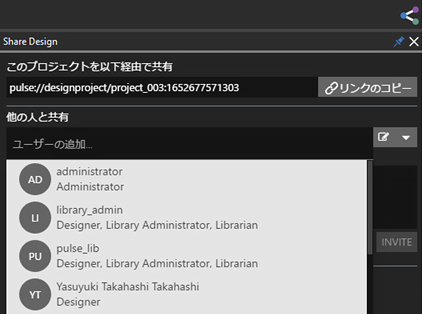

更に、Team Collaboration用ライセンスを追加して頂くと、1つのプロジェクトに対してページやブロック単位でチーム設計を可能にするAdhoc Team Design機能が有効になります。 System Captureの画面右上のShareアイコンから簡単にチームメンバーのアサインが可能です。

チームに招待、アサインされるとメールにて通知が届くシステムになっています。

設計者がCommitコマンドを実行することにより、担当のページ、ブロックがPulseサーバーに格納され、他の設計者が更新された回路図を取得できます。

Adhoc Team Design参考記事:

ASCENT: Allegro System Captureでのチームコラボレーション

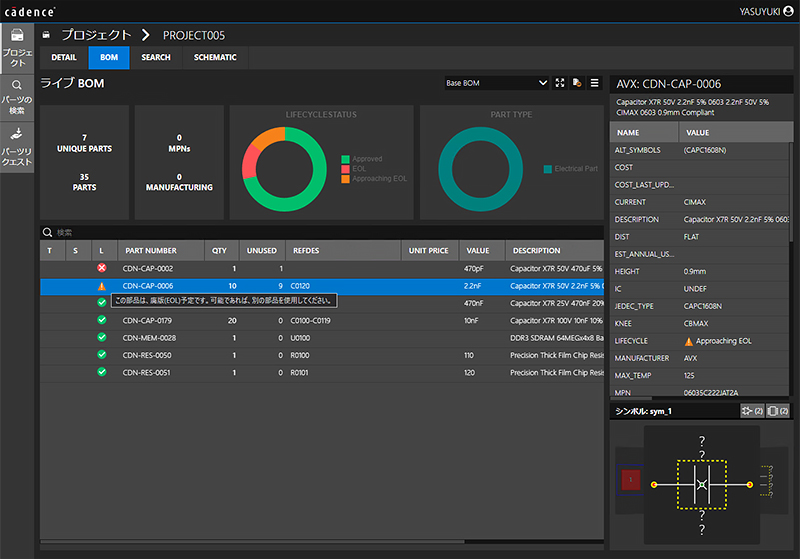

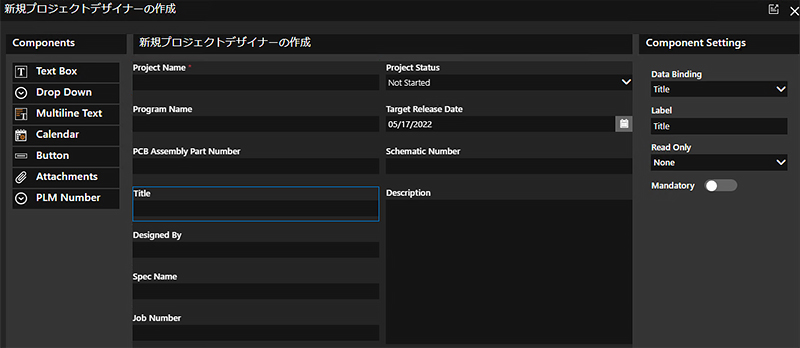

4つ目は、管理者を含めた非CADユーザーの方も利用可能な、Webブラウザからプロジェクト作成・表示、BOM作成・表示、前述のVersion Control情報などが閲覧できるWebダッシュボード機能です。

プロジェクトのリスト表示では、任意の属性表示が可能で、現在のプロジェクトステータスや締め切り日時などの情報が確認できます。

BOMは、Live BOMというAllegro System Captureと共通の次世代BOMを採用しています。予定数量の定義も行え、回路図での未配置分も含めBOM情報の把握が行えます。

EDMご利用時には、ライブラリ検索の結果を直接Live BOMに登録し、日々変更になる廃番や推奨部品などのライフサイクル情報も含めることが可能です。

QIR4からは、チーム設計のメンバーアサインも可能になりました。

Allegro Design Entry HDLのCUSTOM TEXTは、Allegro System Captureでもサポートされますが、管理者がカスタマイズ可能なフォームにCUSTOM TEXT名を定義しておくことで、CUSTOM TEXT値をPulseサーバーで入力、閲覧できます。

Webダッシュボード参考記事:

ASCENT: ブラウザベースのダッシュボードからSystem Captureの機能にアクセスする

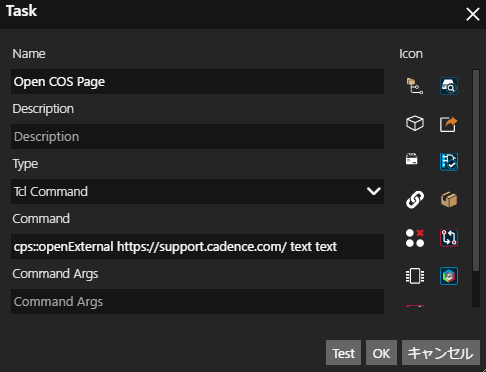

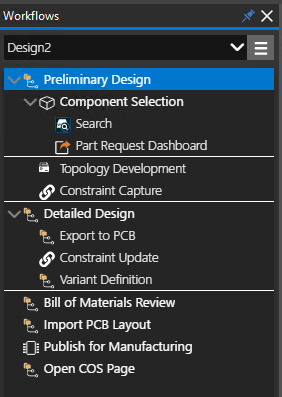

5つ目は、Allegro System Captureのワークフロー管理です。

設計者の皆様は、作業フローは他の設計者と共通化されていますでしょうか?

Allegro Pulse が管理するAllegro System Captureのワークフローは、Allegro System CaptureがサポートするTCLコマンドの他に、システムのコマンドもサポートしており、外部のWebページを表示したり、batファイルや作成したTCLプロシージャを実行したりできます。OSで関連付けられているアプリケーションで開くことができるTCLコマンドも用意しているため、簡単にオリジナルの作業フロー構築が可能です。

Allegro System Capture自体も直感的に操作できるGUIになっていますが、このワークフローを活用することで、新しくツールを覚えるという負担が更に軽減されます。

カスタマイズしたワークフローは、Pulseサーバーで管理されているため、設計者が同じワークフローを利用することができます。

Workflow参考記事:

ASCENT: Allegro System Captureのワークフロー

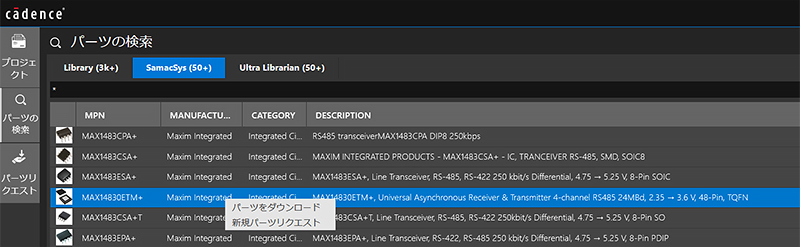

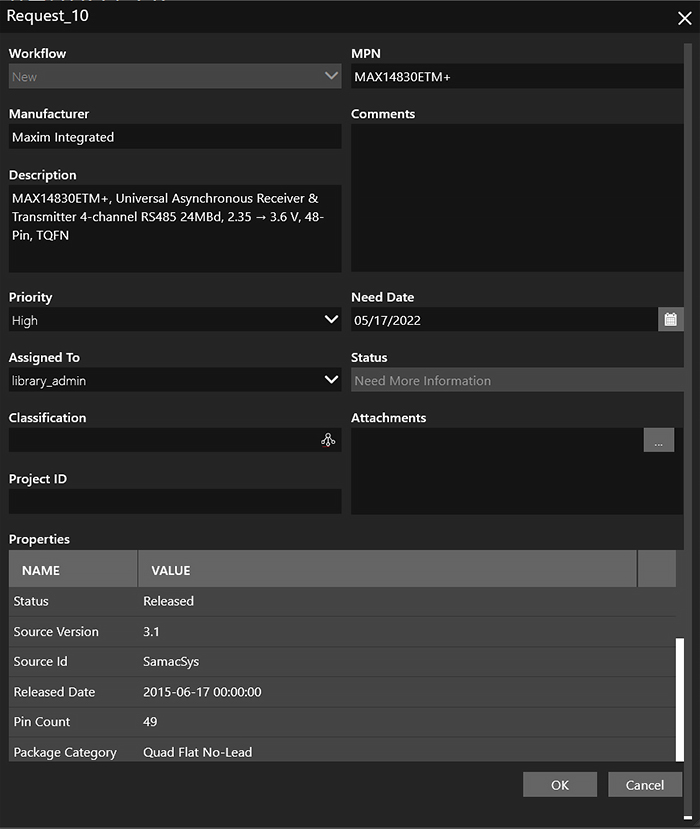

6つ目が、EDMでライブラリ管理を行っている場合の新規部品リクエスト機能です。

回路設計者が、ライブラリ作成者に、部品作成を依頼する際、Allegro PulseとAllegro System Captureを利用することでこのやりとりをシステム化します。

新規部品はもちろん、既存部品や、コンテンツプロバイダーの提供する部品を流用して部品作成依頼が可能です。

回路設計者は、カスタマイズ可能なリクエストフォームで申請を行います。

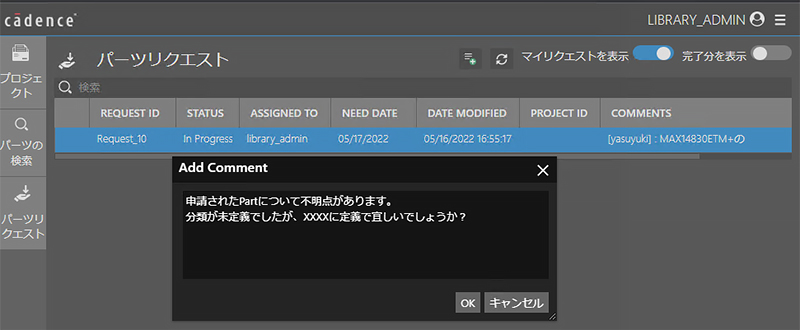

パーツリクエストダッシュボードでは、現在申請中の部品作成依頼がリストされ、ここでライブラリ作成者のアサインや、部品作成においての不明点があった場合、回路設計者とライブラリ作成者の間でメッセージのやり取りを行います。

このパーツリクエストから、ライブラリ作成者が使うEDMのDatabase Editorへ情報が引き継がれ、部品作成、配布後に、完了ステータスになるという仕組みになっています。

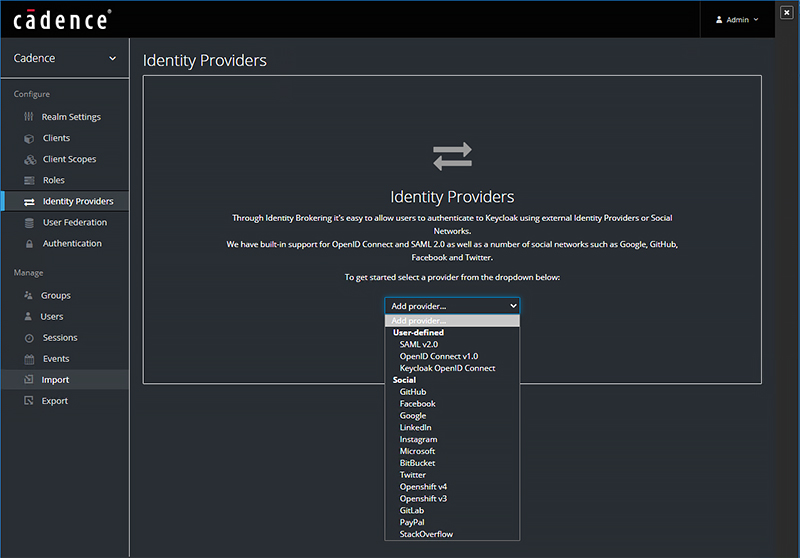

ここまでに紹介したPulseサーバーに接続するAllegro System Captureの利用には、Allegro Pulseでのユーザー管理が前提となりますが、Keycloakと呼ばれるエンタープライズグレードのオープンソースID管理ソリューションを採用しているため、SSOやLDAPを使ったユーザー管理が可能です。

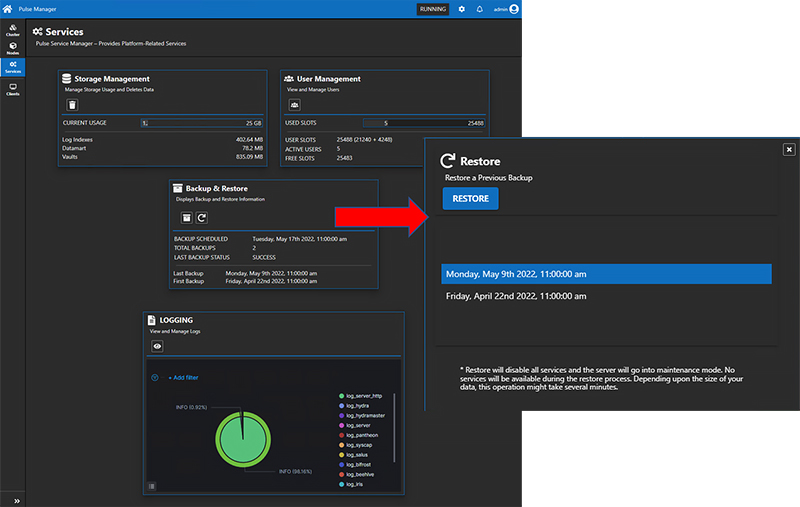

また、Pulseサーバーのデータのバックアップは、定期的に実行できるように設定が可能で、ロールバック機能も有しています。

如何でしたでしょうか?

Allegro Pulseはモジュラーアーキテクチャーを採用しているため、今日紹介した全機能を最初から利用する必要はなく、一つずつ機能を導入していくことが可能です。

Allegro System Captureのトッピングに一つ加えてみては如何でしょうか?

今回、ご紹介の内容に関しましてお問い合わせがございましたら、貴社担当営業、あるいはメール: [email protected]へご連絡ください。

フィールドエンジニアリング&サービス本部

カスタムIC&シミュレーション&SPB

高橋 泰之

Latest Issue

- 新製品Fidelity CFD : CFDの可能性を解き放つ

- Quantus FS (Field Solver) 最新機能のご紹介

- Cadence Online Support (COS) サイトで字幕付きのビデオがリリースされました。

- Cadence Topics: CadenceLIVE Japan 2022開催!

- チップレット活用の時代へ向けたケイデンスIntegrity 3D-ICプラットフォーム

- 革新的なマシンラーニングベースの設計システム製品Cerebrus Intelligent Chip Explorer

- 自動運転シミュレーションができる車載向けエッジAIの自動ハードウェア設計・検証環境

- Cadence AWR Design Environmentの進歩

- Allegro In-Design AnalysisにSigrity PowerSI/Clarity 3D Solverを統合

- サインオフDRC/LVS/FILLをインプリ全体で適用し圧倒的な設計期間短縮を可能にするPegasus Signoff Verify Design Flowの紹介

- RC抽出ツールQuantusのもう一つの機能 ~ 基板ノイズ解析

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues