Allegro In-Design AnalysisにSigrity PowerSI/Clarity 3D Solverを統合

前回の記事(基板レイアウト設計者によるスクリーニング・チェック Allegro In-Design Analysis)にて3つのAllegro In-Design Analysisワークフローを紹介いたしました。今回OrCAD®およびAllegro® 17.4-2019 QIR4 [S028 March 2022] リリースでは、新たにInterconnect Model Extraction (IME) ワークフローが追加され、従来のレイアウト設計ツールと解析ツール間のイタレーション時間を大幅に削除し、手間を掛けることなく信号配線のSパラメーターモデルを抽出できるようになりました。また、Clarity™ 3D Solver抽出エンジンとCadence® Sigrity™ Xによって強化されたSigrity™ PowerSI®抽出エンジンを使用しているため、分散処理による解析時間の短縮や抽出結果のSパラメーターモデルをTopology WorkbenchへエクスポートすることでSI解析を容易に実行することができます。本稿では、このIMEワークフローの簡単な使用例を紹介いたします。

Interconnect Model Extraction (IME) の使用例の紹介

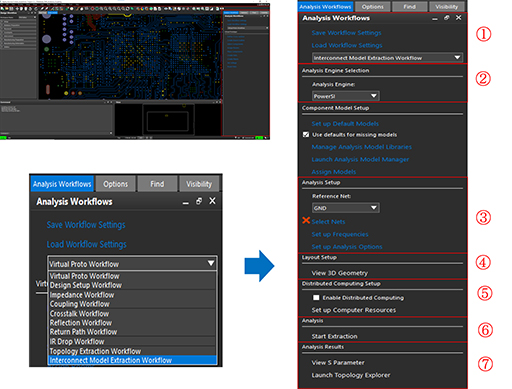

IMEワークフローの実行手順を各項目に分けると以下の様になります。

① Analysis Workflows

Allegro PCB Editorメインウィンドウの右側にあるAnalysis Workflowsウィンドウより、ワークフロー設定を切り替えることができます。ドロップダウンリストより、Interconnect Model Extraction Workflowに切り替えます。今回はDDR配線のSパラメーターを抽出するため、以下の7つのセクションを順次設定します。

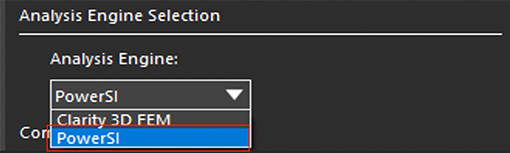

② Analysis Engine Selection

Analysis Engine Selectionセクションで抽出エンジン(PowerSIおよびClarity 3D FEM)を選択します。今回は、PowerSIを選択して抽出を実行します。

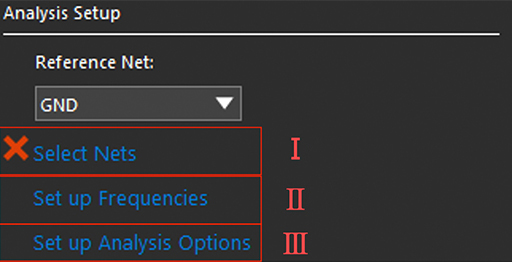

③ Analysis Setup

Analysis Setupセクションで抽出するネットや周波数帯域、解析オプションを設定することができます。

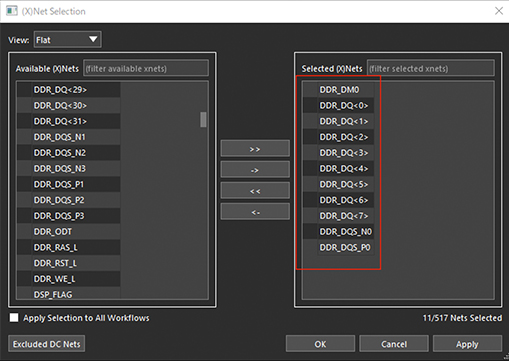

Select Netsをクリックし、(X) Net Selectionウィンドウ内で抽出するネット(DDR配線)を選択します。

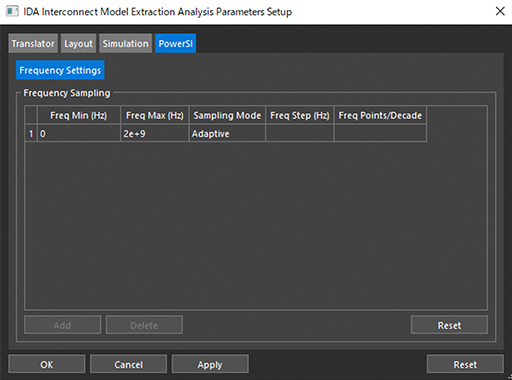

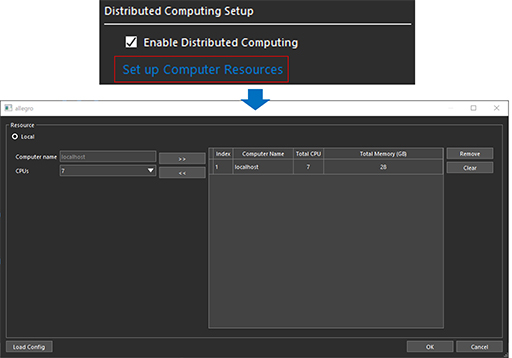

Set up Frequenciesをクリックし、Sパラメーターの周波数帯域を設定します。

Set up Analysis OptionsよりSパラメーターモデル出力形式やSpecial Void、IPC (Inter Plane Coupling) 等の設定を行うことができます。

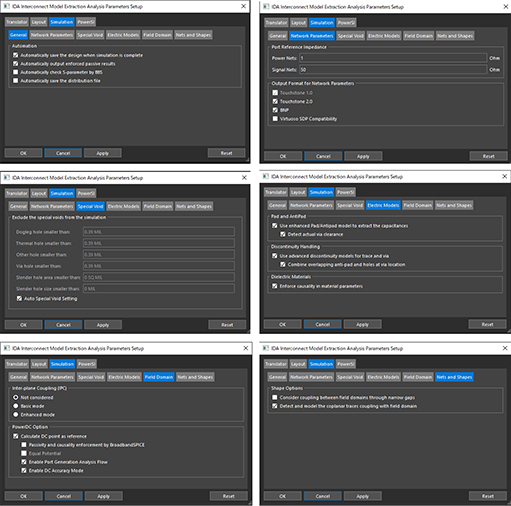

④ Layout Setup

View 3D Geometryをクリックし、シミュレーション対象のインターコネクトモデルを3D表示することができます。

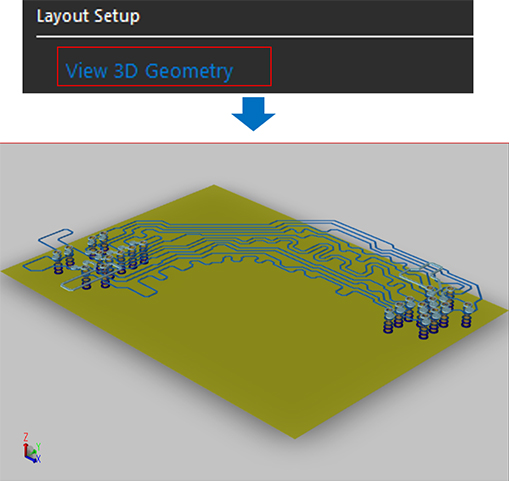

⑤ Distributed Computing Setup

Set up Computer Resourcesをクリックし、Sパラメーターモデル抽出時のPowerSIやClarityエンジンの分散処理を実行するコンピュータリソースを設定します。

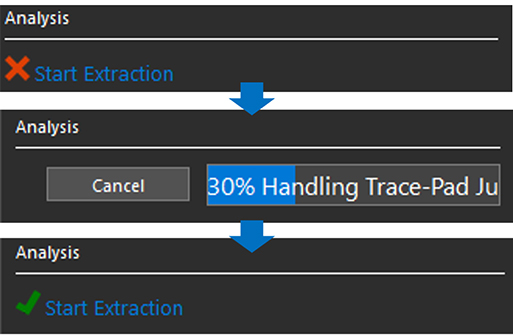

⑥ Analysis

Start Extractionをクリックし、Sパラメーターモデル抽出を開始します。ステータスバーには抽出の進捗状況が表示され、抽出が完了時には緑のチェックが表示されます。

⑦ Analysis Results

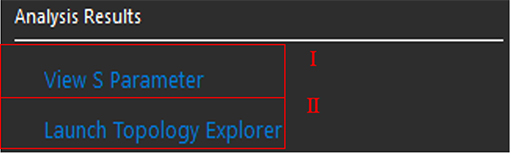

Analysis Resultsセクションでは、抽出結果の確認や、結果をTopology Workbenchへエクスポートすることが可能です。

View S Parameterをクリックすることで、BNP1 Viewerを起動しSパラメーターを確認することができます。

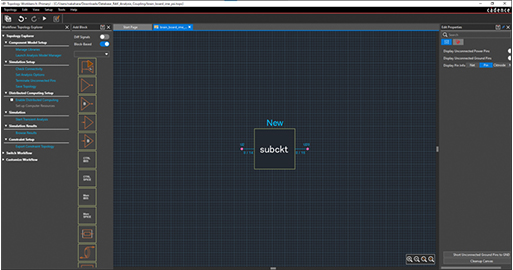

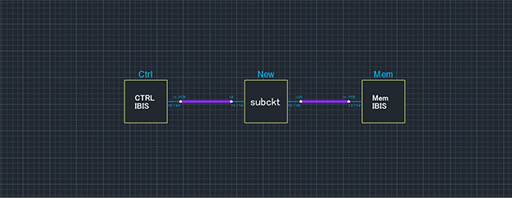

Launch Topology Explorerをクリックすると、Topology Workbenchが起動しインターコネクトモデルがインポートされます。

トポロジーにコントローラーとメモリーを追加し、ネット接続を行います。

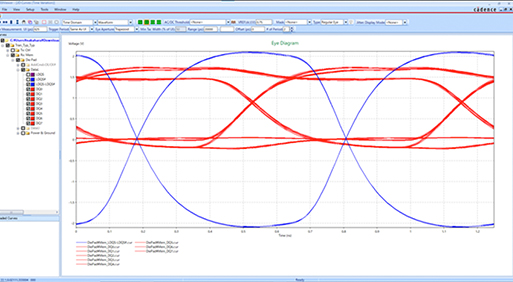

ビットパターンをRandomに設定し、シミュレーションを実行します。

シミュレーション完了後、SSIViewerが起動し、波形を確認することができます。

まとめ

AllegroのIn-Design Analysisは、OrCAD®およびAllegro® 17.4-2019 QIR4 [S028 March 2022]リリースにおいて、SI/PI解析エンジニア向けの解析機能(クロストーク、リフレクション、トポロジー抽出、IR Drop解析)に本稿で紹介したInterconnect Model Extractionワークフローが加わりました。Allegroレイアウト設計環境のGUI上でネットを選択するだけで、既に実績のあるFEM(有限要素法)のEMソルバーであるPowerSIやClarity 3D Solverを用いたSパラメーターモデル抽出を実行する事ができます。また、In-Design Analysisには他にも基板レイアウト設計者向けスクリーニング・チェック (Impedance、Coupling、Return Path) が含まれておりますので、是非ご活用いただき設計/解析業務の改善に役立ててみては如何でしょうか?

今回、ご紹介の内容に関しましてお問い合わせがございましたら、貴社担当営業、あるいはメール: [email protected]へご連絡ください。

カスタム&システムグループ マルチフィジックス・システム解析チーム

中原 正裕

1 Cadence Broadband Network Parameterの略で、BNPファイルは、バイナリー形式のSパラメーターファイルです。

Latest Issue

- 新製品Fidelity CFD : CFDの可能性を解き放つ

- Quantus FS (Field Solver) 最新機能のご紹介

- Cadence Online Support (COS) サイトで字幕付きのビデオがリリースされました。

- Cadence Topics: CadenceLIVE Japan 2022開催!

- チップレット活用の時代へ向けたケイデンスIntegrity 3D-ICプラットフォーム

- 革新的なマシンラーニングベースの設計システム製品Cerebrus Intelligent Chip Explorer

- 自動運転シミュレーションができる車載向けエッジAIの自動ハードウェア設計・検証環境

- Cadence AWR Design Environmentの進歩

- PCBデザイン管理環境Allegro Pulseを利用することで本領発揮するAllegro System Capture

- サインオフDRC/LVS/FILLをインプリ全体で適用し圧倒的な設計期間短縮を可能にするPegasus Signoff Verify Design Flowの紹介

- RC抽出ツールQuantusのもう一つの機能 ~ 基板ノイズ解析

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues