サインオフDRC/LVS/FILLをインプリ全体で適用し圧倒的な設計期間短縮を可能にするPegasus Signoff Verify Design Flowの紹介

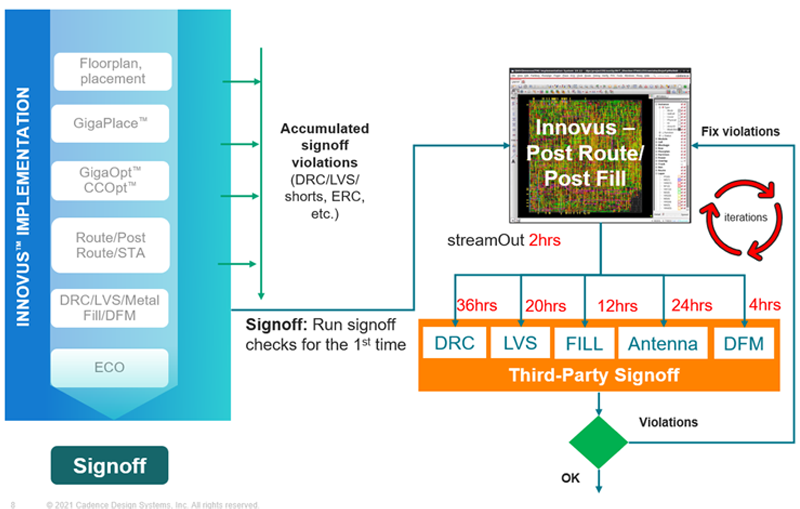

Innovus™と3rd-Party Signoff DRC/LVS/FILL/DFM flow

図1に典型的なInnovusと3rd-paty Signoff DRC/LVS/FILL/DFMフローを提示しますが、これは以下の理由から複雑なsignoffチェックとなります。

- Advanced-nodeプロセスの複雑さは、配置・配線とcoloringに影響を与えます

- タイミングに対するdummy metal FILLの影響

- 大規模SoCにおけるLVSデバッグの問題

- 高電圧、ERCの複雑さによるオープン/ショートデバッグの遅延

その為、設計者の修正作業に時間が掛かり、signoffの結果を得るために数日要する場合があります。

図1:典型的なInnovusと3rd-party signoffフロー

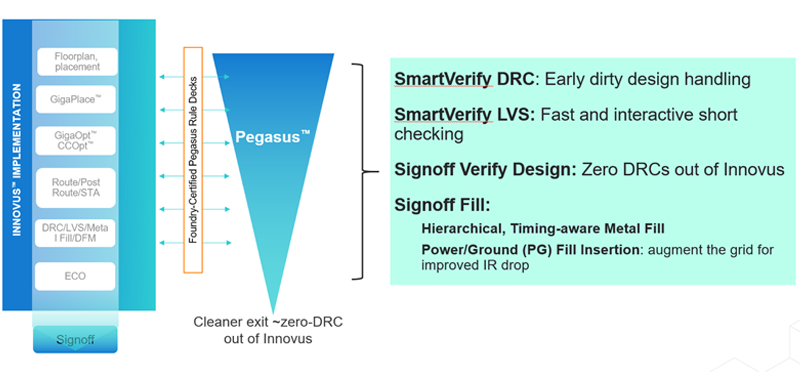

InnovusとPegasus™ In_design DRC/LVS/FILL flow

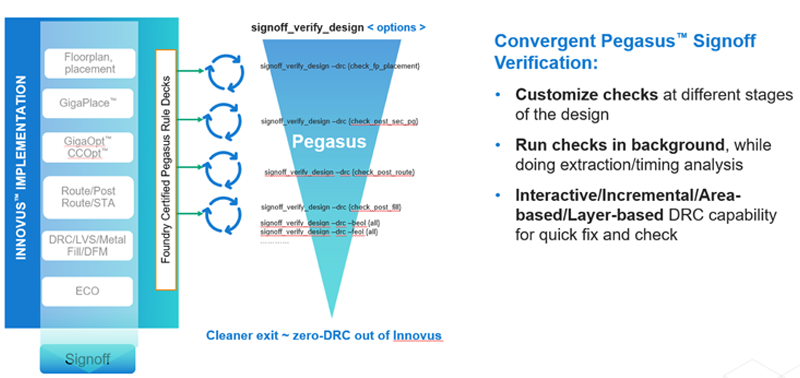

複雑なsignoffチェックの中で設計者の修正作業時間を短縮する為にCadenceでは以下のFlowを提供します(図2)。

- SmartVerify DRC: 初期段階の大量のエラーがあるデザインへのDRCチェック

- SmartVerify LVS: 高速でインタラクティブなオープン/ショートチェック

- Signoff Verify Design: InnovusからDRCをゼロに

- Signoff FILL:

- HMF:階層、Timing-awareなDummy Metal FILL挿入

- PG FILL:Power/Ground (PG)FILL挿入でグリッドを拡張してIRドロップの最適化

図2:InnovusとPegasus In_designフロー

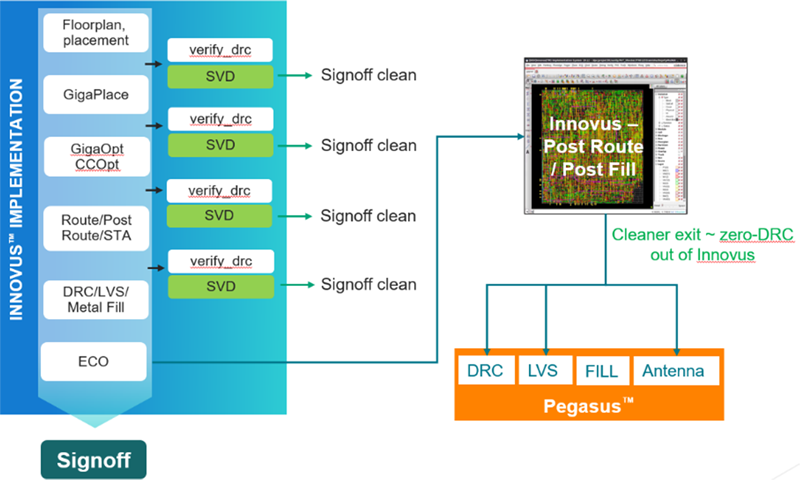

Signoff Verify Design (SVD)の必要性

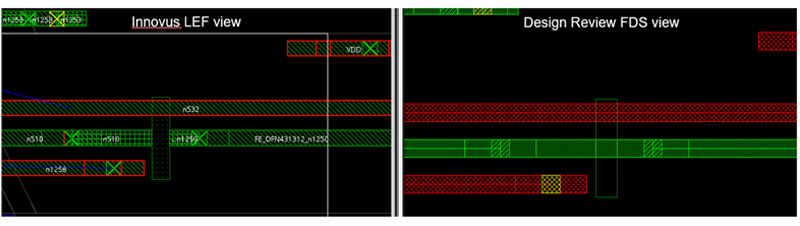

Signoff Verify Design (以降、SVD) DRCは、LEFビューではなく、完全にマージされたGDSでDRCチェックを行います。

図3:Innovus™とPegasus™ In_designでの提案フロー

これは、Innovusのverify_drcに加えてSVD DRCを使用して(図3)、追加のDRCの問題を検出し、初期段階でデザインのsignoff品質を保証できます:

- Signoff DRCルールデッキの使用

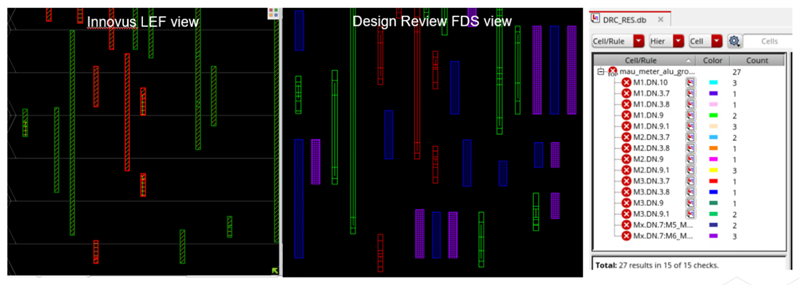

- LEFとGDSの不一致によって引き起こされる問題の検出(図4)

- LEFとGDSのバージョンの不一致により、マージされたGDSは異なります。このような場合、SVD DRCは、不一致が原因で潜在的なDRCを検出できます

図4:LEFとGDSのミスマッチ

- LEFとGDSのバージョンの不一致により、マージされたGDSは異なります。このような場合、SVD DRCは、不一致が原因で潜在的なDRCを検出できます

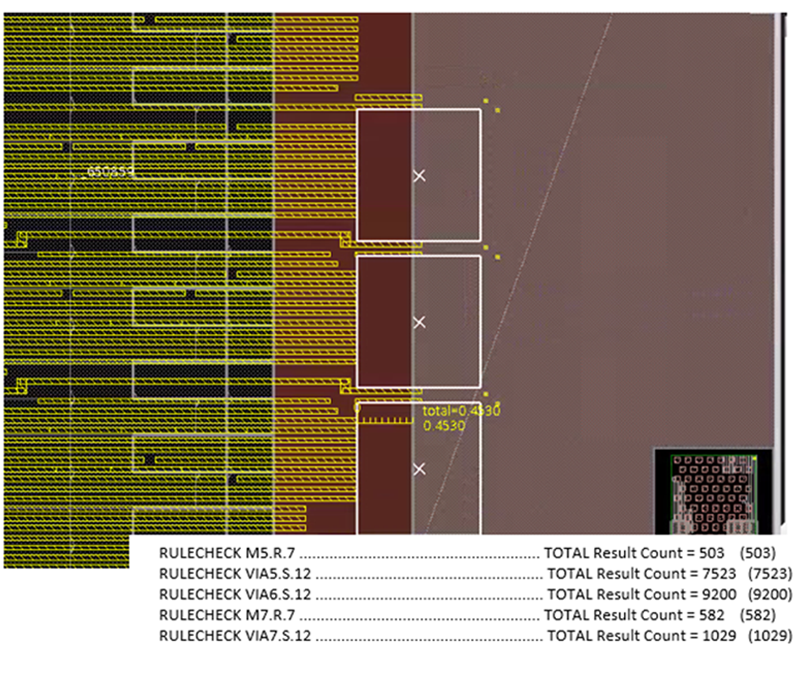

- 密度、最大スペース、マクロ境界のDRC(図5)

- IPがその境界の近くでRouting/FILLされなかった例になります。このような場合、Routing領域とIPの間にDRCが存在する可能性がありますが、IPの内容はInnovusには表示されません。ただし、これはSVD DRCでは検出できます

図5:境界DRC - 配線密度およびMetal FILL関連のDRC(図6)

- IP Blockageとsignoff Metal FILLでは、InnovusのverifyMetalDensityの結果を使用して密度の問題を検出する事は出来ません

- Signoff Metal FILL(図の青/紫色)は、GDSを使用したSVD DRCでは、密度およびDummy Metal FILLに関連するDRCを検出できます

図6:密度およびDummy Metal FILLに関連するDRC - FEOL違反の検出

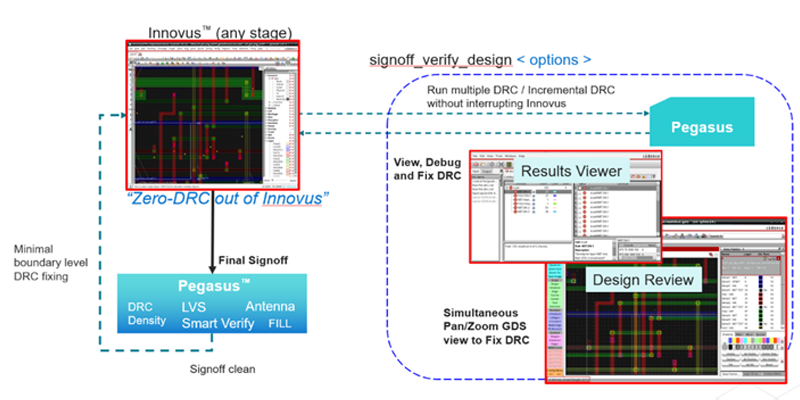

また、Innovusを中断せずに複数のDRC/インクリメンタルDRCの実行が可能で、Pegasus Result Viewer(RV)でDRCエラーの表示、デバッグ、またPegasus Design Review(DR)を併用する事でマージしたGDSでも同時にエラー箇所をパン/ズームが可能で、エラー解析と修正が高速に行えます。

これにより、最終signoffのイタレーション回数を軽減する事ができます(図7)。

SVD DRCは、

図7:最終signoffとデバッグ、修正フロー- 設計のさまざまな段階でチェックをカスタマイズします

- 抽出/タイミング分析を行いながら、バックグラウンドでチェックを実行します

- 迅速な修正とチェックのためのインタラクティブ/インクリメンタル/エリアベース/レイヤーベースのDRC機能

により、Pegasusによるsignoff検証の収束が可能で生産性が約5倍向上します(図8)。

図8:統合されたPegasus検証によるInnovus signoff検証設計

SmartVerify LVSの必要性

InnovusのverifyConnectivityとverify_drcは、デザインの初期問題を特定する為の機能です。

ただし、いくつかの制限があります:

- 電力網をチェックするときにverifyConnectivityによって、以下の理由から誤った違反にフラグを立てる可能性があります

- 一部のウェルタップセルのLEFモデルには、ピンが定義されていません。したがって、すべてのウェルタップは基板層から切り離されているように見えます

- これらの違反をWaiveするには、オプション「-noSoftPGConnect」を使用する必要がありますが、ウェルタップセルがないため、実際の問題を見逃すリスクがあります

- 以下いくつかのケースのショートに関してはチェックできません

- LEFとGDS間の不整合が原因のケース

- ブロック階層を介して(LEFビューレベルでは表示されません)のケース

- テキストの無い内部ネット間(LVS比較で検出できます)のケース

- Innovus™では利用できないレイヤーを介しているケース

SmartVerify LVSの付加価値は以下になります。

- 「通常のLVS」では利用できない追加のチェック(配置の短絡、欠落しているポート、追加のポート、および短絡を特定)。これらは、完全なLVS比較でのみ見つけることができます

- LEFビューは使用せず、マージされた実際のGDSおよびSignoff LVSルールデッキが使用されます

- エリアベースモードが使用できます

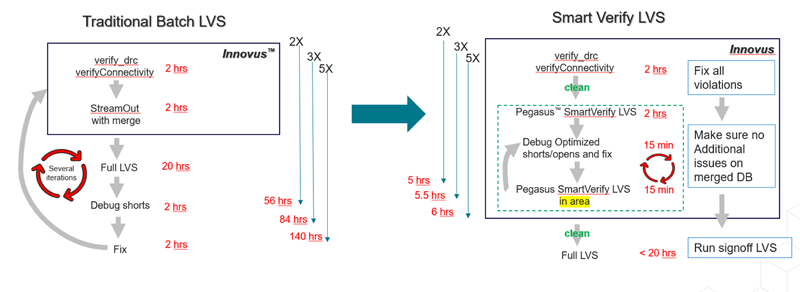

- 完全なLVSおよびInnovus™のverify_drcと比較して実行時間が高速です(図9)

- 実行時間が高速であることで、エラーをクリアにするまでの時間が従来のフローに比べて5倍以上短縮できます

図9:SmattVerify LVSの提案フロー - ERCはファウンドリルールデッキからチェックします

- オープンエラーを検出できます

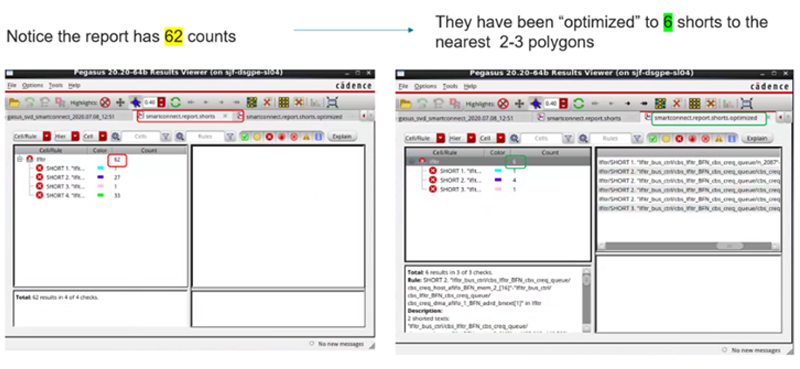

SmartVerify LVSの特徴であるショートエラー数の最適化により、エラー箇所の特定と修正が迅速に行えます(図10)。

図10:SmattVerify LVSのショートエラー数の最適化

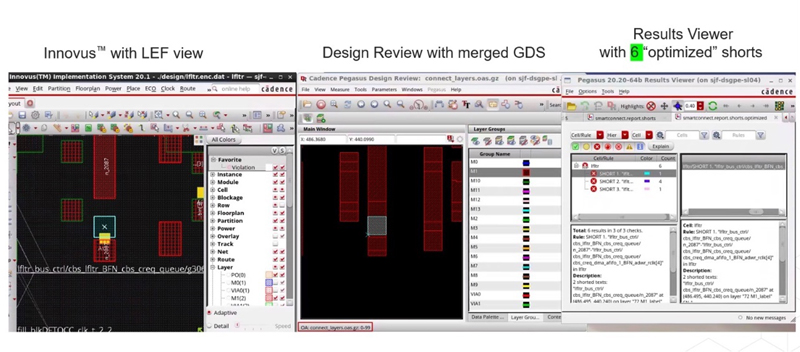

また、Innovusを中断せずに複数のSmartVerify LVSの実行が可能で、Pegasus Result Viewer(RV)でDRCエラーの表示、デバッグ、またPegasus Design Review(DR)を併用する事でマージしたGDSでも同時にエラー箇所をパン/ズームが可能です(図11)。

図11:SmattVerify LVSの提案フロー

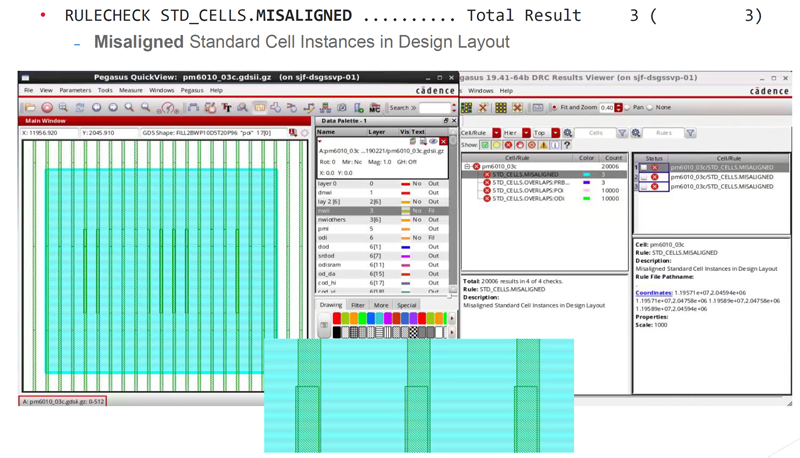

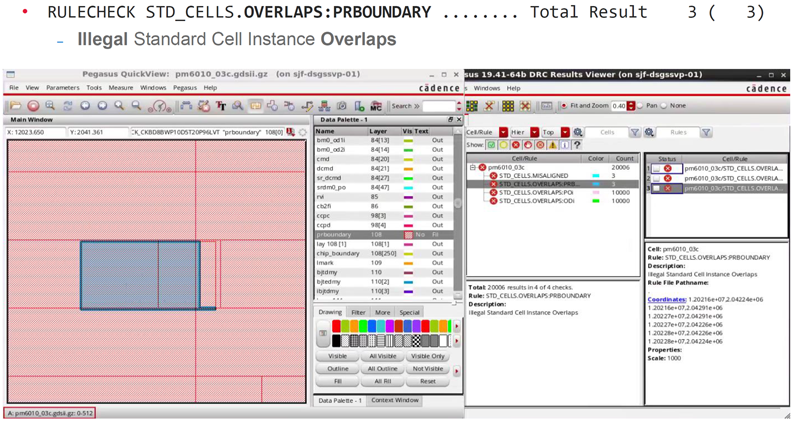

SmartVerify DRCの必要性

SmartVerify DRCは、設計の初期段階で使用します。この段階に完全なDRCを実行すると、エラー数が多い場合に使用可能な結果が得られない場合があります。

違反数が多い原因は、セルの配置のずれ(図12)やオーバーラップ(図13)等の設計に大きな問題がある可能性があります。

図12:セル配置ずれエラー例

図13:オーバーラップエラー例

SmartVerify DRCは、デザインの主要なDRC違反をすばやく特定し、フルチップ設計サイクルを短縮します。またsignoffフローでの重大な問題も事前に防止します。

SmartVerify DRCは、Signoff DRCに比べて実行時間が高速です(図14)。

| Design | Node | Size | Flow | Signoff (hrs) | SmartVerify (hrs) |

|---|---|---|---|---|---|

| A | N16 | 25 x 22 | DRC | 27 | 2.5 |

| LVS | 25 | 8 | |||

| B | N7 | 13 x 11 | DRC | 18 | 1.2 |

| LVS | 15 | 2 | |||

| C | N7 | 25 x 25 | DRC | 12 | 1.1 |

| LVS | 8.4 | 2.3 |

図14:Signoff DRCとSmartVerify DRCの実行時間の比較

SmartVerify DRC、SmartVerify LVSおよびSVD DRCの違い

図15にそれぞれの特徴を示します。

また、共通の機能としては、「バックグランドでの実行」、「ジョブのモニタリング」、「Result Viewer + Design Reviewの統合」、「どの設計ステージでも実行可能」があります。

| Flow | Tagline | Input needed | Features |

|---|---|---|---|

| SVD DRC | Innovus™からのDRCゼロ | Signoff DRC deck、Innovus map file | 事前設定されたスイッチ。 構成可能なスイッチ。 レイヤーとエリアベース。 |

| SmartVerify LVS | 高速なインタラクティブショートチェック/デバッグ | Signoff LVS deck、Innovus map file | フルデザインまたはエリアで10倍高速。 |

| SmartVerify DRC | 設計初期段階でのDRCチェック | セル配置のズレや重なりのチェック。 |

図15:SVD DRCとSmartVerify DRC/LVSの違い

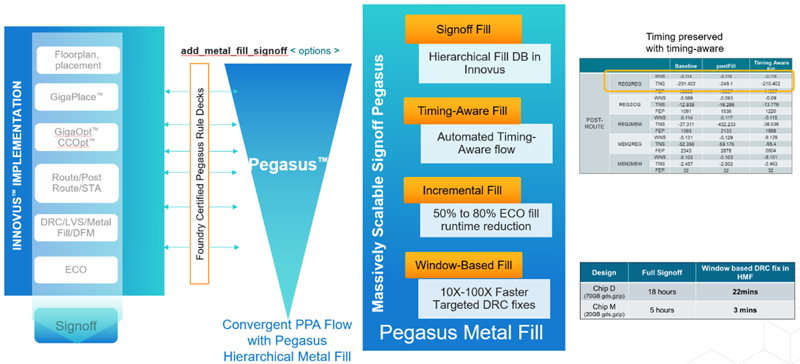

Innovus/Pegasus Signoff Metal FILL flow

Pegasus Signoff Metal FILL flowはInnovus™の緊密な統合により、データベースの設計/Metal FILLの読み取り/書き込みおよび保存/復元の全体的な所要時間が改善されます。

Advanced ノードにおいてタイミングへの影響はMetal FILLの複雑さが増すことによって引き起こされます。また、DRCクリーンな結果を達成するために必要な操作が増加します。

その為、Pegasus Signoff Metal FILL flowでは、重要なネットの周りの配線のFILLをトリミングして、最小の密度を維持しながらタイミングの影響を減らすtiming-awareな機能があります(フローに統合されたトリミング機能)(図16)。

図16:Innovus™/Pegasus™ Signoff Metal FILL Flow

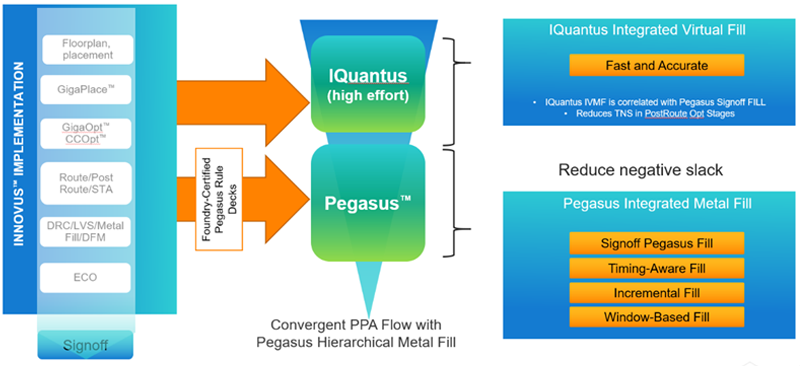

また、高速で高精度のIQuantusの統合とPegasus統合された階層的なMetal FILL (Signoff FILL/Timing-Aware FILL/Incremental FILL/Window-Based FILL)によるネガティブスタックを軽減してPPA収束フローが実現できます。

図17:Pre-RouteからsignoffへのMetal FILL収束

Innovus/Pegasus Signoff Metal FILL flow

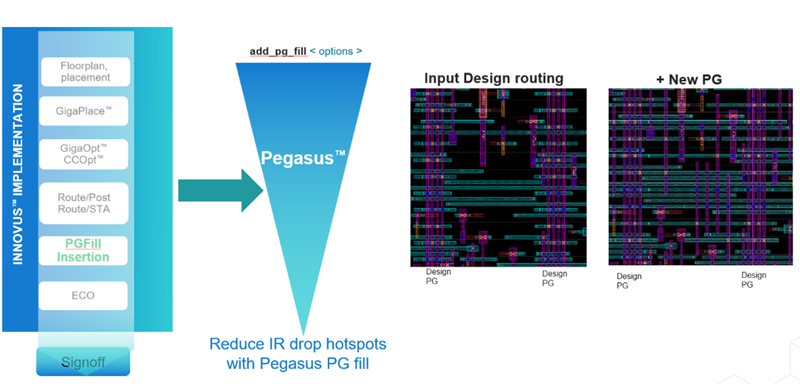

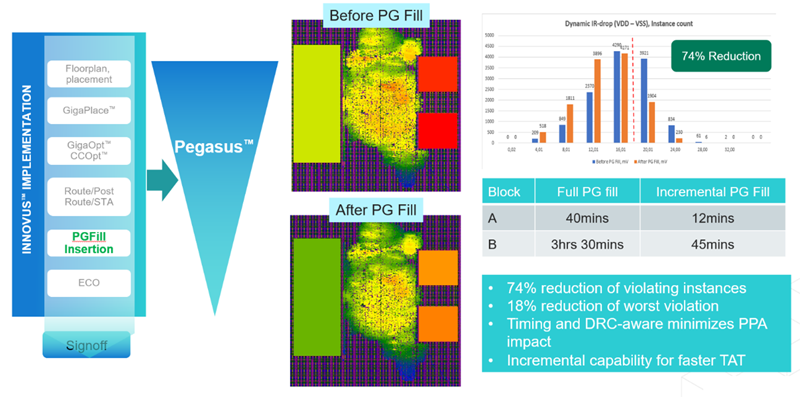

In_designのPegasus Power/Ground(PG)FILLは、IRホットスポットを削減します。

Power/Groundに接続されているデザインの配線トラックにFILLを挿入し、効果的なPGストライプを最大化します(図18)。

既存のPGネットワークへの最適な接続により、Signoff DRCとタイミング認識はPPAの影響を制限します。ECOにも対応しており、Signoff Rule Deckは必要ありません。

図18:In-DesignトラックベースのIR Drop最適化用PG FILL挿入

図19の例では、違反するインスタンスが74%削減され、最悪の違反を18%削減されました。

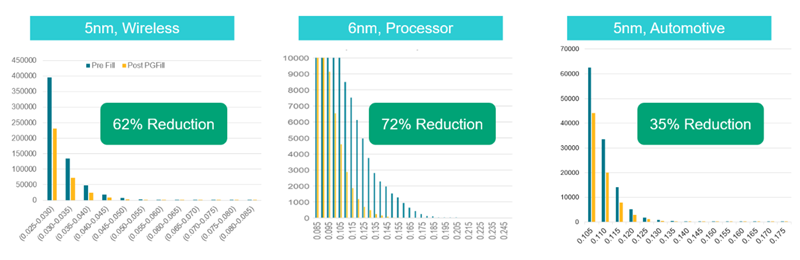

また、様々な用途の設計にも効果(35~72%削減)が得られています(図20)。

タイミングとDRC対応により、PPAの影響が最小限に抑えられます。

より高速なTATのためのインクリメンタル機能も搭載しています。

図19:In-Design IR Drop最適化用PG FILL挿入例-1

図20:In-Design IR Drop最適化用PG FILL挿入例-2

主な機能として以下が上げられます。

- 多くのマシンを使用した非常にスケーラブルな実行(LSF / qsubをサポート)

- ECOステージ中のインクリメンタルPG FILLによるTATの3〜5倍の改善

- さまざまな電圧ドメインのArea/Layerをシームレスにサポートするマルチ電圧ドメインのサポート

まとめ

InnovusとPegasus In_design DRC/LVS/FILL flowでは、Innovusに全体で統合されたPegasus Signoffにより、

- InnovusまたはTempus ECOの任意の段階で特定のチェックを実行する柔軟性

- SmartVerifyによる最速のデバッグ環境:

- SmartVerify DRC:初期のダーティデザイン処理

- SmartVerify LVS(SmartConnect):高速ショートチェック

- TATが3倍から4倍速くなり、生産性が向上

- Pegasus Result ViewとPegasus Design Reviewによる高速デバッグ

- インクリメンタルでタイミングを意識したDummy Metal FILL挿入により、TATが50〜80%削減

- IRドロップ最適化の為のPegasus PG FILLフローによるより高速な設計クロージャを提供、その結果In_designのsignoff クロージャは、最高のPPAで最速のsignoff収束を実現します

フィールドエンジニアリング&サービス本部

デジタル&サインオフ テクニカルリーダー

佐藤 真之

Latest Issue

- 新製品Fidelity CFD : CFDの可能性を解き放つ

- Quantus FS (Field Solver) 最新機能のご紹介

- Cadence Online Support (COS) サイトで字幕付きのビデオがリリースされました。

- Cadence Topics: CadenceLIVE Japan 2022開催!

- チップレット活用の時代へ向けたケイデンスIntegrity 3D-ICプラットフォーム

- 革新的なマシンラーニングベースの設計システム製品Cerebrus Intelligent Chip Explorer

- 自動運転シミュレーションができる車載向けエッジAIの自動ハードウェア設計・検証環境

- Cadence AWR Design Environmentの進歩

- PCBデザイン管理環境Allegro Pulseを利用することで本領発揮するAllegro System Capture

- Allegro In-Design AnalysisにSigrity PowerSI/Clarity 3D Solverを統合

- RC抽出ツールQuantusのもう一つの機能 ~ 基板ノイズ解析

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues