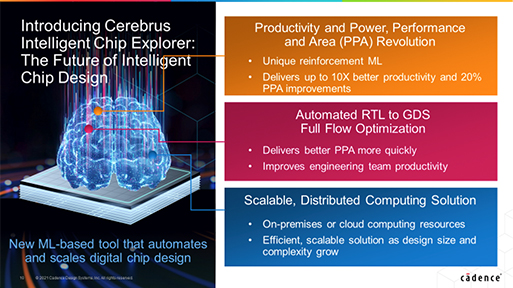

革新的なマシンラーニングベースの設計システム製品Cerebrus Intelligent Chip Explorer

デジタル設計の自動化をさらに進化させ、顧客に求められるチップ設計の目標を効率的に達成するマシンラーニングベースの設計システム製品Cadence® Cerebrus™ Intelligent Chip Explorerについて紹介します。

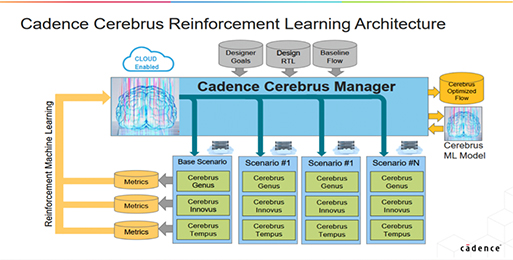

Cerebrusは、マシンラーニングを活用した、チップ設計フローの最適化を自動化する画期的なアプローチです。Cerebrusは完全に自動化された方法で、ケイデンスのRTLからサインオフまでのデジタルインプリメンテーション設計フロー全体で使用することが可能で、パワー、パフォーマンス、エリア、配線混雑(PPAC)の目標を満たすようにベストな結果を導き出します。様々なプロセスノード上で開発されるコンシューマー、ハイパースケールコンピューティング、5G通信、自動車、モバイルデザインなど、高機能化、大規模化、複雑化している現在のシステムオンチップ(SoC)設計においては、PPAC改善および設計効率化は共通の課題です。Cerebrusにより、インプリメンテーション設計の生産性を最大10倍、PPAを20%改善できることが確認できています。オンプレミスおよびクラウド上のコンピューティングリソースを最大限に利用することで、一人の設計エンジニアが複数ブロックを同時に設計することが可能になり、エンジニアリングチーム全体の生産性が大幅に向上します。

Cerebrusは以下のようなメリットを提供します。

- マシンラーニング機能の強化 : 人手では考えられないようなフローソリューションを早期に見つけ出し、PPACおよび生産性を向上

- ラーニングモデル再利用 : 設計で得た知見を将来の設計に自動的に適用し、より良い結果を得るまでの時間を短縮

- 設計生産性の向上 : 1人のエンジニアが、多数のブロックに対してRTLからGDSへのフロー全体にわたり同時にかつ自動的に最適化することが可能になり、設計チームの生産性が向上

- 大規模並列処理 : オンプレミスおよびクラウドに対応する拡張性の高い設計空間探索テクノロジを提供し、フローの最適化を迅速に実現

- 使い勝手の良いユーザインタフェース: 強力な設計コックピットにより、実行ジョブ管理とインタラクティブな結果分析が可能となり、設計メトリクスに関する重要な知見を得ることが可能

Cerebrusに関する詳細についてはこちらをご参照ください。

Cerebrus製品紹介ビデオ、ユーザ事例のビデオ、製品概要資料など、様々な情報を紹介しています。

また、好評いただいているCadenceTECHTALKでも、Cerebrusを紹介していますので、日本語スライドや英語版ビデオも是非ご覧ください(CadenceTECHTALKのスライドやビデオをご覧いただくためには、サポートサイトにログインしていただく必要がございます)。

フィールドエンジニアリング&サービス本部

岡村 亮介

Latest Issue

- 新製品Fidelity CFD : CFDの可能性を解き放つ

- Quantus FS (Field Solver) 最新機能のご紹介

- Cadence Online Support (COS) サイトで字幕付きのビデオがリリースされました。

- Cadence Topics: CadenceLIVE Japan 2022開催!

- チップレット活用の時代へ向けたケイデンスIntegrity 3D-ICプラットフォーム

- 自動運転シミュレーションができる車載向けエッジAIの自動ハードウェア設計・検証環境

- Cadence AWR Design Environmentの進歩

- PCBデザイン管理環境Allegro Pulseを利用することで本領発揮するAllegro System Capture

- Allegro In-Design AnalysisにSigrity PowerSI/Clarity 3D Solverを統合

- サインオフDRC/LVS/FILLをインプリ全体で適用し圧倒的な設計期間短縮を可能にするPegasus Signoff Verify Design Flowの紹介

- RC抽出ツールQuantusのもう一つの機能 ~ 基板ノイズ解析

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues