自動運転シミュレーションができる車載向けエッジAIの自動ハードウェア設計・検証環境

~DUTを組み込んだ自動運転のシステム検証を簡単に~

本稿では、柔軟かつ短期にニューラルネットワークモデルを車載向けハードウェアに自動実装し、自動運転シミュレーションによるシステム検証が可能な設計・検証環境をご紹介します。

ニューラルネットワークのハードウェアの課題

ニューラルネットワークによる物体認識や音声認識の技術は日進月歩の発展を遂げていて、新しいニューラルネットワークの提案も盛んに行われ、半年や一年もすれば、最新技術もすぐに更新されてしまうという開発競争が激しい分野であり、成功のためには、常に最新技術動向に目を向け、タイムリーな製品開発と市場投入が求められます。これは車載分野であっても同様です。

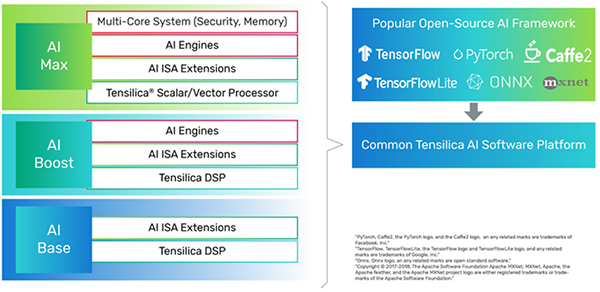

ニューラルネットワークモデルは、通常、TensorFlowやPytorchなどの汎用フレームワークを用いてPC上で開発され、GPUを用いない省電力用途では、高位合成など様々なアプローチにより、量子化などを行いながらハードウェアに実装されますが、ここでは、弊社のTensilica® DSPを用いたソフトウェアソリューションによるハードウェア実装について、ご紹介します。

汎用フレームワークを用いてニューラルネットワークを設計、学習し、求める推論精度が得られた後は、これを組込みのハードウェアに実装すると、果たしてどのくらいの実行時間で、回路規模、動作周波数や消費電力がどうなるか、量子化による推論精度の劣化はどの程度か、そしてハードウェアをシステムに組み込んだ時に、正常にシステム動作するのかどうかが、次の課題になるのではないでしょうか。

柔軟かつ短期にニューラルネットワークモデルを車載向けハードウェアに自動実装

ハードウェアの実装アプローチには様々なものがありますが、ニューラルネットワークの分野は未だ発展途上で、新しいアルゴリズムが次々に提案される状況であるため、これを長い開発期間を掛けて実装することは、出来上がった頃には既に陳腐化して競争力が無いというようなことになりかねず、非常にリスクを伴います。このため、このようなアルゴリズム自体が流動的な段階では、DSPのように、特定用途向けに高性能かつ省電力の専用演算回路を持ちながら、ソフトウェアでアルゴリズムを変更可能な、ソフトウェアソリューションによる実装が最適です。

DSPであれば既にハードウェアがありますので、実行時間や回路規模、動作周波数や消費電力、推論精度についてはすぐに評価可能です。Tensilica DSPには、AI向けのシリーズ1 がありますので、このシリーズの中から目的に合ったものを選択したり、Tensilicaの大きな特徴であるコンフィギュレーションの変更や追加命令(TIE2 : Tensilica Instruction Extension)の実装によりDSPをカスタマイズしたりして、アプリケーションに最適なハードウェアを得ることが出来ます。DSPのソフトウェアについても、ニューラルネットワークモデルからDSPで実行可能なソースコードに自動変換するニューラルネットワークコンパイラやAI向けライブラリが提供されていますので、短いTATで開発が可能です。Tensilica DSP IPはSEooC(Safety Element out of Context)としてISO26262の認証を受けていますので3、お客様のデザインの機能安全認証にも安心してお使いいただけます。

1 Tensilica AI Platform (cadence.com)

2 https://www.cadence.com/en_US/home/tools/ip/tensilica-ip/technologies.html#tie

3 Cadence Achieves Industry-First ASIL B (Random) and ASIL D (Systematic) Compliance Certification for Automotive Radar, Lidar and V2X DSP IP | Cadence IP

自動運転オープンソースソフトウェアAutowareを用いた組込み実証実験

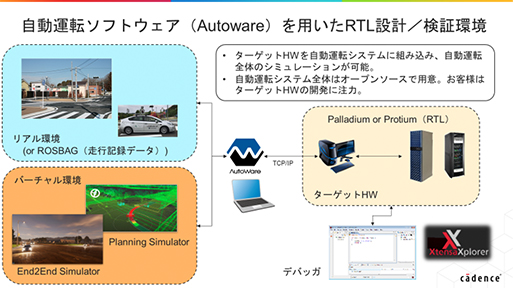

それでは、自動運転のシステムに開発中のハードウェアを組み込んで自動運転システムが正常に動作することを、どのようにして確認したら良いでしょうか。例えば、カメラやLiDARなどのセンサーに搭載するAIを開発しているのに、自動運転システム一式を独自に用意しないといけないとなると、非常に大きな負担となってしまいます。

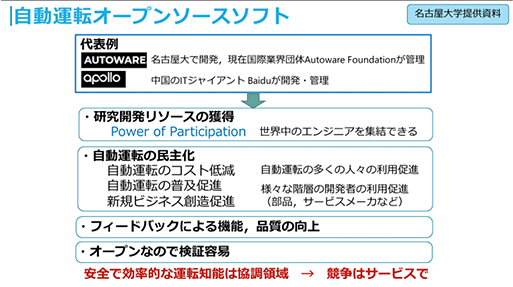

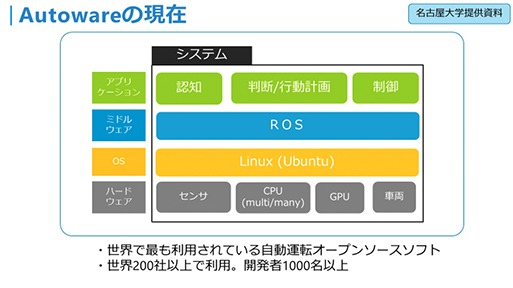

このような問題の解決のために、Autowareという一般道レベル4に対応した自動運転ソフトウェアがオープンソースで公開されています4。Autowareは自動運転車に必要な「認知」「判断」「操作」を行う機能と、自動運転をシミュレーションするための実行環境が集約されたオープンなプラットフォームで、自動運転のコスト低減や普及促進、新規ビジネス創造促進などのために、様々な階層の開発者など、自動運転に関わる多くの人々に使用して貰うことを想定しており5、世界中のエンジニアを集約できるプラットフォームです。名古屋大学が開発し2015年8月に公開された後、国際業界団体であるAutoware Foundation6 が設立され、現在はAutoware Foundationの管理の下、ワールドワイドで開発が進んでいます。

設計者は、設計対象でない機能はAutowareを流用することで、対象機能の設計に注力して、自動運転システム全体の検証を効率的に行うことが出来ます。利用可能な機能は非競争領域の技術で実装されたものですが、システム動作の検証環境としては十分です。Autowareが世界で最も多くのユーザーに利用されている自動運転オープンソースソフトウェアである点も、安心材料の一つです。

日本ケイデンスは名古屋大学と2020年までの三年間、組込み用途でのAutowareの活用について共同研究し、Tensilica Vision P6 DSP7 を搭載したADAS評価ボード(Dreamchip社製)を組み込んだAutowareを用いて、実際の自動運転車を走行させる実証実験を行いました。

例えば、Autowareを実行させるPCと評価ボードをTCP-IPで接続し、カメラで撮影した画像をリアルタイムで評価ボードに転送し、Vision P6 DSPで車や歩行者などの物体認識をさせて、認識結果をAutoware PCに返す形でシステムを構築し、自動運転車を走行させています。

これにより、Autowareを利用したDUT検証環境が、実際の自動運転システムと同等であることを実証しました。この実証実験の様子は日本ケイデンスのホームページでご覧いただけます8。

4 https://github.com/autowarefoundation

5 Autoware FoundationのプレミアムメンバーであるTIER Ⅳ社の言葉を借りると「自動運転の民主化」

6 he Autoware Foundation - Open Source for Autonomous Driving ケイデンスはAutoware Foundationのインダストリーメンバーです。

7 Vision P6 (cadence.com)

8 Cadence and Autoware—Partnering to Make Autonomous Vehicles for Tomorrow

自動運転シミュレーションによるシステム検証

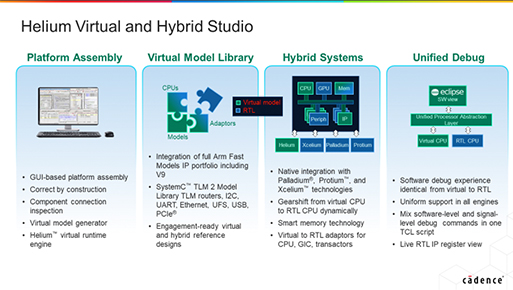

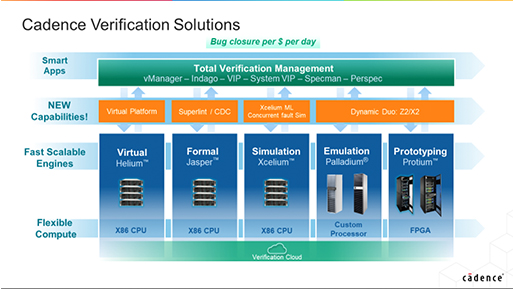

上記実験で用いたADAS評価ボードには500MHz動作するVision P6 DSPを搭載したSoCが実装されていましたが、DUTを新規設計し、DSPを新しくする場合には、RTLシミュレーションが可能な検証環境である必要がありますので、上記の実機環境を、HDLシミュレーション環境に現在移植中です。RTLの実行には、HDLシミュレーションが高速実行可能なエミュレータPalladium®と、更に高速なFPGAプロトタイピング環境Protium™を使用し、AutowareとのTCP-IP通信モジュール(C++)とRTLの組み上げには、RTLとSystemCのハイブリッドシミュレーションが可能な仮想プラットフォームHelium™9 を使用します。

RTLシミュレーション環境になりますので、弊社のEDAツールを使用して、詳細なSoC内部動作の波形観測はもちろん、Joules™10 によるRTLレベルでの電力評価やInterconnect Workbench(IWB)によるバス性能評価などの性能解析、および故障シミュレーションなどが、リアルタイム動作ではありませんが、実際の自動運転時のシナリオを用いて実施可能です。

更には、Autowareにはバーチャルシミュレーション環境がありますので、これを用いることにより、悪路や悪天候などのコーナーケースや、実車では困難な急な飛び出しや事故などのシナリオもテストすることが出来ます。

9 Helium Virtual and Hybrid Studio (cadence.com)

10 Joules RTL Power Solution (cadence.com)

まとめ

本稿では、進歩の激しいAIの分野で、柔軟かつ短期にニューラルネットワークモデルを車載向けハードウェアに自動実装し、Autowareを用いた自動運転シミュレーションによるシステム検証が可能な設計・検証環境について、ご紹介しました。

より詳細な説明は、7月15日(金)に開催予定の弊社ユーザー・カンファレンスのCadenceLIVE Japan 2022にて、デモも交えながら、講演する予定です。

本環境は自動運転をモチーフに開発しておりますが、今後はロボットなど他のシステムにも展開していく予定です。最後までご覧頂き誠にありがとうございました。

システムソリューション テンシリカ

プリンシパルアプリケーションエンジニア

博士(工学)

辻 雅之

Latest Issue

- 新製品Fidelity CFD : CFDの可能性を解き放つ

- Quantus FS (Field Solver) 最新機能のご紹介

- Cadence Online Support (COS) サイトで字幕付きのビデオがリリースされました。

- Cadence Topics: CadenceLIVE Japan 2022開催!

- チップレット活用の時代へ向けたケイデンスIntegrity 3D-ICプラットフォーム

- 革新的なマシンラーニングベースの設計システム製品Cerebrus Intelligent Chip Explorer

- Cadence AWR Design Environmentの進歩

- PCBデザイン管理環境Allegro Pulseを利用することで本領発揮するAllegro System Capture

- Allegro In-Design AnalysisにSigrity PowerSI/Clarity 3D Solverを統合

- サインオフDRC/LVS/FILLをインプリ全体で適用し圧倒的な設計期間短縮を可能にするPegasus Signoff Verify Design Flowの紹介

- RC抽出ツールQuantusのもう一つの機能 ~ 基板ノイズ解析

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues