チップレット活用の時代へ向けたケイデンスIntegrity 3D-ICプラットフォーム

3D-ICの必要性と現状の設計課題

先端プロセス・ノードにおけるトランジスタの微細化に伴い、設計の複雑さや難易度は継続的に上昇しており、先進的なSoC (Systems-on-Chip)の設計コストも上がり続けています。また、そのダイはレチクルのサイズの限界に達しつつあり、大規模な論理・メモリ・I/Oからなるシステムを単一のダイにまとめることが物理的に難しくなりつつあります。

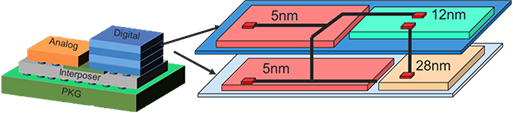

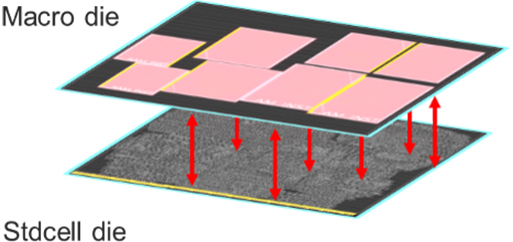

これらの背景から、ICの集積度を高めるため、複数のダイを積層して1つのパッケージに実装する2.5Dや3D-IC技術の適用が増えています。これらの技術によって、システム全体を単一の先端プロセス・ノードで実装するのではなく、異なるプロセス・ノードからなる複数のダイで実装することが可能になります。2.5Dや3D-IC技術を用いた設計では、システムのどの機能ブロックをどのプロセス・ノードに割り当て、さらにそれらのダイをどう積層するかといったプランニングによって、システム全体の性能や消費電力、設計コストや製造コストが大きく影響を受けることになります。消費電力やコストを抑えながら、より高集積度かつ高性能なシステムを継続的に開発するためには、システム全体を高い自由度で柔軟にプランニングできる環境が有用になります(図1)。さらに、異なるプロセス・ノードで開発される様々な構成のシステムにおいて、システム全体のタイミング解析、電力解析、物理検証など各種サインオフ解析、および熱解析をいかに正確に効率よく行うか、という点も重要な課題になります。

図1:異なるプロセス・ノードのダイを積層した3D-ICのイメージ例

既存の2.5Dや3D-IC設計のフローでは、システムのプランニング、実装および解析・検証の各工程は、お互い独立した個別の開発プラットフォームで実施されています。また多くの場合、各ダイやパッケージは異なる設計チームにより個別に設計されて検証され、さらにそれらのデータが最終的にシステムトップとして組み上げられ解析・検証されることになります。この過程で各工程の担当者は、様々な情報(各ダイのプロセス情報やフロアプラン、ダイの位置や向き、積層の形状、bumpの位置、等)を正しく共有し、ファイルの形式変換などを経ながら、工程ごとに異なるプラットフォームをセットアップする必要があります。このため、プランニングを行ってからシステムレベルの解析結果が得られるまで、非常に時間がかかってしまうことになります。システムレベルの解析結果に基づいて最適なプランニングを十分に探索するためには、これらの工程を効率化することも大きな課題となります。

Integrity 3D-IC : 次世代3D-ICプラットフォームの概要

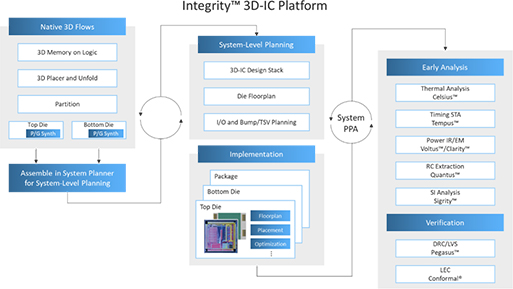

Cadenceでは、上記で挙げた複数の課題に対するソリューションとして、Integrity 3D-ICプラットフォームを提案しています。このIntegrity 3D-ICは、2.5Dや3D-ICに関するプランニングや実装、さらにサインオフ解析・検証を1つのコックピットから行うことができる、業界初めての統合された設計環境です。

図2:Integrity 3DICプラットフォームの設計フロー

このIntegrity 3D-ICプラットフォームには、いくつかのキーとなる特長があります。

-

単一コックピットによる柔軟な3D-ICプランニングと実装

あらゆるタイプの3D-IC設計を取り扱い、単一コックピットでプランニングと実装を行うことができる高機能なプラットフォームです。

-

独自のプランニング機能

システムレベル設計のため、階層プランニングや最適化を行う独自のSystem Plannerを備えています。

-

Innovus™ Implementation Systemとの統合

Tclベースの環境としてInnovus Implementation Systemとダイレクトに統合されており、bumpおよびTSVの柔軟なプランニングを含めた完全な実装環境を提供します。

-

設計を効率化する階層デザイン・データベース

3D-ICの各ダイにおける様々な工程のデータを1つのデータベースとして格納することが可能な、効率的なオン・ディスク・データベースを備えています。

-

2Dデザインを入力とした3Dデザインの探索

2Dデザインを複数のダイに分割する強力なフローにより、メモリ・オン・ロジックやロジック・オン・ロジックからなる3D積層デザインの効率的な探索が可能です。

-

アナログ設計環境およびパッケージ設計環境との協調設計

Cadence Virtuoso®やAllegro®設計環境との協調設計を行うことが可能な、強力なクロス・プラットフォームです。

-

統合されたシステムレベル解析機能

洗練された強力なフロー・マネージャーを備えており、設計早期の電力-熱解析や、複数のダイをまたぐスタティック・タイミング解析(STA)、複数のダイ間の物理検証など各種解析を効率的に実行することが可能です。

System PlannerとInnovus Implementation Systemの連携

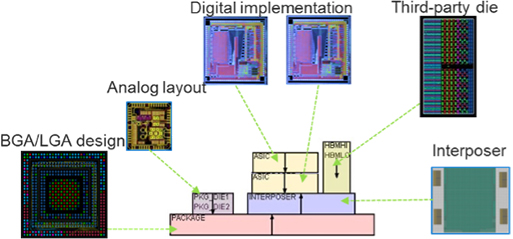

Integrity 3D-ICでは、System Plannerを使用することで3D-ICに必要な全てのデバイスを積層したデータを作成することが出来ます。これには、デジタル・ダイやアナログ・ダイ、パッケージやPCBボードなどが含まれます(図3)。また、巨大なデザイン・データを扱うレイアウト用のビューアと異なり、System Plannerでは3D-ICシステムのための軽量なビューアを備えています。このビューアは、ダイの積層の構成やフロアプランニング、およびダイ間のインターフェースの設計に特化したことにより軽量となっています。

一方、レイアウト実装はInnovus Implementation System上で実行され、デジタルIC設計において使用されている配置配線や最適化に関する全ての機能を利用することが可能です。またレイアウト実装に関連して、Integrity 3D-ICではマルチ・ダイに対応したレイアウト用ビューアも備えています。設計者は、異なるプロセス・ノードで開発される複数のダイを単一のビューアで表示することができ、システムレベルの解析結果を確認しながら、ダイを跨ぐデザイン上の問題をデバッグすることが出来ます。また、3D-ICのデジタル・ダイを設計するために有用な、3Dへのデザイン分割機能も備えています。

さらにIntegrity 3D-ICにおいては、設計者はSystem Plannerとレイアウト実装の工程をシームレスに柔軟に切り替えることが可能です。ダイのフロアプランやbump、TSV、I/O pad、ハードマクロの変更に伴い、System PlannerのデータをInnovusへ反映させたりInnovusのデータをSystem Plannerへ反映させたりすることで、積層した全てのデバイスのデータを常に同期させることが出来ます。

図3:システムレベル設計におけるデバイス積層のプランニング

Integrity Database

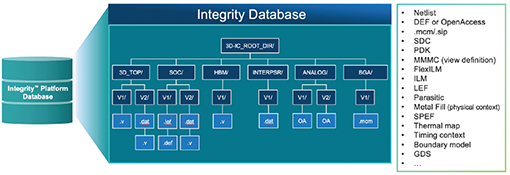

Integrity 3D-ICの中心的な役割を果たす機能として、複数のテクノロジを扱う共通の階層データベースがあります。このデータベースは異なるテクノロジ・ノードに属する様々なテクノロジ・データの読み込みをサポートしています。それぞれの3D-ICに含まれるデザイン・データは、このデータベースの単一のディレクトリ以下に整理して保存されます(図4)。

ユーザは、Tclで実装されたコマンドによってこのデータベースを操作することができ、データの読み込み、書き込み、更新、表示を簡単に行うことができます。また、このデータベースはInnovusの階層データベースを拡張したものなので、デジタル・ダイそれ自身が階層設計データであるようなケースもサポートしています。

図4:Integrity Databaseの構成

独自の3D-IC実装フロー

Integrity 3D-ICでは、2Dのデザインのネットリストを複数の階層からなる3Dのデザインに自動的に分解することで、2Dの平坦な単一ダイのデザインに対し、ダイを3Dに積層したデザインがどれほどPPAの優位性を持つかを探索することが可能です。

現在の3D-IC設計においては、ロジック・ダイの上にメモリ・ダイをマウントする形式の3D積層が普及しつつあります。Integrity 3D-ICでは、Innovus独自のMixed Placement技術を活かし、2Dデザインからメモリ・マクロを抽出してデザインを自動的に分割し、スタンダード・セルのロジックを含んだ下層のロジック・ダイと上層のメモリ・ダイからなる2層のデザインを実装することができます(図5)。その際にテスト用論理など一部のロジックをメモリと同じダイに置かなければならないケースも考えられるため、マクロとロジックのブロックを選択的に各階層へ割り当てるユーザ制御もサポートしています。このフローでは、タイミングを考慮した完全な配置済みの積層デザインを実現するため、3D Mixed Placementや自動的なbumpアサイン、および多階層デザインへの物理的展開などが行われます。その後、通常の配置配線フローと同様に、CTSや配線、最適化といった標準的な工程を進めることで、3D-ICの実装を最後まで実施することが可能です。

図5:メモリ・オン・ロジックのデザインにおける3D積層のイメージ

アナログ回路やパッケージ・レイアウトとの協調設計

アナログ回路やRF回路の実装においては、Cadenceのアナログ設計環境Virtuosoが主要なプラットフォームとなります。Integrity 3D-ICでは、System Plannerを通してVirtuosoとのインターフェースを行うことができます。Integrity 3D-ICにおいては、Virtuosoで設計したデザインのbumpに関する情報を参照することが可能となっており、対向するダイで最適な位置に接続用のbumpを作成することが出来ます。OpenAccessを介した既存のインターフェース機能を有効に活用して、VirtuosoとIntegrity 3D-IC間のデータのやり取りを実現しています。

ICパッケージ設計は、シリコン-パッケージ-ボードの設計フローにおいて重要な工程の1つです。Cadenceのパッケージ設計環境Allegroは、PCBや複雑なパッケージ実装のための完全かつスケーラブルな技術を提供しています。CadenceのICパッケージ設計技術により、プロジェクトの短期スケジュール内でコストや性能を改善するため、単一または複数のダイからなる複雑なワイヤ・ボンドやフリップ・チップのデザインを最適化することが可能です。このAllegroからIntegrity 3D-ICにパッケージのデータベースを直接インポートし、インターポーザや基板とbumpとの接続に利用することができます。このことによって、パッケージの設計工程が大幅に簡略化され、単一の設計環境でシステム全体を考慮しながらパッケージの協調設計を行うことが可能になります。

Flow Managerによる早期デザイン解析やサインオフ解析

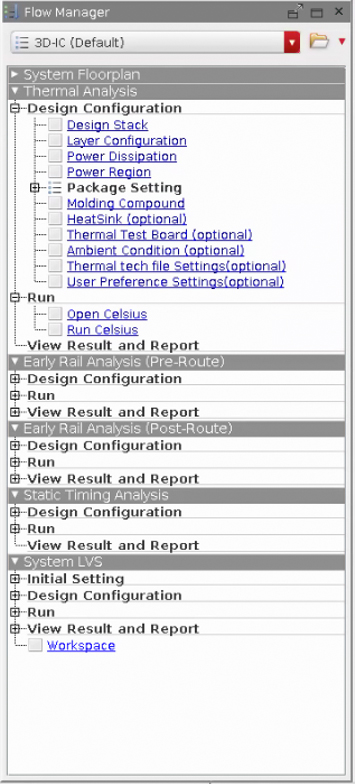

3D-ICシステムの開発においては、システムレベル設計へのフィードバックを行いアーキテクチャの改善を行うための、効率的なデザイン解析が重要な鍵となります。3D-ICの解析では、スタティック・タイミング解析や電力解析、エレクトロマイグレーション解析、IR Drop解析、物理検証などの標準的な解析に加えてさらに、熱解析や反りに対する機械的応力解析を含む追加の解析が必要になります。Integrity 3D-ICでは、これらの3次元に関連する様々な解析のセットアップをガイドするための、Flow Managerという機能を備えています。システムのフロアプランを完了しデザインを実装した後に、Flow Managerにおいて、利用可能な解析項目のリストを確認することができます(図6)。

図6:Flow Manager

Celsius Thermal Solverによる熱解析ソリューション

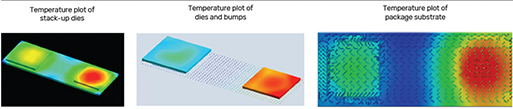

3D-ICデザインの性能は、その3D-ICのコンポーネントにおける熱挙動や温度分布に依存します。Cadenceの熱解析ツールCelsius™ Thermal Solverは、積層したダイやICパッケージ、PCBにおける熱の問題を高速かつ正確に特定するための、あらゆる点の熱解析を可能にします(図7)。そこには複雑なソリッド構造における過渡状態および定常状態の熱伝導を解析するためのFinite Element Analysis (FEA)フィールド・ソルバが含まれており、対流熱伝達と放射熱伝達の解析のための数値流体力学(CFD)エンジンを活用しています。この3D向けFEAフィールド・ソルバによって、bumpやボンディング・ワイヤ、PCBへのコネクタを含む複雑なパッケージのような、任意の3D構造の正確な熱伝導解析やシミュレーションが可能になります。

図7:Celsius Thermal Solverによる熱解析の例

VoltusによるEarly Rail Analysis

3D-IC設計において、各ダイに跨り電流を供給する電源供給配線網は最も重要なポイントの1つです。3D-ICデザインの性能は、複数のダイに跨る電源の割り当てや分配、およびIR Dropの効果に著しく依存します。Integrity 3D-ICではCadenceのVoltus™ Power Integrity Solutionの機能を利用可能であり、3D-ICデザインのEarly Rail Analysis (ERA)を実施する機能を備えています。このVoltusは、チップの電源供給配線網や電源グリッドに対する正確で高速、かつ高機能な解析および最適化の技術を提供する、フルチップのサインオフ向けのセルレベル電力解析ツールです。Voltusは、2.5Dインターポーザや3D-ICにおけるチップ-パッケージ-ボードのトータル電力のサインオフ解析のため、CadenceのSigrity™ XtractIM™やSigrity PowerDC™と緊密に統合されています。

Quantus/Tempusによる複数ダイのSTAソリューション

3D-ICデザインでは、各ダイのタイミングをクローズすることと同時に、ダイを跨るタイミング・パスをクローズすることも重要となります。ダイを積層することで、インターコネクトの距離は短くなりますが、RC抽出時のTSVやマイクロバンプを介した3D-IC構造のモデリングが複雑となります。RC抽出ツールQuantus™は、全ての3D-IC構造をモデル化し、複数プロセスに対応したTechnology Fileを用いてSPEFを生成するように改善されています。生成されたSPEFを用いて、STAツール Tempus™は、独自の分散処理とクラウド機能を備えたStaticタイミング解析機能で高速に複数ダイの解析を実施します。3D-ICデザインでは、正確なタイミング解析を行うために、様々なプロセスによるRCコーナー条件を考慮し、プロセスの変動を完全にカバーしタイミングを保証する必要があります。Tempusは、ダイのモデル生成やサインオフコーナーを削減するための特別な技術を用いて、設計パフォーマンスを犠牲にすることなく、正確な解析を行い、タイミング・クローズを促進します。

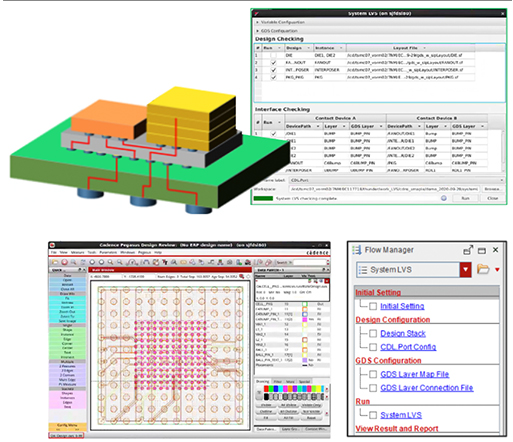

Pegasusによるダイ間の接続、DRC検証

積層したダイまたはインターポーザを備えたマルチ・チップレット・システムでは、デザイン・クロージャに必須なダイ間の接続性とデザイン・ルール・チェック(DRC)が重要となります。Integrity 3D-ICには、物理検証ツール Pegasus™の柔軟なクラウド対応プラットフォームが組み込まれており、システムレベルのルールデッキを準備しない状態でマルチ・チップレット接続の物理検証が可能です(図8)。

図8:物理検証の例

Pegasusでは、GUIを介してバンプ・アラインメントとシステムレベルの接続性をチェックでき、インタラクティブなGDSビューアを用いて違反箇所の検証と解析が可能です。Integrity 3D-ICとPegasusのネイティブな統合により、3D設計フローにおける物理検証の要件が保証されます。

システム主導のPPA最適化

Integrity 3D-ICによる設計の差別化の鍵となるポイントの1つは、あらゆるシステムレベル解析ツールからの早期のフィードバックです。システムのプランニングや実装にフィードバックすることで、2.5D構成におけるチップレットの位置の改善や、2.5D/3D構成におけるダイの選択の改善に繋がる可能性があります。最も重要な点は、それが消費電力やセル密度、タイミング最適化に影響するという点です。例えば、電力密度に基づく正確な電熱解析のフィードバックが得られた場合、システムの設計者は、同時にスイッチングする複数のモジュールがお互いに重なり積層されないよう、フロアプランを変更することができます。またタイミング解析の早期のフィードバックにより、各ダイで必要な最適化を再考することも可能です。システムレベル解析の有益な情報を適切な工程へフィードバックすることで、個々のチップレットに対して必要以上のコストやマージンをかけた設計を避けることが可能です。

まとめ

CadenceのIntegrity 3D-ICは、2.5Dや3D-ICに関するプランニングや実装、さらにサインオフ解析・検証を1つのコックピットから行うことができる、業界初めての統合ソリューションです。このIntegrity 3D-ICは、デジタルやアナログおよびパッケージの実装・サインオフ解析において業界をリードするCadenceの技術を、一元化された階層データベースを通して活用するものとなっています。Integrity 3D-ICによって、プランニングや実装フローの早期においてシステム解析や物理検証のフィードバックを可能にし、3D-ICの個々のチップレットに過剰なコストやマージンをかける設計を避けながら、システム主導のPPA最適化を可能にします。

本稿で紹介いたしましたIntegrity 3D-ICに関しては、2022年7月15日(金)に横浜ベイホテル東急(B2F)にて開催予定のCadenceLIVE Japan 2022にてユーザ様の事例紹介を予定しております。CadenceLIVE Japanではその他にも、ケイデンスの様々な最新技術情報や、ユーザ様の最新事例発表をご聴講いただけます。是非奮ってご参加いただけますようお願いいたします。 本イベントの詳細につきましては、日本ケイデンスのホームページにアクセスのうえ、「セミナー/イベント」よりCadenceLIVE Japan 2022のページをご参照ください。

フィールドエンジニアリング&サービス本部

デジタル&サインオフ

髙田 大河

Latest Issue

- 新製品Fidelity CFD : CFDの可能性を解き放つ

- Quantus FS (Field Solver) 最新機能のご紹介

- Cadence Online Support (COS) サイトで字幕付きのビデオがリリースされました。

- Cadence Topics: CadenceLIVE Japan 2022開催!

- 革新的なマシンラーニングベースの設計システム製品Cerebrus Intelligent Chip Explorer

- 自動運転シミュレーションができる車載向けエッジAIの自動ハードウェア設計・検証環境

- Cadence AWR Design Environmentの進歩

- PCBデザイン管理環境Allegro Pulseを利用することで本領発揮するAllegro System Capture

- Allegro In-Design AnalysisにSigrity PowerSI/Clarity 3D Solverを統合

- サインオフDRC/LVS/FILLをインプリ全体で適用し圧倒的な設計期間短縮を可能にするPegasus Signoff Verify Design Flowの紹介

- RC抽出ツールQuantusのもう一つの機能 ~ 基板ノイズ解析

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues