RF/マイクロ波設計のための新しいCadenceの統合ソリューション-機能拡張と効率化

自動車や産業用のIoTアプリケーションから消費者向け製品や医療機器に至るまで、今日、事実上すべてのインテリジェントシステムは、何らかの形の通信と無線センシングを採用しています。これらのシステムの多くは、ビームステアリングアンテナやミリ波スペクトラムなどの技術革新を採用して、システムの範囲、帯域幅、データレートを向上させています。一方、大規模な商用展開の場合、これらのシステムの部品は、小型化と統合を通じて、積極的なサイズ、重量、および価格の目標を達成する必要があります。そのため、エンジニアは、これらの追加の製品要件とともに高いレベルの性能を実現するRF IPを提供するという大きなプレッシャーにさらされています。これらの要件を満たすには、チップ、パッケージ、ボード全体で信頼性の高い解析および分析データを提供でき、設計から製造向けのレイアウトとサインオフまで、製品開発のすべての製造前段階に対応した電子設計ツールを使用する必要があります。

この記事では、Cadence® AWR Design Environment®プラットフォームとその他のCadence 製品間の効率的で堅牢なワークフローをサポートするCadenceの新機能に焦点を当てます。

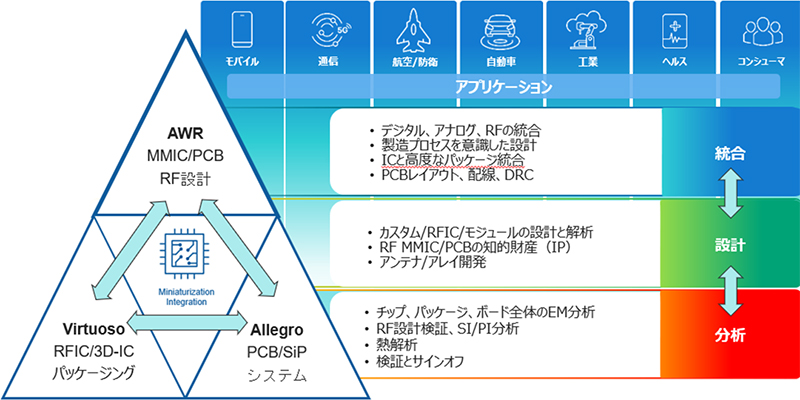

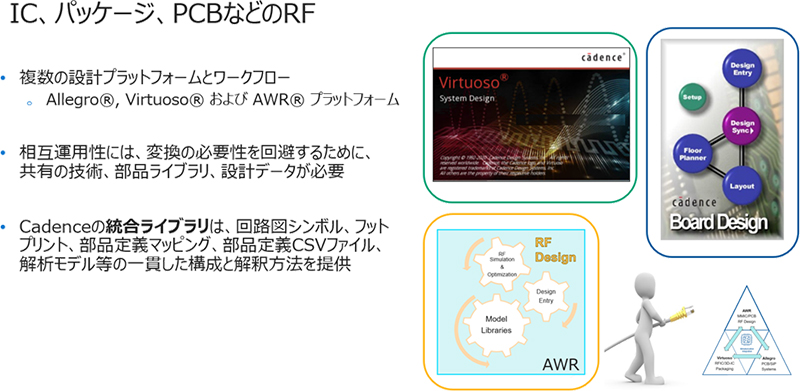

図1. RF設計をサポートするPCBおよびクロスファブリックシステム

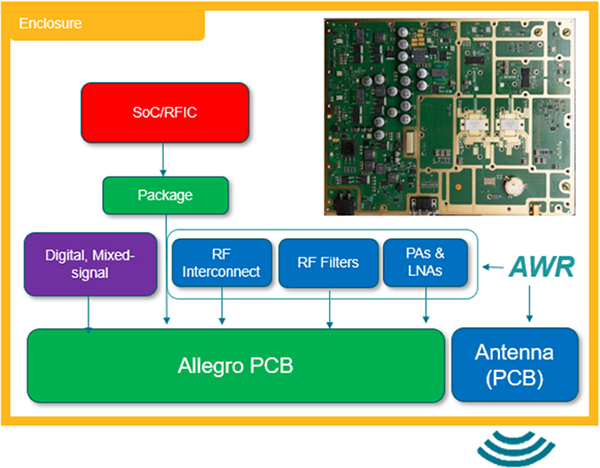

基地局、モバイルデバイス、またはレーダー等むけのPCBに実装されるシステムの場合、RF部分としては、モジュールに統合されていたり、PCB上で直接設計されたり、ディスクリート表面実装部品としてパワーアンプ、ローノイズアンプ、フィルタ、アンテナなどが実装されていたりします。設計の観点から、これらのRF部分は、特殊な分析を使用して開発されています。図2では無線機器の簡略化されたブロック図を示しており、全体を表す黄色の枠の中で様々な色の部分があります。これらの色は機器の中で様々なツールが利用されて製品が開発されていることが分かります。またPCB(Allegro® PCBを記載の有る所)は、複数の設計プラットフォームで開発されたすべての電子部品を組み込むための基板を提供しています。システムの統合とPCBレイアウトのチームにとっての課題は、さまざまなツールから設計IPを取得し、それらをPCBレイアウトツールに効率的かつ正確に取り込むことです。

図2. 無線部分の簡略化されたブロック図

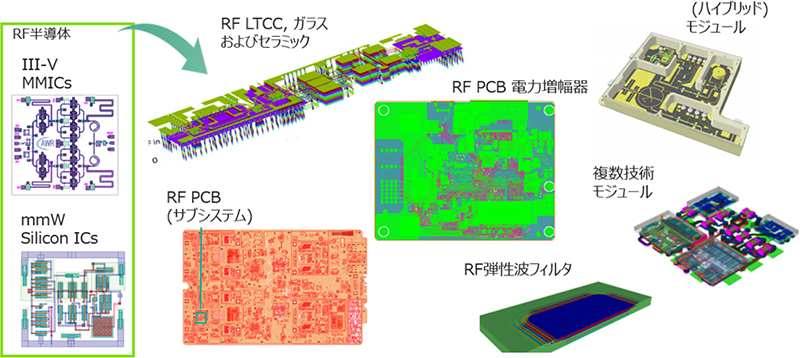

RF/マイクロ波の設計と高速電子機器は、どちらも回路の物理的なレイアウトに非常に影響を受けやすいという点で類似しています。高速設計ではレイアウト後に電磁界解析を使用してシグナルインテグリティを調査します。伝送線路の長さと幅は、部品間のインピーダンス値が得られるように制御されます。これらは、増幅器の性能に影響を与えますし、分布定数型の受動デバイスになります。 そのため、Microwave Office®などのRF設計ツールは、基板の電気的な情報が組み込まれた分布定数伝送線路エレメントの包括的なライブラリを使用して、回路図とレイアウトの設計入力を同時にサポートします。レイアウトの影響を考慮しながら、様々な技術分野で、システムのサイズ、コスト、および性能の懸念に対処しています。

図3. 様々な技術を利用したRF/マイクロ波設計

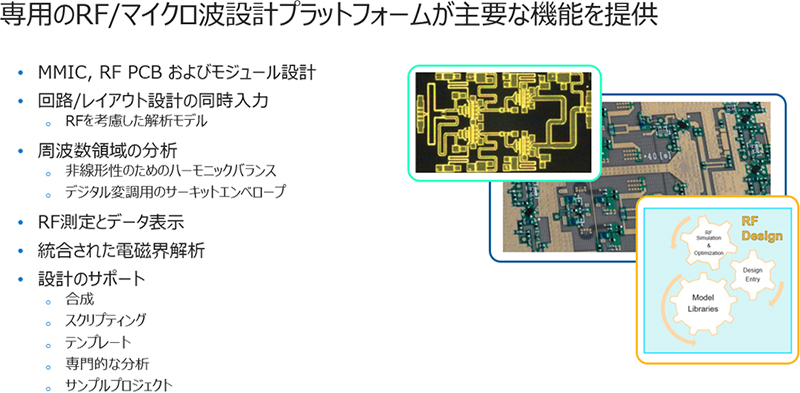

RF向けの設計ソフトウェアは、回路図とレイアウト設計の同時入力に加えて、特殊な周波数領域での回路分析機能を提供して、システム全体の性能に関係するRF動作を解析します。解析は、Microwave Officeの強力な最適化技術と組み合わせて、RF IPが最高の全体的な回路性能を提供し、システムインテグレータによって指定された部品要件を満たすことを確実にします。

Cadence AWR Design Environmentは、回路設計とレイアウト設計の同時入力、および設計者がRF性能を解析、プロット、および最適化できるようにする特殊なRF解析機能を含む統合されたRF設計プラットフォームです。さらに、このプラットフォームは、電磁界解析機能を設計環境内に統合しており、重要な個所のSパラメータ抽出、回路/電磁界協調解析、および設計検証をサポートしています。このプラットフォーム内で、AWRソフトウェア製品は、無線フロントエンド部品の開発に使用される豊富なRF設計向けの機能と、RF IP開発のさまざまな段階を加速するのに役立つ多数の設計支援機能を提供しています。

図4. Microwave Officeを利用したRF IP開発

Cadence EDAソリューション全体で共有されるアーキテクチャ/データを活用し、Cadence AWR Design Environment のV16リリースでは、Microwave Officeソフトウェアから完成した回路設計とレイアウト設計の両方のIP設計を、回路設計のすべての構築ブロックが含まれている統合ライブラリ内のデータとしてVirtuoso®および/またはAllegroプラットフォームに渡す新しいRFワークフローを提供します。 これらのプラットフォーム間で信頼性の高い相互運用性を提供し、RF統合を可能にすることは、共有の技術とライブラリから始まり、回路図とレイアウトに広がります。Cadenceの統合ライブラリは、回路図シンボル、フットプリント、および回路図シンボルとフットプリント間の部品定義のマッピングを提供しています。さらに、統合ライブラリは、技術に依存しないレイアウトPcell、部品定義ファイル、および解析モデルをサポートしています。このワークフローにより、複数技術の統合において、貴重なエンジニアリングリソースを消費し、開発スケジュールに直接影響を与える設計ツール間のシステム統合のボトルネックを削減または排除します。

図5. チップ、パッケージ、ボード統合のためのクロスプラットフォーム設計

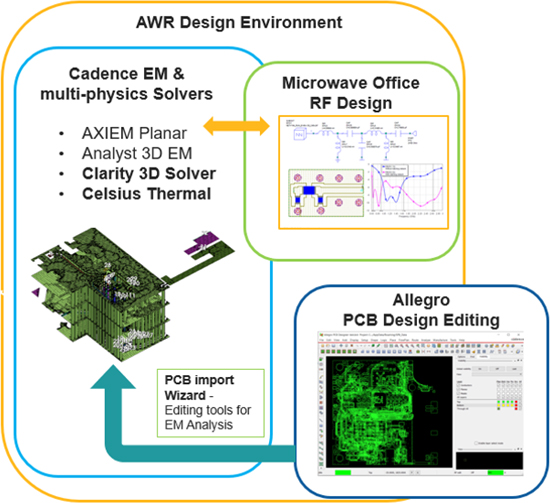

Cadence AWR Design EnvironmentのV16リリースではさらに、Clarity™3D SolverおよびCelsius™ Thermal Solverとのシームレスな統合が導入されました。大規模で複雑なRFシステムの電磁界解析や熱解析に強力で高機能の解析エンジンをCadence AWR Design Environmentで活用できます。またAllegroで設計したレイアウトを取り込んで、回路部品と組み合わせて解析を実行することも効率的に進めることが可能になりました。

図6. 様々な解析ソルバをCadence AWR Design Environmentで活用可能

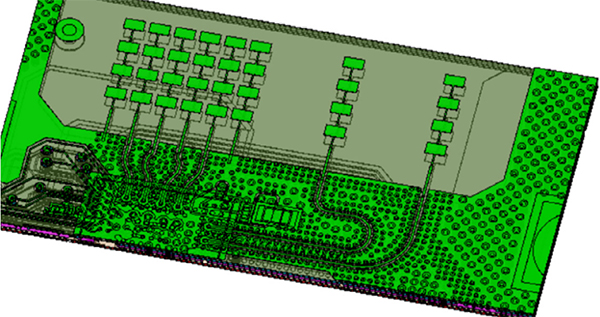

例えば、図7のようなフェーズドアレイアンテナと給電回路などの大規模なRF構造は、多くの計算のためのリソースが必要になるため、手動で小さな構造に分割されることがよくあります。重要な相互接続、RFIC/MMIC、モジュール、PCBの設計に使用されるClarity 3D Solver 3D EMシミュレータは、Cadenceの優れた分散マルチ処理技術を活用しており、実質的に無制限の規模と10倍の速度を提供できます。これにより、従来の電磁界解析ソフトウェアの制限を克服し、より効率的かつ精度の高い解析を可能にします。

図7. 自動車のレーダー向け77GHzアンテナアレー

現在AWRソフトウェアに統合されているClarity 3D Solverは、RF設計者に、AXIEM 3D平面およびAnalyst 3D有限要素法(FEM)ソルバで解析可能な規模を超えて、大規模で複雑なRF/ミックスドシグナルシステムの設計検証やサインオフのために、大規模の電磁界解析を可能にします。Clarity 3D SolverとMicrowave Officeソフトウェアの統合は、完全にCadence AWR Design Environmentで自動化されたプロセスです。つまり、他の電磁界解析エンジンと同様に、Microwave Officeで構造を解析することができ、Sパラメータ、メッシュ、電流、およびフィールドの視覚化、回路解析との協調解析などのMicrowave Officeソフトウェアにすでに存在する豊富な機能を最大限に活用できます。

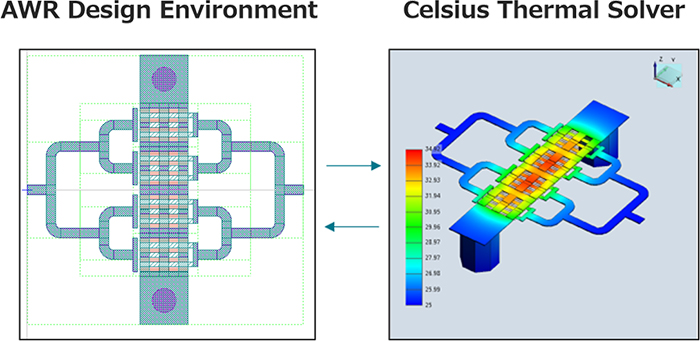

ICおよび電子システム企業、特にICパッケージングや複数技術のモジュールを組み込む企業は、設計後期での設計変更を引き起こし、プロジェクトのスケジュールを狂わせる可能性のある途方もない熱の課題に直面しています。Microwave Officeソフトウェアに組み込まれたCelsius Thermal Solverは、RF PAおよびMMIC設計、RF PCB、およびモジュールのためのソリューション(図8)を提供し、既存のMMIC(ダイまたはパッケージ化されたデバイス)の設計データや、レイアウト、材料情報のような構造、RF解析における電力源の値を含むMicrowave Officeソフトウェアのプロジェクトから得られるモデル情報を通して電熱解析をサポートします。

図8. Cadence AWR Design EnvironmentとCelsius Thermal Solverの連携

2020年1月にAWR製品はCadenceの一員となり、それ以来、Cadenceのソフトウェアとの連携によるシステムの設計向けのソリューションの開発を継続してきました。本記事では連携の状況、目的、お客様にご提供できる価値について説明を致しました。今後も製品自体の改善と合わせて、ツールを組み合わせた新しい価値の創造を継続いたします。今後の開発にご期待頂けましたら幸いです。

参考

システム セールス チーム プリンシパル アプリケーション エンジニア

菅原 努

Latest Issue

- 次世代仮想プラットフォーム Helium Virtual and Hybrid Studio 最先端のテクノロジとケイデンス検証プラットフォームとの融合

- FMEDAベースの機能安全開発ソリューションCadence Midas Safety Platform

- Xcelium ML: ツールの中の黒帯検証エンジニア

- プリント基板設計ツールAllegro/OrCAD:SPB17.4-2019 QIR3 最新機能の一部をご紹介

- 基板レイアウト設計者によるスクリーニング・チェック Allegro In-Design Analysis

- Electro-Static Discharge: The Silent Killer Voltus ESD解析:大規模デザインに対応し、高速な検証エンジンと使い勝手の良い解析環境を提供するESD検証環境

- ケイデンス・ソフトウェア・ダウンロードサイトが一新しました

- Cadence Topics

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues