基板レイアウト設計者によるスクリーニング・チェック

Allegro In-Design Analysis

設計サイクルがますます短くなっている今日、高速信号の基板設計にSignal Integrity解析は欠かせません。そのため、シミュレーションは、設計サイクルに不可欠な要素となり、配線の問題をできるだけ早期に発見して修正することが必須となっております。基板レイアウトの初期段階から解析エンジニアに頼っていた場合、そのリソースは逼迫し、解析工数の増大につながります。そこで、Allegro® PCB Editorを使用している基板レイアウト設計者は、解析向けの複雑なルールを理解していなくても、Workflow Managerを介して、Signal Integrityで問題となる箇所のスクリーニング・チェックを行うことができ、その結果をAllegro PCB Editorキャンバス上で表示することができます。

設計サイクルがますます短くなっている今日、高速信号の基板設計にSignal Integrity解析は欠かせません。そのため、シミュレーションは、設計サイクルに不可欠な要素となり、配線の問題をできるだけ早期に発見して修正することが必須となっております。基板レイアウトの初期段階から解析エンジニアに頼っていた場合、そのリソースは逼迫し、解析工数の増大につながります。そこで、Allegro® PCB Editorを使用している基板レイアウト設計者は、解析向けの複雑なルールを理解していなくても、Workflow Managerを介して、Signal Integrityで問題となる箇所のスクリーニング・チェックを行うことができ、その結果をAllegro PCB Editorキャンバス上で表示することができます。

基板レイアウト設計者向けスクリーニング・チェックは、以下の3つになります。

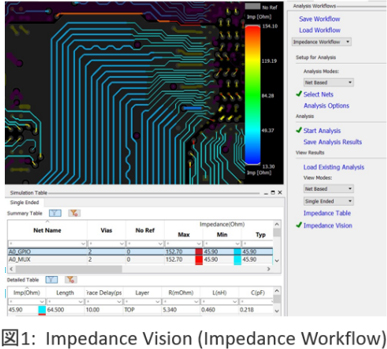

特性インピーダンスのスクリーニング・チェック(Impedanceワークフロー)

このチェックでは、配線トレースの特性インピーダンスをチェックします。

このチェックでは、配線トレースの特性インピーダンスをチェックします。

たとえば、グランドプレーンのギャップを通過するインピーダンス不連続部分をもつ信号を検出できます。

図1は、DDR信号バスの特性インピーダンスのスクリーニングを行った例になります。メモリからの引き出しが細い配線やリファレンスが取れていない等の理由により、特性インピーダンスが不連続になっています。これにより、大きな反射ノイズが発生するため信号の安定化のためには、この影響を極力排除する必要があります。また、基板レイアウト設計者が意図せずリファレンスの存在しない、特性インピーダンスが不連続になってしまうネットまたはセグメントも識別するために、問題のある箇所を素早く特定して基板を修正できます。

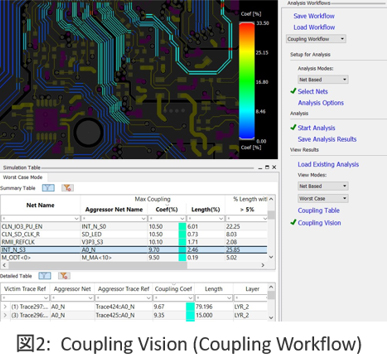

配線カップリングのスクリーニング・チェック(Couplingワークフロー)

このチェックでは、配線トレース間の結合をチェックします。

このチェックでは、配線トレース間の結合をチェックします。

この結合が最小限に抑えられることで、ドライバとレシーバーのクロストーク問題を防止できます。

図2のAllegro PCB Editorキャンバスに赤く表示されている配線間の結合係数は、クロストークの問題になります。基板レイアウト設計者は、この対象部分の配線間隔を広げる等の基板を修正することで、クロストークを最小限に抑えることができます。

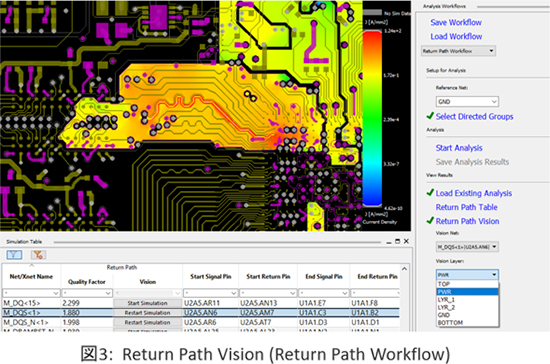

リターンパスのスクリーニング・チェック(Return Pathワークフロー)

リターンパスの問題の可能性があるネットを報告し、リターンパス品質係数を示します。

リターンパスが不十分な場合、Signal Integrity問題が発生する可能性があります。基板レイアウト設計者は、品質係数の悪い信号のリターン電流を視覚化し、基板の修正箇所を認識することで問題を解決できます。このチェックを実行するには、Sigrity® Auroraライセンスが必要となります。

図3では、赤く強調表示された信号は、電源層の真上に配線されていました。グランドプレーンに到達するには、リターン電流が基板のL5層に流れる必要があります。そのため、視覚化を使用し、配線下の電源層にグランドパッチを配置することにより、リターンパス品質係数がほぼ2倍向上します。

Allegro PCB Editor には、その他SI/PI解析エンジニア向けの解析機能も用意しております。(以下参照)

これらの結果も同様にAllegro PCB Editorキャンバス上で表示することができます。

- Fundamental SI Analysis ※

- Crosstalk ワークフロー(クロストーク)

- Reflection ワークフロー(反射解析)

- Topology Extraction ワークフロー (トポロジーベースのSI解析)

- Fundamental PI Analysis ※

- IR drop Analysis ワークフロー(IRドロップ解析)

※上記のワークフロー解析を実行するには、Sigrity Auroraライセンスが必要となります。

本稿では、基板レイアウト設計者向けのAllegro PCB Editorスクリーニング・チェック機能をご紹介いたしました。基板レイアウト設計者が、基板レイアウトの初期段階においてスクリーニングすることで、ノイズの少ない基板を設計することができ、解析エンジニアの作業工数を大幅に削減することが可能となります。

今回、ご紹介の内容に関しましてお問い合わせがございましたら、貴社担当営業、あるいはメール: [email protected]へご連絡ください。

カスタム&システムグループ マルチフィジックス・システム解析チーム

森谷 卓矢

Latest Issue

- 次世代仮想プラットフォーム Helium Virtual and Hybrid Studio 最先端のテクノロジとケイデンス検証プラットフォームとの融合

- FMEDAベースの機能安全開発ソリューションCadence Midas Safety Platform

- Xcelium ML: ツールの中の黒帯検証エンジニア

- プリント基板設計ツールAllegro/OrCAD:SPB17.4-2019 QIR3 最新機能の一部をご紹介

- RF/マイクロ波設計のための新しいCadenceの統合ソリューション-機能拡張と効率化

- Electro-Static Discharge: The Silent Killer Voltus ESD解析:大規模デザインに対応し、高速な検証エンジンと使い勝手の良い解析環境を提供するESD検証環境

- ケイデンス・ソフトウェア・ダウンロードサイトが一新しました

- Cadence Topics

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues