FMEDAベースの機能安全開発ソリューションCadence Midas Safety Platform

2021年9月20日に、「ケイデンス、車載および産業用機器設計に向けた認証取得を加速する包括的な機能安全ソリューションを発表」のプレスリリースを発表させていただきました。

このプレスリリース内では、ISO 26262やIEC 61508に準拠した製品開発を進める上での強力なソリューションとしてCadence® Midas™ Safety Platformがアナウンスされています。このMidas(まいだす)とはいったい何者なのでしょうか?一言で簡単に言ってしまいますと、LSI/ICの機能安全で悩める方への福音となるソリューションです。

自動車に代表されるような、長期間にわたって使用され、かつ使い方によっては人命にも関わるような機器において、製造後の経時劣化よる故障によって危険な状況になることも避けることが求められます。例えば自動車であればISO26262、産業機器であればICE61508のような標準によって、このような危険を避けるための方法が定義されています。ISO26262とその基本概念となる機能安全の考え方については、バックナンバーVolume 27, July 2018の「車載電子システム向け機能安全メソドロジ」の記事をご覧いただければと思いますが、これらの標準では安全の度合いについて、システマティックにかつ定量的に評価することが求められます。そのシステマティックかつ定量的に評価をするツールとして、FMEDA(Failure Modes Effects and Diagnostics Analysis)があります。FMEDAは、ざっくりした言い方をしてしまうと、故障の発生確率と故障の影響から、安全と見てよい故障か危険な故障かを分析し、安全の度合いを数値として定量的に示す手法です。このFMEDAは、いろいろなレベルで、例えば、車全体が対象であったり、その一部である例えばADASシステムが対象であったり、さらにADASシステムの部品であるLSI/ICを対象として使用されたりします。このなかで、LSI/ICのFMEDAをやろうと思われている方には残念なお知らせがあります。以前の記事、Volume 30, July 2019 「ISO26262第2版と半導体における機能安全」で書きましたように、たとえばADASシステムであれば、そこで使用している抵抗器やコンデンサなどの部品については、その故障の発生確率などのFMEDAに必要な情報はSN 29500やIEC 61709などの各種データハンドブックに書かれています。その一方、LSI/ICでは、その中身であるサブモジュールについてのデータは、ユーザが独自に定義/算出する必要があります。悲しいことに、この手間は膨大なものです。

FMEDAを軸に機能安全解析を行う必要がある、しかしLSI/ICのFMEDAは大変な手間である。やらないという選択肢がない以上、どれだけ楽にできるかがポイントとなります。長々とした前書きになってしましましたが、10月20日に発表したケイデンスの新機能安全ソリューションであるCadence Midas Safety Platformは、この悩みを解消するソリューションです。

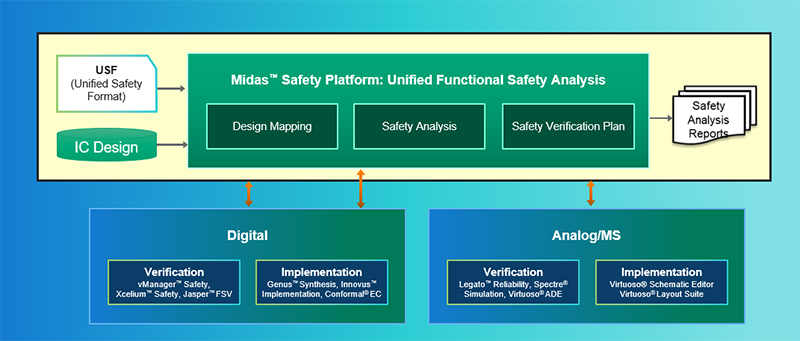

Midasの基本的な考え方は、機能安全、特にFMEDAを行うにあたって必要とされるツールを有機的に接続し、それらのツール間での機能安全に関するデータのやり取りを行えるようにすることです。図1に、Midasの構造を示します。トップにMidasがあり、Midasをハブとして各種ツール群、例えばデジタル機能安全検証のためのvManager™ Safety、Xcelium™ Safety、Jasper™ Functional Safety Verification (FSV) Appや、デジタル機能安全設計のためのGenus™ Synthesis、Innovus™ Implementation、Conformal® Equivalence Checker、そしてアナログ機能安全検証のLegato™ Reliability 、Spectre® Simulation等を双方向接続したプラットフォームとなっています。

図1:Midas Safety Platform

このツール間での機能安全に関するデータのやり取りを行えるようにするという考え方は、SystemCやUVM、IP-XACT,、SCE-MI2.4など数々のEDAおよびIPでの標準化で知られるAccelleraでの、機能安全におけるデータ互換性やトレーサビリティの確保のための標準化のワーキンググループFunctional Safety working group で提唱されています。ケイデンスはこのワーキンググループに積極的に関与して標準化を進めていますが、このワーキンググループの提唱するコンセプトをいち早く実際に使用できる形にしたものがMidasであると言えるでしょう。

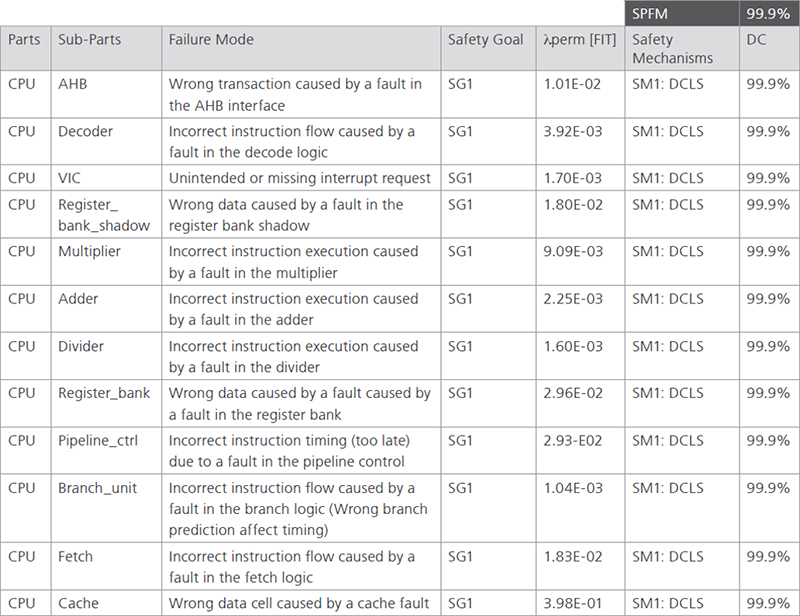

話を元に戻して、Midasを活用してFMEDAを行うと、どのようなよいことがあるのでしょうか?図2に簡単なFMEDAの例を示します。このFMEDAシートを見ると多種多様な情報を記載することが必要であることがわかるかと思います。例えば、PartおよびSub-Part(左側2列)としてのデザインの構造や、FIT(Failure In Time:稼働10億(109)時間あたりの平均故障回数:右から3列目)、DC(Diagnostic Coverage:右から1列目)を記載することが必要です。

図2:FMEDAの例

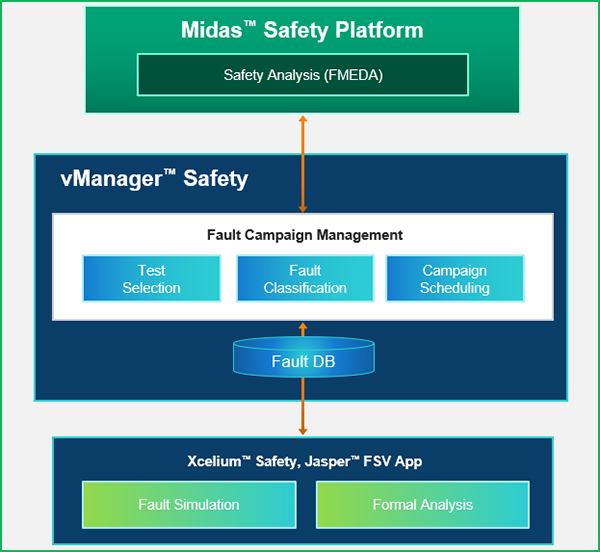

例えば、DCについて考えてみます。日本語ではよく診断カバレッジとも呼ばれるこの尺度ですが、ASIL-CやDをターゲットとする設計では、故障注入シミュレーションにより厳密に数値化すること(例えば、後述するSPFMを算出すること)が求められています。故障注入シミュレータであるXcelium Safetyに加え、故障リストの削減や診断カバレッジホールの解析にJasper FSV Appを、そして機能安全検証キャンペーンの管理にvManager Safetyを組み合わせたデジタル機能安全検証フローを今までもご提案してきましたが、このようなフローの上にMidasを置くことで(図3)、Sub-Partおよびfailure mode毎に算出するDCの項目を、先のデジタル機能安全検証フローをMidasから管理し項目ごとに埋めていくことが自動化できます。そして、これらの数値をもとにFMEDAを行うことによって、SPFM(Single Point Fault Metric::表右上)のようなISO26262で求められる定量的な機能安全達成度を自動的に算出することができます。これは、人手による記載漏れや記載ミスのようなポカミスを防ぎ品質向上に寄与するだけでなく、記載が正しいかどうかのレビューやそのエビデンス作成の手間も減らして工数削減が(もちろん、それに対しての精神的負荷削減も)可能となります。

図3:デジタル機能安全検証

デジタル部分のDC算出をこのように効率化できるだけでなく、アナログ部分の機能安全検証フローを接続することで、同様の成果を得られることは言うまでもありません。

また、PartおよびSub-Partとしてのデザインの構造については、論理合成ソリューションであるGenusと接続すれば、論理合成にてそのようなデザイン構造を保持していますから、その情報をMidasにあげることで、先のFMEDAシートの作成を大幅に省力化することができます。さらに、FITを算出するとき、同じテクノロジ、同じ条件下であれば、ゲート数が多くなれば故障確率も上がることから、Genusより、合成後のそれぞれのSub-Partのゲート数情報を取得し、その情報からFIT値を計算することが可能となります。このように、FMEDAを行う上で、それぞれのツールがそれぞれ独立して持っている情報を、Midasで統合・有機的にやり取りすることができるようにすることで、FMEDA作成の効率が大きく向上します。

FMEDAはしなくてはいけない、でもその手間考えると気が重い、という機能安全エンジニアの方々には、その心労を少しでも減らす手段として、Midasは是非ともお勧めしたいプラットフォームです。

テクノロジーセールスリード システム&ベリフィケーション

後藤 謙治

Latest Issue

- 次世代仮想プラットフォーム Helium Virtual and Hybrid Studio 最先端のテクノロジとケイデンス検証プラットフォームとの融合

- Xcelium ML: ツールの中の黒帯検証エンジニア

- プリント基板設計ツールAllegro/OrCAD:SPB17.4-2019 QIR3 最新機能の一部をご紹介

- 基板レイアウト設計者によるスクリーニング・チェック Allegro In-Design Analysis

- RF/マイクロ波設計のための新しいCadenceの統合ソリューション-機能拡張と効率化

- Electro-Static Discharge: The Silent Killer Voltus ESD解析:大規模デザインに対応し、高速な検証エンジンと使い勝手の良い解析環境を提供するESD検証環境

- ケイデンス・ソフトウェア・ダウンロードサイトが一新しました

- Cadence Topics

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues