今、なぜ、ケイデンスの次世代物理合成ツール Genus Physical Synthesis の躍進が著しいのか?

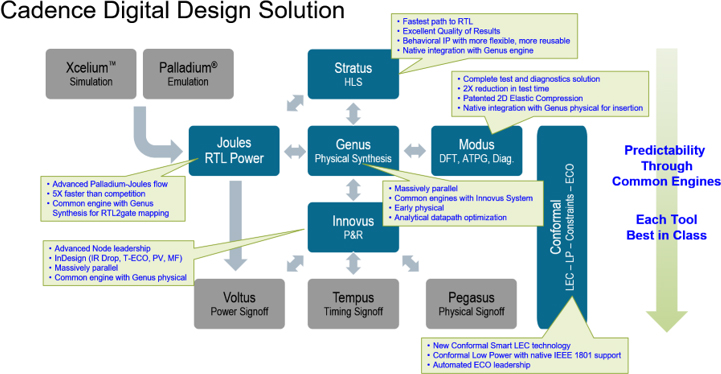

昨今の設計では 7nm/5nm プロセスノードが主流になりつつあり、今後 3nm 以降も徐々に需要の増加が見込まれます。ケイデンスのデジタル設計ツール群では、既に4年ほど前からRTL-to-GDSII のフルフローを提供してきており、最近の先端プロセスノードにおいては、合成、配置配線、サインオフ検証すべてにおいてケイデンスデジタル設計ツール群を使用したフルフロー適用事例が全世界で急増しています。次世代の物理合成ツール Genus™ Physical Synthesisは、配置配線ツールの Innovus™ Implementation System 、サインオフ検証ツール Tempus™ Timing Signoff Solution、DFT/ATPGツールの Modus DFT Software Solutionとともにケイデンスデジタル設計フローの中核をなすツールです。

Genus Physical の前後に位置するツールとしては、現在の P&R 業界で PPA をリードする Innovus、高位レベルのSystemC動作記述から高品質のRTLを早期に自動生成するStratus™ High-Level Synthesis、システムレベルのPalladium®/Xcelium™ Parallel Logic Simulationとリンクし RTL レベルのパワー解析をGenus の合成エンジンを用いて高精度に行える Joules™ RTL Power Solution、業界唯一の 2D Elastic Compression 技術によりテスト時間を大幅に削減する Modus、業界 No1 の高い信頼を得ているエンジンによるフロー全体の 等価性検証、Low Power検証を担う Conformal があります。個々のツールで優れた技術を提供しているのはもちろんですが、ケイデンスのデジタル設計フローの中心に位置する Genus Physical との密な連携により更なる付加価値を提供しています。

Stratus - Genus:

Stratus に Genus Physical が統合されています。SystemCを高位合成したRTLに対し早期にGenus Physical の配置により配線混雑を検出且つSystemC コードにフィードバックします。その結果を基に適切なSystemCコード修正もしくは高位合成制約の改善により配線混雑の早期解消を実現します。

Genus - Innovus:

Genus に Innovus が統合されている Genus Physical です。精度の高いレイアウト予測が可能なため、P&R との乖離のすくない物理合成が可能となり、設計のイタレーションを低減できます。今回のメイントピックです。

Genus - Joules:

Genus に Joules が統合されています。Genus では Joules の高性能なパワー解析エンジンを採用していますので、Switching Activity を入力した精度の高いパワー最適化が可能です。また Joules ライセンスを併用することで Joules のフル機能を Genus コックピット上で使用可能です。

Genus - Modus:

Genus Physical に Modus が統合されています。全ての DFT/テスト回路の実装は Genus コックピット上で1パスフローとして行われます。

Genus - Conformal:

Genus から Conformal の実行スクリプトが生成されます。合成時の設定等、検証に必要な設定はすべて含まれていますので、編集無しで実行することができます。

このように Genus はケイデンスデジタル設計フローのフロントエンドにおいて、フローで一貫したエンジンとしてメインのコックピットとなっています。

Genus が 2015 年にリリースされて以来、非常に多くのお客様が既存環境から Genus へ移行いただいてきましたが、特にここ最近、ユーザー数が顕著に増加しており、業界を一気に躍進しているその理由を紐解いていきたいと思います。

Genus をお使いいただいているお客様の最大の理由は PPA の向上です。PPAの向上に貢献している主な特長は次の通りです。

優れた合成アルゴリズム

最終結果を大きく左右する論理構造を重視した合成アルゴリズム(グローバルマッピング)が非常に優れています。与えられたターゲット PPA に対して回路全体の論理構造を適切に作り分けることができるため、取りうる解すべてを網羅的にチェックすることなく、高速に最適解を求めることができるように開発されています。

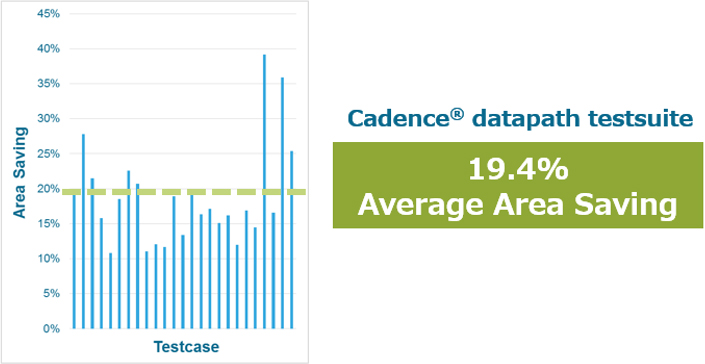

Analytical データパス最適化

従来のようにタイミングパス毎に個々の演算器単体でアーキテクチャを評価し選択するのではなく、論理コーン内の全演算器に対して演算器の組み合わせを考慮します。すべての組み合わせを網羅的にすべてチェックすることなく、高速に最適な組み合わせを決定できるように開発された次世代のデータパス最適化エンジンです。この機能により、従来エリアの大きな高速なアーキテクチャを必要としていた演算器も、エリアの小さな低速のアーキテクチャでも十分ターゲット周波数を達成できるケースが増え、最終的なエリアとパワーが削減できます。

配置に最適な論理構造

論理構造を決定する前にジェネリックセル(テクノロジマッピング前のセル)を配置することで、配置後の配線混雑や物理距離がタイミングに及ぼす影響を予測することができ、タイミングや配線混雑に最適な論理構造を構築することが可能です。 配線混雑が起きやすい回路構造に対しては配線混雑を低減する回路構造の構築、配置により距離が離れてしまうパスに対しては、物理距離によるタイミングの影響を考慮しタイミングに最適な回路構造を構築します。 従来ですと、配置後のクリティカルパスが低速な演算器アーキテクチャを含んでいたり、論理段数が長いまま残っていたり、配線混雑の原因を改善できない等、配置後では到底リカバーしきれない課題に苦労された方もいらっしゃると思います。Genus では最適化の自由度が高く PPA 改善効果の高い、合成処理の初期で配線混雑や長距離パスを予測することで配置後の品質を向上します。

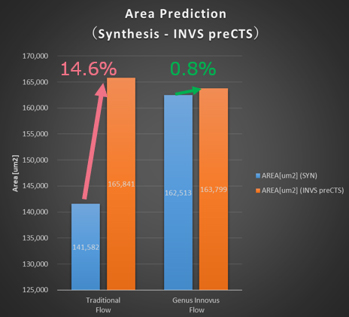

高いレイアウト相関性

合成結果でターゲットのチップサイズに収まる見込みであったにもかかわらず、レイアウトで面積が増加し、結局ターゲットサイズに収まらなかった、という事例は良く聞くケースです。合成とレイアウトで面積の相関が低いということになりますが、チップサイズや周波数がクリティカルな設計の場合には致命的な問題です。ある事例では合成とレイアウトで面積のGAPが約15%もあるケースもあり、結局レイアウトしてみないとターゲットサイズに収まるかどうかわからず、物理合成の意味を問われるお客様もいらっしゃいました。物理合成では高いレイアウトの予測性が求められています。Genus では P&R業界でPPAをリードする Innovus のエンジンを搭載しています。配置、概略配線、抽出、遅延計算、さらにはコマンドやGUIも共通で、ピンアクセスやlayer Promotionなど先端プロセスノード特有の技術に完全に対応しています。Innovus の配置結果が Genus の物理合成結果として確認ができるため、合成とレイアウトの乖離を最小にする物理合成が可能です。レイアウト結果を高い精度で予測可能となり、タイミングだけでなくAreaも高い相関結果を得られ、物理合成結果で性能判断が可能です。 チップサイズや周波数がクリティカルな設計の場合には特に有効です。

設計初期の物理合成を可能にする自動フロアプラン機能

レイアウト後にターゲットPPAが実現可能かどうかを設計の初期段階で確認できることは非常に重要です。特に設計の要求仕様を大きく外れる結果に対しては、システムメーカーやフロントエンド設計者が早期に対策できるようになることでASICベンダーやバックエンド設計者とのイタレーションを削減することにつながります。昨今の設計プロセスノードにおいては、物理距離依存の配線抵抗による遅延の差分が大きく、使用する配線層により抵抗値が大きく異なるため、合成でも配線層と距離を考慮する必要がありますが、設計初期には物理合成を実施するためのフロアプランが用意されていないケースもございます。Genusでは統合されているInnovusエンジンにより、フロアプランを自動生成することができるため、フロアプランがない状態からでも物理合成を進めることが可能です。

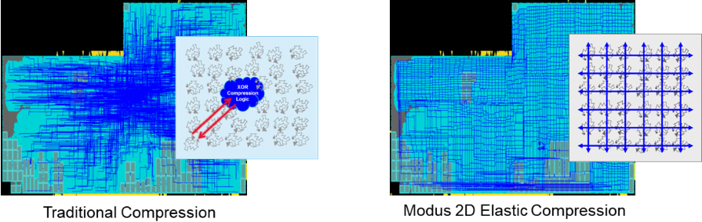

スキャンチェーンの圧縮回路による配線混雑を劇的に削減

ユーザー回路だけでなくDFTのテスト回路を含めた PPA 改善が可能です。スキャンチェーンの圧縮回路はデザインのすべてのスキャンチェーンと接続をもつため、圧縮回路を中心として配線が極端に集中し、配置配線におけるターゲットのチップサイズや PPA 達成のボトルネックになるケースもあります。Genus Physical に統合されている DFT ツールの Modus の 次世代の圧縮回路アーキテクチャ 2D Elastic 機能を使用すると、配置されたデザインに対して、圧縮回路をデザイン全体に格子状に発生させて、圧縮回路における配線集中を劇的に抑えることができます。これにより配線リソースを大幅に削減できるため、チップサイズ縮小に大きく貢献でき、さらに圧縮率を上げることによりテスト時間の大幅な短縮が実現できます。

また昨今の大規模化、複雑化していくデザインに対して開発されている、大規模に対応したキャパシティと処理時間もGenusを選んでいただく理由の1つになっています。

大規模対応を可能にする分散処理

同一筐体、ネットワーク分散の両方に対応しています。 分散処理は業界でも特に新しい機能ではありませんが、分散処理によりPPAが悪化したり、デザイン規模やCPU数が増加したときに分散効率が悪くなる等の分散処理特有の課題を Genus では解決するように開発されています。そのため大規模回路に対してもPPA品質を維持しながら処理時間を高速可能です。CPU 数に対して高いスケーラビリティをもつため、大規模回路に対しては CPU 数を増やすことで高速化が可能です。

Genus Physical は、コアの合成エンジンの優位性に加えて、ケイデンスデジタル設計フローツール群でエンジンの共有化など密に連携させることで、最大限の利点を提供するツールです。ケイデンスデジタル設計フローでは、RTL-to-GDSII フローの全ツールを共通設計環境でご利用いただける環境 Stylus としても提供しておりますので、是非設計の効率化にお役立ていただければと思います。

フィールドエンジニアリング&サービス本部

野原 秀公

Latest Issue

- Clarity 3D Solver Technology - 高精度+大規模なパフォーマンスを実現 -

- 編集後記

- シミュレータの進化による革命 最新の高速大容量SPICEシミュレータ 「Spectre X」

- サインオフRC抽出ツールQuantusの技術紹介 ~P&RツールInnovusと組み合わせて使う意味とメリットとは!?~

- データセンター設置に最適化された初のエンタープライズプロトタイピングシステム新製品 Protium X1のご紹介

- ISO26262第2版と半導体における機能安全

- 車載、AR/VR、モバイル、監視カメラの市場に向け、ビジョン、AI処理のパフォーマンスを2倍高速化したVision Q7 DSP

- オートモーティブ電子システムデザイン・セミナー開催レポート

- CDNLive Japan 2019ご案内

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues