ISO26262第2版と半導体における機能安全

自動車向け電子制御系の安全規格(機能安全)として 2011 年 11 月に発行されたISO26262ですが、昨年末にそのアップデート版としての第2版(ISO26262-2018)が発行されました。2018年の第2版改定では多くの改定が含まれておりますが、その大きな改定の1つとして、Part 11: Guidelines on application of ISO 26262 to semiconductorsとして、半導体に特化した章が建てられたことがあります。

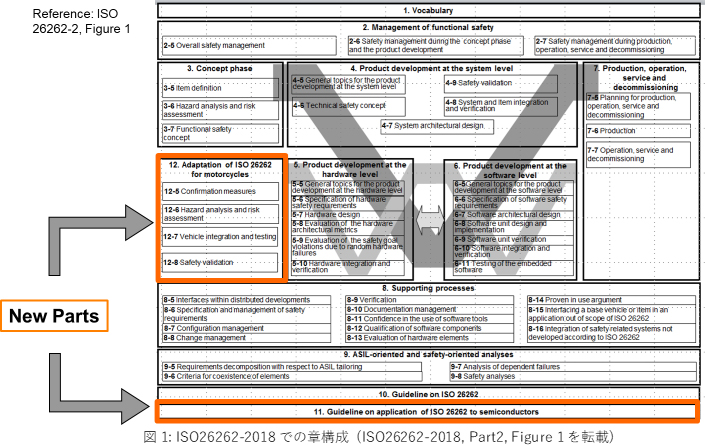

図1に、ISO26262-2018全体の構成を示しました。このうち、オレンジ枠で囲まれた部分が、新たに追加された章です。Part11は図1では小さなエリアでありますが、実はPart 11だけで200ページ弱と、ISO26262-2018全12章のうちほぼ1/4のページ数を費やしており、内容的には極めて大きなボリュームかつ比率となっています。なぜこのような大きな追加が、半導体を対象とした機能安全を考える上で必要になったのでしょうか?それ以前に、なぜ半導体を独立して記述しなくてはならないのでしょうか?

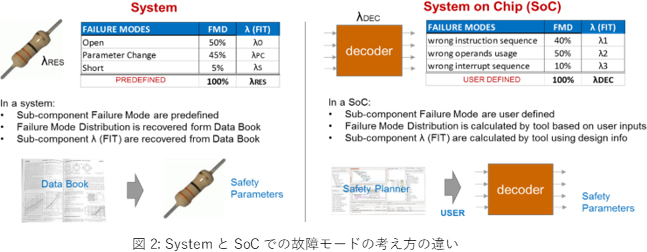

半導体を含むハードウェアに対しての機能安全は、2011年発行の第1版から変わらずPart 5にて記述されています。が、その主たる記述は抵抗やコンデンサ、マイクロコントローラなどを組み合わせたボードやそれらのボードを組み合わせた「システム」を想定したものです。ここで問題となることは、機能安全を考える上で、SoCをはじめとする半導体とシステムでは、若干の考え方の差があることです。例えば、ISO26262を進める上で必須なFMEDA(Failure Modes Effects and Diagnostics Analysis)の実施を例にあげますと、FMEDAを実施しようとしたとき、システムではその構成部品である抵抗やコンデンサなどの故障モードや故障率はSN 29500やIEC 61709のような業界データハンドブックから入手することを想定しています。一方、SoCを考えた時、SoC内のサブモジュールはALUやメモリなどのある程度の類型化はできるとしても、基本的に機能や構造に大きな柔軟性があり、それこそ設計ごとにサブモジュールの機能・特性が異なることもごく当たり前です。そのため、一般論としてサブモジュールに対しての故障モードや故障率を与えてくれるような都合の良いデータハンドブックはありません。従って、SoC内のサブモジュールの故障モードや故障率は、ユーザが定義/算出する必要があります(図2)。それらのSoCでの機能安全を取り扱う際に特有な定義や算出をどのように行うか、そのためのガイドラインの提示がPart 11のキモとなっています。

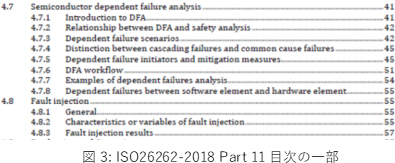

図3はISO26262-2018 Part 11の目次の一部ですが、SoC機能安全上必要な定義・算出を行う手法として、故障注入検証や従属故障分析などの手法が、明示的にかつ独立した節をもって説明されています。SystemとSoCの機能安全分析手法に差があり、それらの手法が比較的に複雑であることが、それらを説明するためのPart 11が独立した章になり、またそのボリュームが大きくなった一因ではないでしょうか?

少し視点を変えますと、このような多くのページを費やして説明されるような「複雑な」手法を駆使することが、半導体の機能安全を確保するためには必要であるということになります。今までのSound of Cadence記事でも、複雑である故障注入検証やFMEDAなどの手法適用を、ケイデンスのツールを使い自動化・効率化する提案をご紹介してきました。どのように開発プロセスに取り込むかというフロー視点も含めまして、なにかご不安があれば、ぜひとも弊社までご相談ください。

また、2019年7月19日に実施されるCDNLive Japan 2019では、SGS ジャパン株式会社の松尾 健彦様から、「ISO26262 2nd Editionを踏まえた半導体の機能安全開発におけるポイント」と題して、安全分析、従属故障分析、故障注入などの手法も含めてISO26262-2018のPart11のポイントを機能安全の専門家視点から解説いただけますので、ぜひともご参加を検討ください。

最後となりますが、ISO26262-2018のPart 11では、その対象とする半導体についてもリストアップして述べています。その中で、PLD(Programmable logic devices)、これはFPGAと呼んだ方が通りが良い場合もあるかもしれませんが、も対象であることが明記されています。特に、PLDユーザの書くHDLコードも、明確にハードウェア扱いであり、通常のデジタルLSIと同様にPart11の対象となることが明記され、PLDユーザがSPFMやLFMなどのメトリクスをASILレベルに合わせて達成することが求められています。従来、PLD用のHDLコードはソフトウェア扱い(Part 6の対象)との認識も一部であったようですが、その誤解を払拭し何をやらなくてはいけないかを明確化する上でも、FPGAを使う方々も是非とも今回の講演を聴講くださることで、得るものは大きいのではないかと思います。

テクノロジーセールスリード

システム&ベリフィケーション

後藤 謙治

Latest Issue

- Clarity 3D Solver Technology - 高精度+大規模なパフォーマンスを実現 -

- 編集後記

- シミュレータの進化による革命 最新の高速大容量SPICEシミュレータ 「Spectre X」

- 今、なぜ、ケイデンスの次世代物理合成ツール Genus Physical Synthesisの躍進が著しいのか?

- サインオフRC抽出ツールQuantusの技術紹介 ~P&RツールInnovusと組み合わせて使う意味とメリットとは!?~

- データセンター設置に最適化された初のエンタープライズプロトタイピングシステム新製品 Protium X1のご紹介

- 車載、AR/VR、モバイル、監視カメラの市場に向け、ビジョン、AI処理のパフォーマンスを2倍高速化したVision Q7 DSP

- オートモーティブ電子システムデザイン・セミナー開催レポート

- CDNLive Japan 2019ご案内

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues