Allegro/OrCAD PCB 17.2-2016 QiR4

PCB Editorアップデートのご紹介

先般、設計作業中にDFM検証をリアルタイムに実行する業界初のソリューションCadence® Allegro® PCB DesignTrue DFMテクノロジを含む最新QIR (Quarterly Incremental Release) 4リリースをはじめ、これまでの17.2 QIR1~3リリースから継続的に進化する有益な機能を取り上げ、Allegro/OrCAD 17.2 QIRアップデート・セミナーを9月21日に開催させていただきました。

以下、セミナーにてご紹介いたしましたQiR4の新機能や改良点の一部をご紹介いたします。

DesignTrue In-Design DFM Technology

従来のDFMフローは、設計センター内のファブリケーター、または内部サインオフグループとの数多くの相互作用から成り立っており、製造段階へのリリース迄には多くの時間がかかり、製品のリリーススケジュール全体に影響を及ぼします。DesignTrue™In-Design DFMテクノロジは、既に利用されているコンストレイント・マネージメントシステムに製造チェックを組み込むことにより、プロセスを改善し、設計プロセス中でのリアルタイム製造チェックを実行、修正し、イテレーションを削減し、設計効率を向上させることができます。

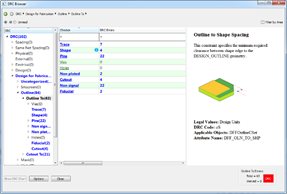

DRC Browser

DRCブラウザは、Allegro/OrCAD PCB Editorの新しいツールで、DRCの検索、レビュー、およびアドレス指定を行います。DRC違反の種類や領域による設計上の問題の解決に集中できるように、さまざまなナビゲーション、並べ替え、フィルタリング機能が含まれています。 この新しいツールは、デザイン/レイアウトエンジニアの生産性を大幅に向上させることができます。

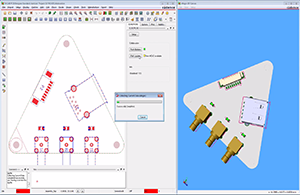

Interactive3D Canvas Updates with Rigid-Flex

我々は継続的に Interactive3D キャンバスに新しい機能を追加しています。今では、マルチゾーンのリジッドフレックスデザインの曲げを表現することさえできます。折り畳んだ状態を表示し、デザインが曲がったときの衝突チェックを行い、選択した2点間を3Dモードで測定できます。 17.2-2016 QiR4の主な3D機能は次のとおりです。

- フレックス材料の3D曲げ

- 3Dコンポーネントの配置と移動

- 3Dスペーシング測定

Seamless Mechanical CAD-Electrical CAD Collaboration

PCB Editorの機械系CADコラボレーション環境は、PCB Editorと他の機械系CADツールの両方が読み書きできる共有IDXベースのデータ格納エリアを有効にすることで、シームレスなコラボレーションプロセスを実現します。 これにより、設計サイクル中に発生する可能性がある複数の変更やエラーを管理する心配が軽減されます。 機械系CAD-電気系CADソリューションはIDXベースのリポジトリをベースにしているため、ベンダーに中立です。 言い換えれば、IDXをサポートする機械系CADソリューションはPCB Editorと容易に統合が可能です。 PCB Editorを使用すれば、機械系CADエンジニアとのコラボレーションはボタンを押すだけで簡単に実現できます。

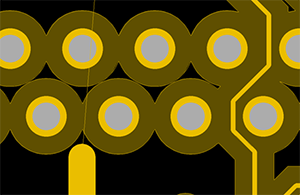

Advanced Routing Features

Route Optimization - この新しいHug/Shoveオプションは、 "Trace-to-Feature"スペーシングを最適化し、配線チャネル間でエッチを自動的にセンタリングまたは均等分配し、最大のパフォーマンスと歩留まりを向上させます。

Route Clearance View - リアルタイムのスペーシング/物理的制約情報を視覚的に表示し、ルーティング処理を支援します。

General Productivity Enhancements

Dynamic Component Alignment - Microsoft toolsと同様にスナップガイドラインを使用して、コンポーネントをダイナミックに整列調整します。

Dynamic Ratsnesting - コンポーネントの移動中にラットネスト接続をリアルタイムで更新します。

Multi-Destination Paste - 新しいコピー/ペーストの動作により、複数のデスティネーションの貼り付けおよびコピーしたアイテムを後で保存して呼び出すことができます。

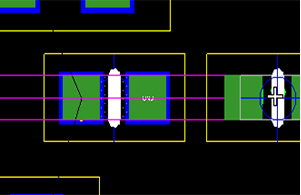

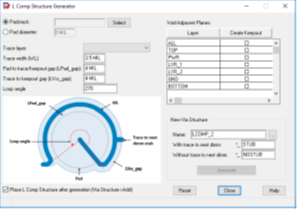

L-Comp Structures

高速信号はインピーダンスを維持するために特別な注意が必要です。 インダクタンス補償構造(L-Comp構造)は、ピンに追加のインダクタンスを加えることにより、ソケットの静電容量の軽減に役立ちます。

※この機能は、Allegro PCB Designer + HS Optionにて利用可能です。

今回ご紹介の内容に関しましてお問い合わせがございましたら、貴社担当営業、あるいはメール: [email protected]へご連絡ください。

日本ケイデンス・デザイン・システムズ社

SPB / Allegro, OrCAD, Sigrity and ICP Products

イノテック株式会社

ICソリューション本部

Latest Issue

- ハイパフォーマンス・コンピューティング分野と車載分野に向けたケイデンスの設計IPソリューション

- 事例紹介:広島大学によるXtensa Vision P6の大腸がん診断支援システムへの適用

- ケイデンスが提供する第3世代論理シミュレータ Xcelium その先進の性能とは?

- フォーマル証明の内側「ヘルパーアサーションってなんだ?」

- デジタル設計効率を大幅に改善する共通ユーザーインターフェースStylus Common User Interface

- 革新的なDRCデバッグを実現 - Results Viewerのご紹介

- もう昔のように作れない。悩める設計者必見!! 先端テクノロジ設計者のためのコンベンション —カスタムIC Advanced Nodeサミット 2017—

- 編集後記

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues