ケイデンスが提供する第3世代論理シミュレータ Xcelium

その先進の性能とは?

RTLの設計、検証をご担当の方は、日常的に論理シミュレータを利用されていると思います。現在ご利用のシミュレータ環境に対し、何かご不満などお持ちでしょうか?

比較的小規模なIPやブロック設計をご担当されている方には、シミュレーションの性能(速度)は大きな問題でなく、それよりもデバッグ機能を重視されるかも知れません。一方、複雑な機能を持つブロックや画像処理を行うブロックは、シミュレーション実行時間が短縮されると業務効率向上に繋がる場合もあるでしょう。

長大な入力ベクタを処理するテストの処理や、大規模なチップレベルのシミュレーション実行時間では、実行コマンドやテストベンチ構築方法を工夫して時間短縮を計られていたり、複数のジョブ投入を効率化するスクリプトや検証マネージメントツールを利用するなど、いろいろ工夫をされている方もいらっしゃるかも知れません。

また、環境整備は他部門の方が担当され、自身は主務である設計、検証業務に注力し、決められたコマンドを実行することで検証作業を進めている、という方も多くおられるのではないでしょうか。

おそらく、どんな場面においても「論理シミュレータは高速である」に越したことはないでしょう。

ケイデンスは、高度な検証ソリューションを提供することで半導体の設計・検証をサポートし、日々の業務を効率化して頂くことを目指しておりますが、その最も基礎となるべき論理シミュレータの実行性能向上を非常に重視しています。

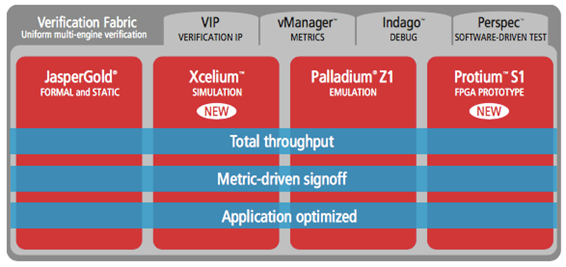

検証を支えるエンジン

ケイデンスの新製品である、Cadence® Xcelium™ Parallel Simulatorは、第3世代の論理シミュレータであり、ケイデンスのVerification Suiteの中の主要4エンジンの1つです。他の3つは、JasperGold®フォーマル検証プラットフォーム、 Palladium Z1®エンタープライズ・エミュレーションプラットフォーム、Protium™ S1 FPGA ベース・プロト タイピング検証プラットフォームです。(図1)

図1. Cadence Verification Suite

これらは高速な検証実行を可能にするべく、業界最速のソリューションを提供するものです。

Xcelium:先進のアーキテクチャ

Xcelium Simulatorは、シングルコア実行とマルチコア実行の2つの実行モードがあります。

シングルコア実行では、従来比で、平均2倍程度の高速化を実現しています(デザインやテストベンチの構成により加速度合いは異なります)。

一方、マルチコア実行は、同一ワークステーション上の複数のコアに実行Jobを割り当て並列にシミュレーションを実行します。検証対象が、RTL, Gate Level, Gate Leve-DFTなどで最大の加速度合いが異なりますが、数倍から数十倍の高速化を実現出来ます。

Cadence Xcelium Single-Core Simulator

Xcelium Simulatorのシングルコア実行は、従来のIncisive® Enterprise Simulator (IES)の技術を踏襲したシミュレータです。IESで実行可能な環境はXcelium Simulatorへの移行は非常にスムーズに行えます。

エンジンの最適化、先進技術の適用の効果もあり、従来のIES比、平均2倍程度の高速化を計っています。

既に、国内のユーザー様においても、Xcelium Simulatorの速度改善を体感頂いており、最新のシミュレータに変更することで、検証環境を全く変更することなしに数十パーセントの速度改善を確認頂けているケースも多く見られます。

Xcelium シングルコア実行では、エンジンの最適化に加え、以下の高速化技術が実装されています。

- Xceligen : 高速制約解決エンジン

- Dynamic Test Reload : シミュレーションシナリオの動的切り替え

Xceligenは、SystemVerilogテストベンチでのランダムデータ生成の制約解決を高速化する、新しい制約ソルバーです。

シミュレーション実行時にXceligenを有効にするオプションを指定することでとても簡単にご利用頂くことが出来ます。

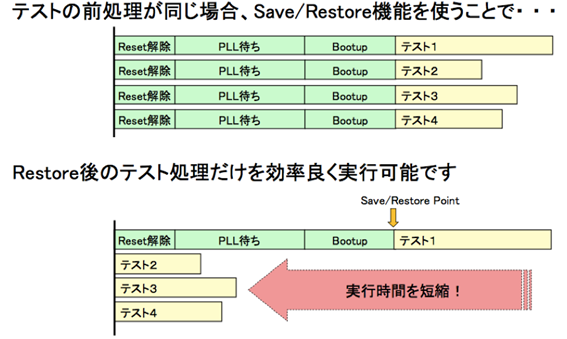

Dynamic Test Reloadは、以下のように、Save/Restore機能と併用頂くことで、複数のテスト実行を効率化し、短時間での複数テストの実行を可能にする手法です。

図2 Save/Restoreを利用したDynamic Test Reloadのイメージ

Xcelium Simulatorは、この機能によりSystemVerilogのランダム検証環境に対し、動的にシナリオを切り替えることが可能で、検証短TAT化を実現します。

Cadence Xcelium Multi-Core Simulator

Xcelium Simulatorは、「第3世代のシミュレータ」と位置付ける最大の理由である、マルチコア技術も実装しています。

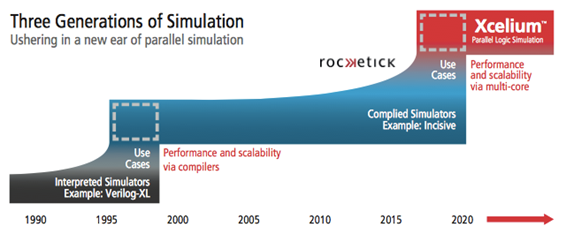

図3は、論理シミュレータのアーキテクチャの変遷を示しています。

1990年代より論理シミュレータの性能は、EWSの性能(主としてCPUのクロック周波数の伸び)に依存して向上しておりました。ただ近年は、EWSの高性能化は、CPUのマルチコア化に寄るところが大きく、論理シミュレータもマルチコア対応が待たれておりました。

図3 論理シミュレータの基本アーキテクチャの変遷

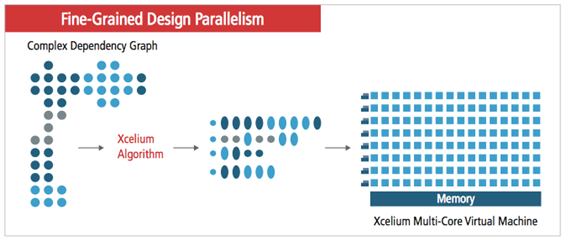

Xcelium Multi-Core Simulatorは、Rocktick社(2016年にCadenceが買収)が開発したFine-Grained Design Parallelism技術により、大規模なデザインをEWS上の複数のコアにマッピングし高速に処理することを可能にしています。(図4)

図4 Xcelium Multi-Core Simulatorが提供するFine-Grained Design Parallelism

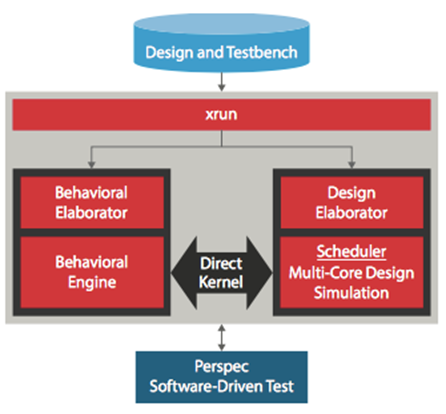

この技術により、図5に示すように、デザインとテストベンチは、xrunというコマンドで処理され、並列実行可能なデザイン部(加速領域)とそれ以外の部分(非加速領域)でエラボレーション処理を分離し、加速領域は、マルチコアデザインシミュレーションエンジン上で実行され、非加速領域であるテストベンチやデザインは、ビヘイビアエジンで実行されます。

図5 Xcelium Simulatorの加速領域と非加速領域パーティショニング

ビヘイビアエンジンは従来のIESを踏襲しており、シングルコア実行はこのエンジンを利用します。一般に、小さな計算要素が多いデザインであり、且つイベント密度の高いテストシナリオの場合、シングルコアでの実行に比較して、マルチコア化による加速可能な割合が高くなる、と言われています。

DFTデザインのゼロ遅延シミュレーションは加速効果の高いデザインの代表例です。

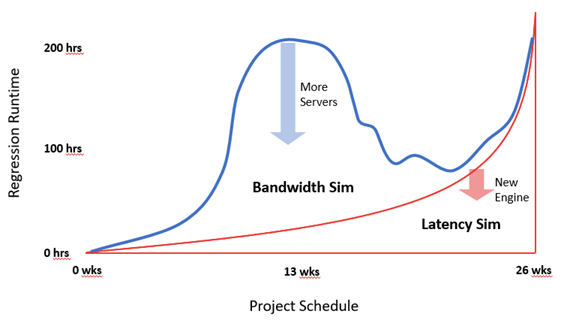

シングルコア実行とマルチコア実行は検証フェーズにより使い分けることで高い効果が期待できると考えられます。一般には、図6に示すように、複雑なSoC等の検証において、検証の終盤では、シミュレーションのレイテンシが検証完了の日程に大きく影響します。

図7 一般的な検証プロジェクトにおけるレグレッションテストの実行負荷

Multi-Engine MDV

Xcelium Simulatorでは、シミュレーション高速化の対応を重要な特徴と位置付けています。

加えて、明確な基準を持って検証完了の判断を下すために、MDV: Metric Driven Verification(検証指標に基づく検証管理)という考え方で検証を進めます。

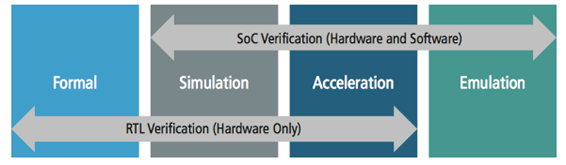

検証指標の計測は、Xcelium Simulator以外の検証エンジンから生成されるデータベースと統合に可能な形式でカバレッジデータを生成します。

図8 異なる検証エンジンを利用したMDV

因みに、ケイデンスのMDVのコンセプトでは、RTL検証では、ハードウェア部分のカバレッジ統合を想定していますが、SoCの検証では、それをソフトウェアに拡張することも想定しています。

Combined Coverage

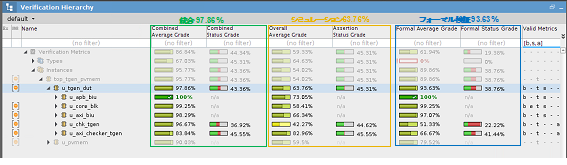

Multi-Engine MDVの最も特徴的な機能が、Combined Coverageと呼ぶ、Formal検証(JasperGold®)とシミュレーションのカバレージ統合(Combine)機能です。

シミュレーションでは、通常コードカバレージ、アサーションカバレージ, 機能カバレージなどを計測することが主流ですが、Formal検証で実行した結果をカバレージとして統合することで、冗長な検証実行を削減することが可能です。

図9 カバレージ 統合のイメージ

Xcelium SimulatorとJasperGoldで生成された カバレージデータはUniCovという形式のDBとして生成されるため、検証管理ツールであるvManager™ Metric-Driven Signoff Platformにこれらの結果を読み込み、統合された結果として確認することが可能です。

まとめ

LSIの大規模化に伴い、検証に要求されるタスクは高度化する一方です。実行すべきシナリオの組み合わせが増大し、適材適所の検証エンジンやツールを利用することが網羅的な検証作業を短時間に実施するための重要なアプローチとなっています。

中でも、高速な論理シミュレーションはその中核を成す重要な要素であると考えます。

ケイデンスは、Xcelium Simulatorを筆頭に、先進の検証ソリューションを提供し、漏れのない検証を短TATで実現頂くことで、引き続きお客様のビジネス成功のお役に立ちたいと考えています。

テクノロジーセールスリード

ディレクター

鈴木 佳香

Latest Issue

- ハイパフォーマンス・コンピューティング分野と車載分野に向けたケイデンスの設計IPソリューション

- 事例紹介:広島大学によるXtensa Vision P6の大腸がん診断支援システムへの適用

- フォーマル証明の内側「ヘルパーアサーションってなんだ?」

- デジタル設計効率を大幅に改善する共通ユーザーインターフェースStylus Common User Interface

- 革新的なDRCデバッグを実現 - Results Viewerのご紹介

- もう昔のように作れない。悩める設計者必見!! 先端テクノロジ設計者のためのコンベンション —カスタムIC Advanced Nodeサミット 2017—

- Allegro/OrCAD PCB 17.2-2016 QiR4 PCB Editorアップデートのご紹介

- 編集後記

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues