ハイパフォーマンス・コンピューティング分野と車載分野に向けたケイデンスの設計IPソリューション

ハイパフォーマンス・コンピューティング(HPC)

現在HPCアプリケーションでは以前には考えられなかったような膨大なデータが扱われるようになってきてます。例えばYouTubeでは毎分100時間分のビデオがアップロードされ、Facebookでは毎日45億件の書き込みと10億件のビデオがアップロードされています。またAmazonでは毎秒426件の販売取引が行われ、WeChat(微信)では11億人のユーザが毎日40分間チャットを行います。

このようなデータ量の増大に伴ってHPCシステムの開発現場では技術革新が進行しています。これまでもMooreの法則に則ったSOCの高集積化、マルチコア・アーキテクチャによるパラレル・プロセッシングが進められてました。それに加えて今、ヘテロジニアス・コンピューティングが注目を集めています。ヘテロジニアス・コンピューティングでは異種のコンピューティングデバイスCPU、GPU、FPGA、DSPなどが最適な性能/電力比を実現するように結合されます。

ところがこの最適化を達成する際には、コンピューティングデバイスの性能そのものよりもむしろ、キャッシュ、メモリー、ストレージからなるメモリーのヒエラルキーがボトルネックになってくるとも言われています。メモリーシステムのバンド幅やレイテンシーによるボトルネックはもちろんのこと、90%の電力がデータを転送するために費やされているという試算もあります。

またマシンラーニングの分野でも、アーキテクチャ開発においてはニューラルネットワークやそのアルゴリズムに注目があつまっていますが、ハードウェア設計に落とし込む段階ではやはりデータ転送がボトルネックとなってしまうため、アーキテクチャ設計と同時にインターフェース設計にも同じように注力する必要があります。

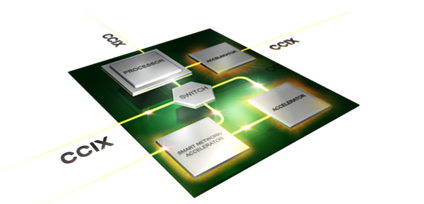

この問題を解決するために、従来からデータセンター用途に広く使われてきた高速インターフェースであるPCI Expressに加えて、CCIX(Cache Coherent Interconnect for Accelerators)やGenZのような、ヘテロジニアス・コンピューティングを対象とした新しい高速インターフェースが登場しました。特にCCIXはキャッシュ・コヒーレンシを備えつつレイテンシーも短縮しており、現在は25GT/sのバンド幅を有していますが将来は56GT/sの可能性も検討されています。

CCIXが登場する以前は、CPUは例えばDMAでアクセラレータへデータを転送し、アクセラレータはCPUへ割り込みを返し、結果のデータをメインメモリーに書き込む、といった動作によりレイテンシーが長くなっていました。CCIXではCPUとアクセラレータ間のキャッシュ・コヒーレンシをとり、データ転送のオーバヘッドを削減します。またソフトウェア開発もARMプロトコルをベースにすることで複雑化を避けられるという利点があります。

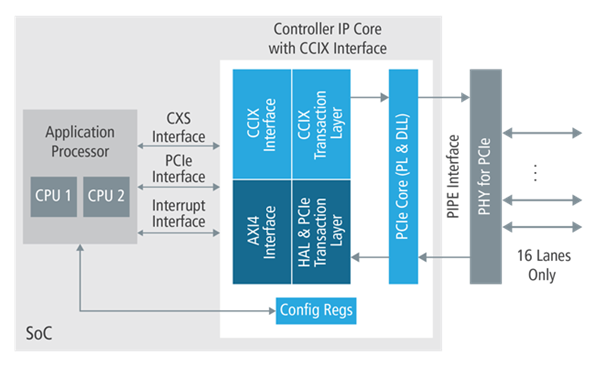

ケイデンスは2017年5月2日に、業界初のCCIXインターフェースIPおよび検証IPの統合ソリューションを発表しました。ケイデンスのCCIXインターフェースIPは、16nmで業界に先駆けてシリコン実証され多数の採用実績を重ねてきたPCI Express Gen4 IPソリューションを活用し、CCIXに必要となるトランザクション・レイヤーを追加しています。

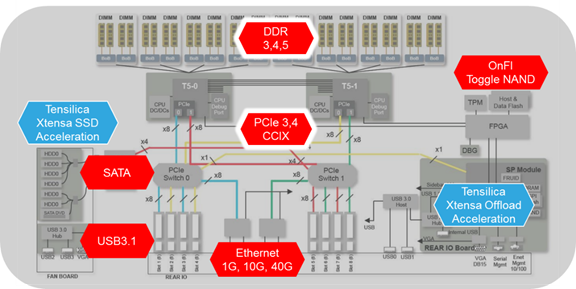

さらにXilinx、ARM、ケイデンス、TSMCの4社は2017年9月11日、TSMC 7nmプロセステクノロジーを用いた業界初のアクセラレータ向けCCIXテストチップの開発協業を発表いたしました。このテストチップはArm® のマルチコアCPUからコヒーレントファブリックを介してXilinzのFPGAアクセラレータのオフチップ動作を実現するCCIXシステムの性能を実証するために開発されます。このTSMCの7nmプロセステクノロジーを用いたテストチップのCCIXサブシステムの開発にあたり、ケイデンスはCCIX IPソリューション(コントローラーおよびPHY)、PCI Express® 4.0/3.0 IPソリューション(コントローラーおよびPHY)、DDR4 PHY、I2C、SPI、QSPIなどのインターフェースIPを提供しています。またチップ設計にはケイデンスの検証およびインプリメンテーションツールが使用されています。

7nm CCIXテストチップ向け ケイデンスのインターフェースIP群 |

|

このようにハイパフォーマンス・コンピューティング分野に向けてケイデンスでは主要な高速インターフェースIP群を取り揃えており、テンシリカDSP IP、インプリメンテーションツールを含め、お客様のHPCチップ設計を全面的に支援いたします。

車載

車載分野においてもハイパフォーマンス・コンピュータ分野と同様に技術革新が進んでいます。従来の車載向けICは高信頼性を求められる一方で、デザインサイクルは長く、比較的小規模なSOCでした。またコンシューマ分野では、車載ほどの信頼性は求められない一方で、デザインサイクルは短く、大規模なSOCが要求されてきました。ところが現在の車載アプリケーションではADAS(Advanced Driver Assistance System)に使われる画像処理/レーダ用ICのように、従来の車載分野における高信頼性の要求とコンシューマ分野における短いデザインサイクルと大規模SOCの要求がともに求められています。しかも先端プロセスを用いて高信頼性を実現するという、過去に例のないアプリケーションとなっています。実際ADASアプリケーションにおける画像処理はそのフレームレート、解像度、データストリームの要求から膨大なバンド幅をDRAMメモリーシステムに要求します。たとえば8メガピクセルクラスのカメラ1個で60fps、16bit depthの場合1ギガバイト/秒のバンド幅が必要となりますし、複数のカメラ画像を同時に処理する場合にはさらに高いバンド幅が必要となります。このような高い性能要件を満たすDRAMメモリーシステムを短いデザインサイクルで開発するためには、シリコン実証された最高速のDDR IPサブシステムが不可欠となります。現在メモリー市場で入手可能なDRAMの中では、高速、低消費電力、信頼性、シグナルインテグリティの観点から、4266MbpsスピードグレードのLPPDDR4、LPDDR4Xが望ましいと言えます。

また信頼性の観点では、最低限AEC-Q100の温度範囲が、車載向けのSOCで要求されるグレードに応じて必要となります。TSMCは16FFCを車載向けプロセスノードとしています。さらにSOC開発とソフトウェア開発はISO26262に基づいた機能安全の設計アプローチが、システムが要求される機能安全基準に対応して必要となります。16nmレベルの半導体プロセスでは一般的に故障率が500FITS程度と言われていますが、一方車載向けでは10FITSレベルが求められます。この故障発生を安全に扱うためにASIL-B/C/Dの各安全基準が設定されています。

車載向けSOCは上記のような、高性能、AEC-Q100、および機能安全/ASILを同時に満たす必要があります。一方、このSOCの設計部品のうち標準IPについては、車載向けチップメーカ様によって開発される必要はかならずしもありません。

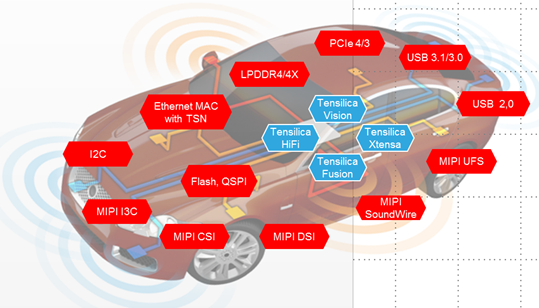

ケイデンスでは9月7日、TSMC 16FFC車載用プロセステクノロジー向けに、車載用IPの包括的なポートフォリオの提供を開始することを発表しました。ケイデンスの車載用IPはAEC-Q100 Grade 2規格が定める使用温度範囲を満たし、またISO 26262規格で概要が示されているエンドユーザーの安全目標および安全要求に基づいて、ASIL-B対応準備完了、ASIL-C/D対応可能となるように設計されています。

車載インフォテインメントおよびADAS SoC向け設計ニーズに対応するケイデンスのIPラインナップ |

|

ケイデンスの車載用IPポートフォリオの中では、4266Mbpsスピードグレードに対応するLPDDR4/4X DDRコントローラーおよびPHY、PCI Express® 4.0 PHYおよびコントローラーがサポートされています。これらのいずれのIPもケイデンスによりTSMC16nmプロセスにおいて、業界で始めてシリコン実証を完了しています。

このようにケイデンスでは、車載向けSOCの高性能、高信頼性の設計要件を満たすシリコン実証済みの設計IPと、またADASチップに不可欠な画像処理、音声処理、マシンラーニングに対応するテンシリカDSP IPも加えて、お客様のADASチップや車載インフォテインメントチップの早期開発を支援いたします。

最後に、弊社では昨年に引き続きIPソリューション・セミナー2017を新横浜国際ホテルにおい10月18日に開催する運びとなりました。業界動向を含めケイデンスが提供する設計IP、テンシリカDSP、検証IPをご紹介いたしますので、ぜひご来場いただきごHPC向けSOCおよび車載向けSOCのお役立ていただけますと幸いです。

詳細/お申込はこちらより

■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■

IPソリューション・セミナー 2017開催のご案内

【 主催 】 日本ケイデンス・デザイン・システムズ社

【 日時 】 2017年10月18日(水) 10:00-17:20 (受付開始: 9:30)

【 会場 】 新横浜国際ホテル マナーハウス

【 費用 】 無料

【 内容 】 10:00-12:05 全体セッション (2階)

13:00-17:20 分科会 (3階)

(1) テンシリカIPトラック

(2) 設計IPトラック

■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■■

設計IP

シニアAEマネージャー

伊原 誠

Latest Issue

- 事例紹介:広島大学によるXtensa Vision P6の大腸がん診断支援システムへの適用

- ケイデンスが提供する第3世代論理シミュレータ Xcelium その先進の性能とは?

- フォーマル証明の内側「ヘルパーアサーションってなんだ?」

- デジタル設計効率を大幅に改善する共通ユーザーインターフェースStylus Common User Interface

- 革新的なDRCデバッグを実現 - Results Viewerのご紹介

- もう昔のように作れない。悩める設計者必見!! 先端テクノロジ設計者のためのコンベンション —カスタムIC Advanced Nodeサミット 2017—

- Allegro/OrCAD PCB 17.2-2016 QiR4 PCB Editorアップデートのご紹介

- 編集後記

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues