ハイパフォーマンス・コンピューティング分野と車載分野に向けたケイデンスの設計IPソリューション

ケイデンスは、ハイパフォーマンス・コンピューティング分野に向けて主要な高速インターフェースIP群を取り揃えており、車載向けにはSOCの高性能、高信頼性の設計要件を満たすシリコン実証済みの設計IPに加え、ADASチップに不可欠な画像処理、音声処理、マシンラーニングに対応するテンシリカDSP IPを提供し、お客様のADASチップや車載インフォテインメントチップの早期開発を支援いたします。

事例紹介:広島大学によるXtensa Vision P6の大腸がん診断支援システムへの適用

CDNLive Japan 2017にて、広島大学 ナノデバイス・バイオ融合科学研究所 小出哲士准教授のグループから「内視鏡画像にCNN特徴を適用した大腸がん診断支援システムのテンシリカVision P6 DSPによるリアルタイム処理の実現」との題で医療アプリケーションへの適用事例を報告いただきました。

ケイデンスが提供する第3世代論理シミュレータ Xcelium その先進の性能とは?

ケイデンスは、高度な検証ソリューションを提供することで半導体の開発をサポートし、日々の業務を効率化して頂くことを目指しておりますが、その最も基礎となる論理シミュレータに関しては今年3月に新製品Cadence Xcelium Parallel Simulatorを発表し、国内のユーザー様においても、Xcelium Simulatorの速度改善を体感頂いてます。

フォーマル証明の内側「ヘルパーアサーションってなんだ?」

ヘルパーアサーションとは、「フォーマル証明の加速を支援するために用意する、実装を説明するためのアサーション」である。アサーションは元来、仕様をフォーマルツールに伝えてデザインを検査するために書くものであった。それに対し、実装の具体的特性を証明エンジンに伝えるための(仕様と直接は関係がない)アサーションが、ヘルパーである。

デジタル設計効率を大幅に改善する共通ユーザーインターフェースStylus Common User Interface

ケイデンスは、各ツールでの最高品質を目指すと共に、トータルフローとしての設計生産性向上にも力を入れています。 その取り組みの1つであるStylus Common User Interfaceは、ケイデンスのインプリメンテーションツール間で共通の実行環境、コマンドおよびレポート体系を提供することにより、ツール間の連携を高め、ユーザーの作業効率を大幅に高めるために構築されたユーザーインターフェースです。

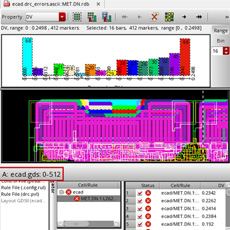

革新的なDRCデバッグを実現 - Results Viewerのご紹介

ケイデンスのレイアウト検証ツールPVS v16.1よりDRCの解析機能として、Results Viewerがリリースされました。ケイデンスの設計プラットフォームVirtuoso、Innovus、Quick Viewと連動し、物理データとクロスプローブを行いDRCの解析を効率的に行う事が可能です。

もう昔のように作れない。悩める設計者必見!! 先端テクノロジ設計者のためのコンベンション —カスタムIC Advanced Nodeサミット 2017—

10月26日にカスタムIC Advanced Nodeサミット 2017が開催されます。このサミットでは、Front-Endから、Design Verificationまでのフローを通じ、如何にVirtuoso ICADV12.3が、異なるテクノロジの要求事項を網羅し、統合環境を実現しているかを紹介します。

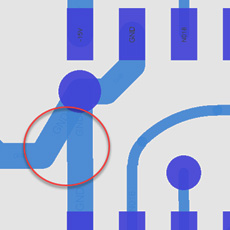

Allegro/OrCAD PCB 17.2-2016 QiR4 PCB Editorアップデートのご紹介

設計作業中にDFM検証をリアルタイムに実行する業界初のソリューションCadence Allegro PCB DesignTrue DFMテクノロジを含む最新QIR (Quarterly Incremental Release) 4リリースをはじめ、 これまでの17.2 QIR1~3リリースから継続的に進化する有益な機能を取り上げご紹介いたしましたAllegro/OrCAD 17.2 QIRアップデート・セミナーを9月21日に開催いたしました。

編集後記

例年のように夏休みが終わるころからSound of Cadenceのトピック探しが始まり、各執筆者の積極的な寄稿提案により、今回も大変充実した内容になりました。是非、ご一読下さい。

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues