チップ全体の最適化およびサインオフを10倍高速化するCertus Closure Solutionのご紹介

今回は米国時間の2022年10月11日に発表した新製品のCertus™ Closure Solutionについてご紹介いたします。

本製品は並列分散同時処理によって、デザインの大きさに制限なく、タイミングおよびパワーの最適化を一晩で完了させることができるソリューションです。処理はすべて完全に自動化されており、使いやすさも備えた世界初の機構です。

これにより、設計の最適化とサインオフを確定するための従来の手動アプローチと比較して、10倍の生産性向上を実現します。

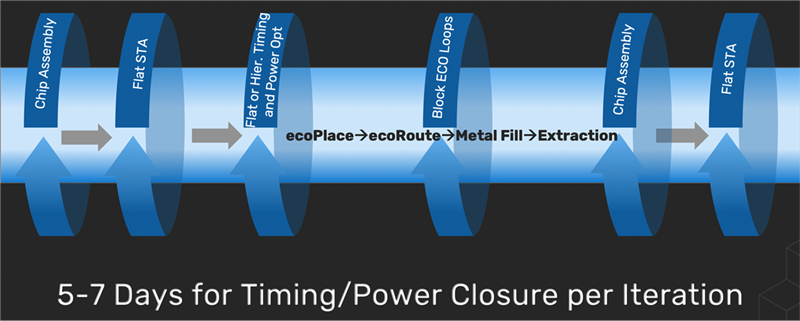

従来の手動アプローチでは、下図のように1回のイタレーション作業に5~7日かかり、イタレーション回数は予測不可能であることほとんどです。仮に30回のイタレーションが必要であれば、フルチップの最適化とサインオフ検証に3カ月要することになります。

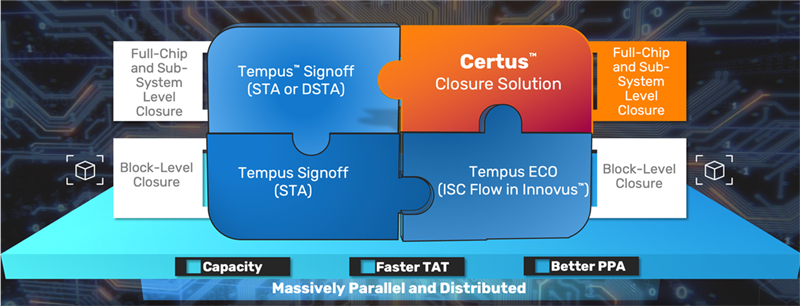

ケイデンスのCertus Closure Solutionは、このプロセス全体を自動化し、一晩での最適化とサインオフ検証を実現します。これは、Tempus Signoff(STAまたはDSTA)、Tempus ECOとInnovusフローで構築することにより実現されます。

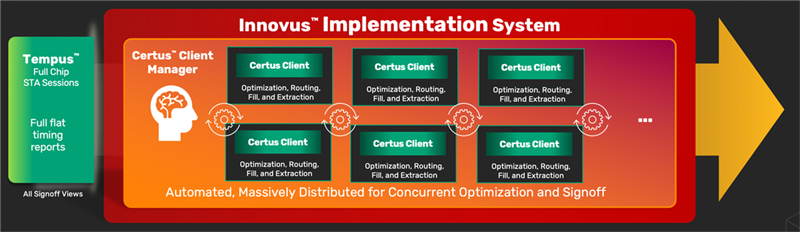

本ソリューションはすべてのタスクを大規模に分散し、全プロセスを完全自動化します。このような並列分散システムでは、下図のように、すべてのワーカータスクを制御するマネージャが存在し、その結果をまとめて次に何を行うべきかを決定しています。

さらに、トップ・ブロック境界などのパーティション間のパワー最適化により、当該箇所を10%~15%、フルチップでは最大5%の消費電力を削減することができます。

主なメリットは以下のとおりです。

- 革新的かつ拡張性の高いアーキテクチャ

Cadence Certus Closure Solutionに搭載されている階層最適化およびサインオフの分散処理アーキテクチャはクラウド上での実行に理想的で、社外クラウド、社内データセンターどちらの環境でも運用可能 - インクリメンタル・サインオフ

デザインの変更された部分のみを柔軟に復元、置換する環境を提供し、最終サインオフプロセスをさらに加速 - エンジニアリング生産性の向上

完全自動化されたフローにより、複数チーム間の長時間にわたる設計イタレーションを軽減し、市場参入期間を短縮 - SmartHubインターフェイス

強化されたインタラクティブなGUIにより、詳細なタイミングデバッグを可能にし、最終段階までデザインクロージャーをサポート - 3D-ICデザインの効率化

Cadence Integrity™ 3D-IC Solutionと密接に統合されており、異種プロセスダイ間のパスのクローズが可能

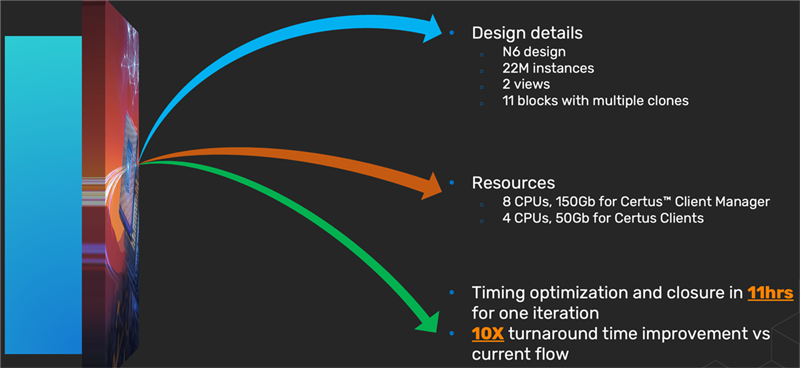

最後にいくつかの事例をご紹介いたします。

例1:6nmプロセス、22Mインスタンス、11時間で実行完了。これは10倍の改善となります。

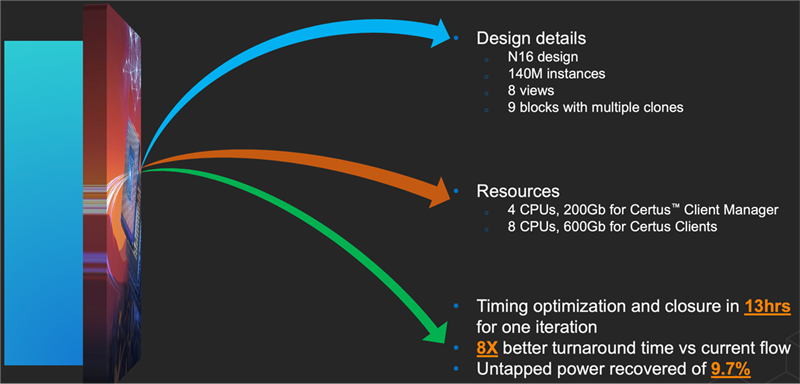

例2: 16nmプロセス、140Mインスタンス、13時間で実行完了。これは8倍の改善となります。

詳細は以下の弊社web siteよりご覧いただけます。

Certus Closure Solution product page.

フィールドエンジニアリング&サービス本部

デジタル&サインオフ

小湊 丈寛

Latest Issue

- ケイデンスがデジタルツイン分野に参入! データセンターのキャパシティ管理と電子機器の熱設計をサポートする革新的なソリューション「6SigmaDCX」

- AI対応ビッグデータ解析プラットフォーム新製品Cadence Joint Enterprise Data and AI (JedAI) Platformのご紹介

- AI ドリブンな機能検証ツール新製品 Verisium Platform

- Cadence Voltus -XFi Custom Power Integrity Solution 3倍以上の生産性向上を実現する次世代EM-IRソリューション

- Cadence Topics: Cadence Blogsをリニューアルしました!

Archive

2024 Issues

2023 Issues

2022 Issues

2021 Issues

2020 Issues