PCB設計では、多くの要因が組み合わされパワー・インテグリティの問題を悪化させるためDC解析が不可欠です。 コアの電圧レベルは低下し続けています。現在では1.2V以下が一般的です。電圧が低下するにつれて、電流要求は通常増加します(IRドロップ= I * R)。電子機器の小型化により、レイヤー数が減り、密度が高くなるため、パワーネットの使用可能領域が減少します。また、ビア周辺のアンチパッドがプレーンを貫通、オーバーラップして「スイスチーズ」効果を作り出します。

さらに、電子メール、通話、経験則などによって伝達されるハードウェアデザイナーやパワー・インテグリティ(PI)エンジニアからの複数の指示からスタートするPCBデザイナーのための電力供給ネットワーク(PDN)の課題があります。デザイナーは、これらの指示と規則のすべてを複数の電源に適用する必要があります。そのため、デザイナーは「20%縮小できるか?」、「2つのプレーンレイヤーと5つのコンデンサを削除できるか?」などの追加要求を満たす必要があります。

複雑なボードには、数十のパワーレール、何百ものパワーネット(フィルタネットを含む)、さらにPDNを構成するコンポーネントがあります。PDNが論理的に接続されていることを確認するために、数百ページの回路図をソートすることは一苦労です。パワー・インテグリティ解析では、これらのネットとコンポーネントをすべてパワー・インテグリティ解析用に指定およびモデル化する必要がある場合、設計プロセスのバックエンドでさらに苦労する可能性があります。これにはセットアップに数日か数週間かかることがあります。

さらなる課題は、設計上の問題がどのように伝達されるかです: PIエンジニアは、PCB設計者にどのように問題と指針を伝えていますか? PCB設計者はPIエンジニアにどのようにソリューションを伝えていますか?解決策が良いかどうかをPCB設計者がどのように判断できますか?幸運なことに、PCB設計者とPIエンジニアがこれらの設計と通信の問題を解決するための統合機能が利用できます。さらに、PCB設計者は、PIエンジニアがガイダンスをまだ伝えていない場合に、初期の電気的制約を自動的に計算して開始するのに役立つツールを提供しています。

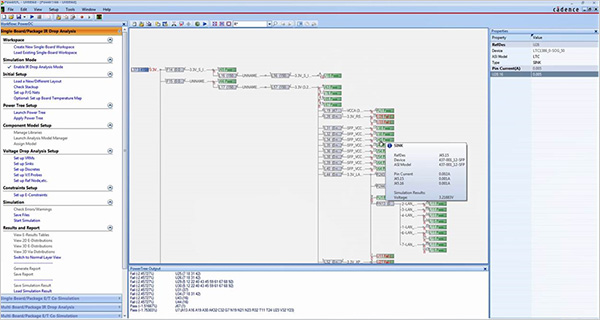

PowerTreeグラフィカル環境

Cadence® Allegro® PowerTree™ テクノロジーにより、PCBレイアウトのスペシャリストとハードウェア設計者は、ロジカルPDNトポロジーでソース/シンク定義、離散値、モデル名、ネット名、デカップリング・コンデンサ値、ターゲットインピーダンス制約などをグラフィカルに表示することができます。

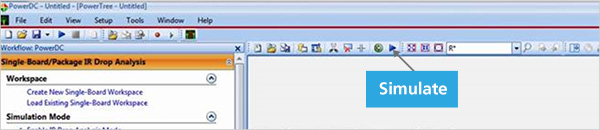

ハードウェア設計者は、ボタンを押すだけで早期の分析健全性チェックを実行できます。回路図データを使用することにより、設計基準を満たすためにPDNトポロジーが適切にキャプチャされているかどうかを判断できます。

ハードウェア設計者とPCBレイアウトスペシャリストが簡単な分析を実行できるようにすることで、PIエキスパートはより専門的な分析に専念することができます。PowerTreeテクノロジーによる自動セットアップにより、PIエキスパートおよび非エキスパートは、同様にPI解析を設定するために何日も何週間も費やす必要がなくなりました。PowerTreeデータを物理設計に適用することで、シミュレーションをボタンのクリックと同じくらい簡単に行うことができます。

インテグレーション機能

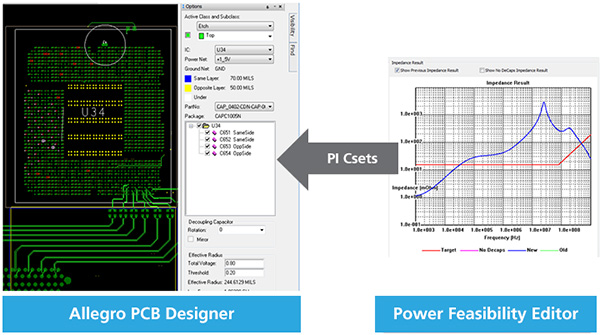

デカップリング・コンデンサの配置ルールでは、PIエキスパートが解析を実行して各ICの理想的なデキャップ方式を決定する必要があります。さらに、PIエキスパートは、PIコンストレイント・セットを作成しPCBデザイナーの配置をガイドする必要があります。

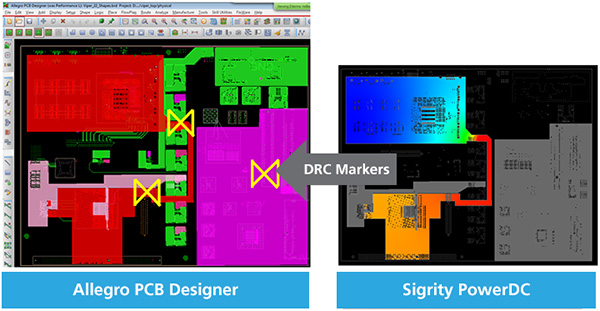

PIデザイナーのルールによって決定されたDRCマーカーには、Cadence Allegro PCB Designerに注釈が付けられています。これらのマーカーにより、PCB設計者はPIエンジニアが発見したPDNの問題を理解し、解決することができます。

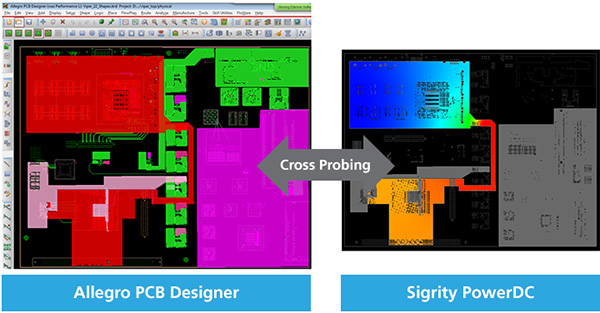

Allegro PCB Designerと解析結果のクロスプロービングにより、PCB設計者はビジュアル解析結果を使用して、パワーシェイプのサイズ増加、ビア追加、プレーン追加など、PCBで何を変更する必要があるかを判断することができます。

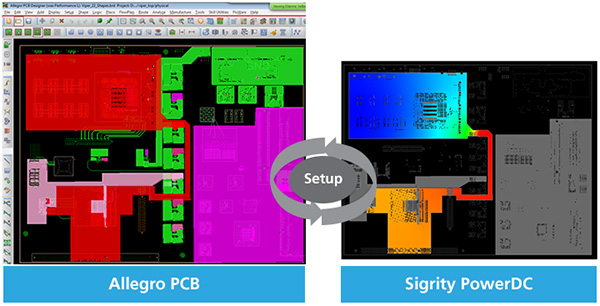

PIエキスパートの設定を再利用することで、PCB設計者は元のセットアップの変更を含め、設計を変更し再分析することができます。

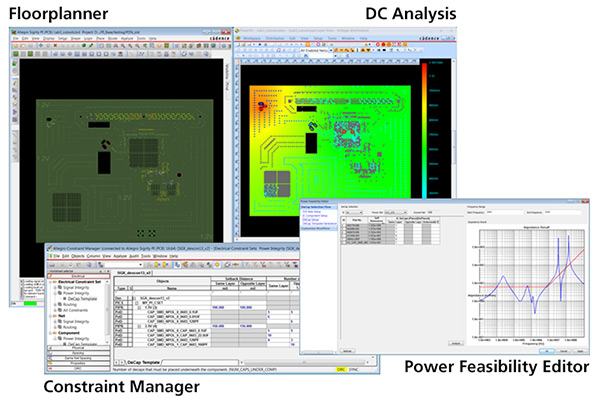

Allegro/Sigrityインテグレーション

AllegroとSigrity技術を統合したAllegro Sigrity™ PI Baseは、PCB、ICパッケージ、システム・イン・パッケージ(SiP)設計のPI解析向けにレイアウトと解析ソリューションを統合したコンストレイント・ドリブン設計を可能にします。Allegro Sigrity PI Baseの主な利点は次のとおりです。

- 実績のあるSigrity分析エンジン

- スケマティックからキャプチャしたPowerTreeデータを使用した自動セットアップ

- デカップ選択と配置を推進する業界初のコンストレイント・ドリブンPI設計プロセス

- DC解析後の自動クロスプロービングにより、物理レイアウトでのIRドロップの問題を簡単に特定し、解決する

- レイアウト設計者とPIエンジニアを対象とする

- 詳細な分析、コンプライアンス、アセスメントのためのアドオン・オプション