Clarity Advanced IC Packaging Extraction

Contact Us

Key Benefits

- Accurate distributed model to reflect the true circuit behavior, including TSV

- Efficient extraction of mutual inductance and coupling capacitance for both power grid structures and I/O signal interconnects

- Maximum accuracy with a compact chip model that is spatially distributed with high pin resolution

- Time-domain simulation environment for easy quality assessment of created interconnect models

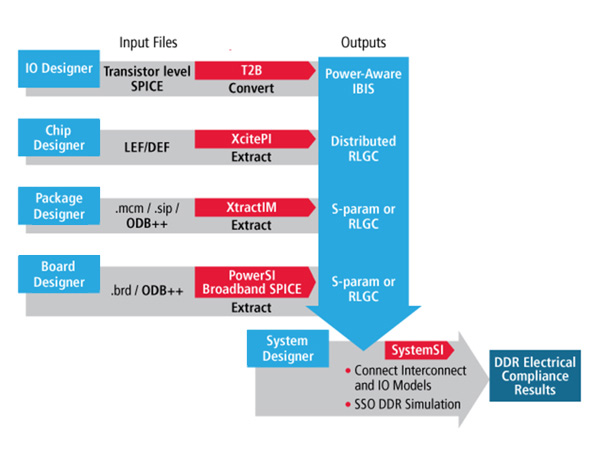

To help you create accurate models for the silicon portion of a power delivery network (PDN) or a signal network, the interconnect model extraction technology is available through a unique extraction solution that creates compact models from silicon layout data. Whether the LEF/DEF (silicon data) file represents a redistribution layer (RDL) or a silicon interposer, creating an interconnect model from classic chip modeling tools is time consuming and too inefficient for use in a system-level time-domain simulator. However, the Sigrity XcitePI™ extraction technology, part of the Advanced IC Package Extraction Suite, provides a compact model with the accuracy needed to run a system simulation for interfaces such as DDR5.

The Advanced IC Package Extraction Suite also includes all the technology included in the Clarity IC Package Extraction Suite. This complete extraction solution complements the Advanced IBIS Modeling, Sigrity Advanced SI, and Sigrity SystemPI solutions.

Features

- Rapid what-if experiments for achieving targeted design performance improvement

- Compact circuit size, compressed from the model of the entire multi-layer power, ground, and/or signal connections

- Generates SPICE models of chip I/O signals coupled to power/ground to be used in chip/package/board analysis of high-speed channels and buses

- Includes MCP model header for easy connectivity to package and IBIS models

- Generated models include effects from TSVs