The Cadence® Liberate™ Variety™ statistical characterization solution provides an ultra-fast standard cell characterization of process-variation-aware timing models. Liberate Variety characterization generates libraries that can be used with multiple SSTAs without requiring re-characterization for each unique format. Variety characterization also generates AOCV and SOCV tables and LVF.

Features

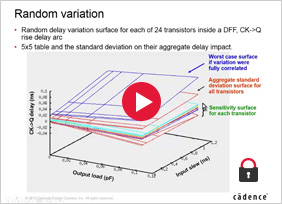

- Creates variation-aware timing models that account for both systematic process variations (e.g., variations due to lithography) and random process variations for any set of correlated or uncorrelated process parameters (e.g., variations due to doping fluctuations between transistors)

- Tool libraries can be used to model both local (within cell and within die) variations and global die-to-die variations

- Enables SSTA or conventional static timing analysis with on-chip variation tables to provide a more realistic estimation of timing relative to actual silicon performance, which often reduces worst-case timing margins by 10-15%, resulting in a higher yielding design that can be taped out sooner