Automotive SoC Design

Read Whitepaper

Cadence has worked closely with all the leading automotive semiconductor suppliers for over a decade, and today, the collaboration continues to refine and improve our industry-leading mixed-signal solutions for automotive SoC design. Benefiting from the on-going evolution of the underlying Cadence® Virtuoso®, Innovus™, Spectre®, and Xcelium® platforms, the Cadence mixed-signal solution provides unique and powerful integration of analog and digital platforms for advanced-node mixed-signal SoC design. Learn more

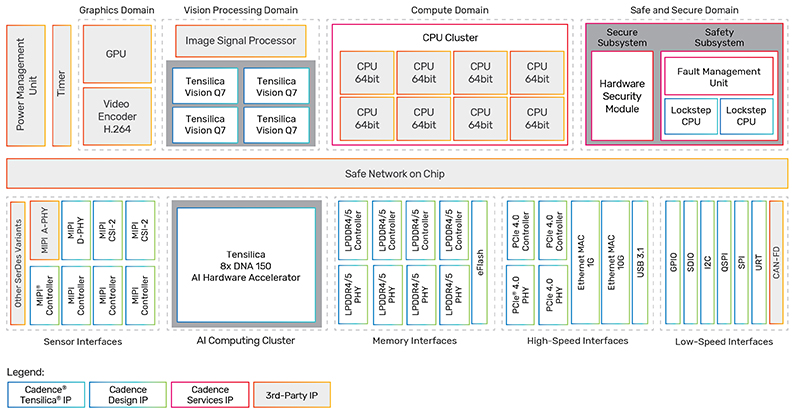

Recent chip developments driven by OEMs have demonstrated what impressive performance can be achieved with a highly automated driving platform. Instead of using existing chips on the market, a purpose-built system-on-chip (SoC) tailored to the system requirements can make a huge difference.

Meanwhile, the automotive industry has realized that for highly automated driving, OEMs and tier 1 supplier need to play a more active role in the definition of the SoC architecture.

A high-performance purpose-built SoC or system-in-package (SiP) is needed in order to meet demanding requirements like feature set, performance per Watt, safety and security—all integrated on a single chip instead on a PCB.

All these new technologies will dramatically increase the complexity of the chip, which may be required to take advantage of the latest process nodes. While high-end automotive SoCs have been been designed in 7nm, some companies are already preparing their next-generation advanced-node designs in 5nm. Foundries claim that 5nm provides about 20% faster speed or about 40% power reduction and is perfectly suited for the next generation of automotive processors.

Cadence"s Automotive solutions—including tools, IP and services—can help you to enable these highly integrated systems that can make cars safer and more reliable.

Mixed Signal

Reliability

An automotive SoC must be reliable across its useful lifetime regardless of the operating conditions or environment. This requirement creates several design challenges. The first challenge is to ensure that testing results in only good parts making it into automobiles. Another challenge is to ensure that even devices operating at high power in extreme environments, such as the engine compartment, never exceed the safe operating region. The final challenge is to reduce the effect of device aging and to extend the lifetime of circuits for vehicles with a typical 15-year lifetime.

Responding to these challenges, the Cadence Legato™ Reliability Solution is the first to help analog designers design for automotive reliability requirements. It provides the tools to manage design reliability throughout the product lifecycle and includes new technology for:

- Analog Defect Analysis: Analyze the manufacturing test’s ability to identify and eliminate test escapes through analog defect simulation

- Electro-Thermal Analysis: Simulates the effect of temperature on circuit electrical performance using dynamic electro-thermal simulation to prevent thermal overstress and prevent premature failures

- Advanced Aging Analysis: Simulate changes in devices over time, including the effects of temperature and process variation on device aging, to better predict product wear-out

Advanced Node

Advanced-node processes challenge automotive designers with the complex interdependency of manufacturing and variability, on top of increasing power and performance specifications.

Leverage complete, consistent, and converging flows across Innovus™ digital and Virtuoso® custom implementation technologies to address design-for-manufacturing (DFM) and variability effects earlier.

Cadence advanced-node platforms enable automotive designers to account for issues such as layout-dependent effects, FinFETs, local interconnect, multi-patterning lithography, and increased device variation and mismatch.

- Automotive mixed-signal SoC design can be centered and optimized for reliability, performance, power, area, and thermal profiles

- Automotive mixed-signal SoC verification can be configured across a range of supported languages, abstractions, methodologies, and Cadence simulation engines, and optimally re-configured as SoC block design progresses to integration

- Provides metric-driven, coverage-based mixed-signal SoC verification and traceability for the IS0 26262 standard

- OpenAccess-based analog and digital implementation, exchange, and signoff

-

Digital Implementation and Signoff

- Stratus High-Level Synthesis

- Genus Synthesis Solution

- Innovus Implementation System

- Physical Verification System

- Conformal Equivalence Checker

- Joules RTL Power Solution

- Quantus Extraction Solution

- Tempus Timing Solution

- Voltus IC Power Integrity Solution

- Voltus-Fi Custom Power Integrity Solution

- Pegasus Layout Pattern Analyzer

- Pegasus CMP Predictor

- [REDIRECT] Liberate Characterization Solution