Armプロセッサ搭載SoCのインプリメンテーション

Arm®ベースのアプリケーション設計に向けて最適化されたデジタル設計フロー

Key Benefits

- Lower risk to develop Arm core-based SoCs

- Easy to use for higher productivity

- Shorter timeframe needed to meet PPA targets

- PPA push technology and expertise to help with last-mile closure

Arm works with EDA vendors to develop EDA reference flows. Working closely with Arm, Cadence has optimized our full-flow digital solution for Arm®-based designs. Using the resulting digital implementation reference flows, you can efficiently implement your Arm core-based systems on chip (SoCs) and reach your power, performance, and area (PPA) targets much faster versus using generic EDA reference flows.

Arm utilizes Cadence® tools to develop its IP. We have early access to Arm cores, so we can tune our tool algorithms, features, and options, and can optimize our flow before the official release of the Arm cores. All of this leads to an added PPA and turnaround time (TAT) boost on top of generic EDA reference flow results.

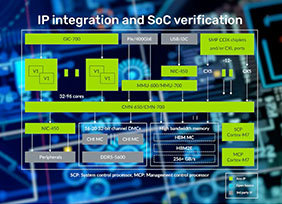

Flows are available for many Arm Cortex®-A, Cortex-R, Cortex-M, and Neoverse cores, multimedia products (GPUs, display controllers, video controllers), and interconnect cores. You’ll get an optimized starting point of scripts, floorplans, and documentation for these CPU and GPU configurations as well as for popular foundry process technologies, including FinFET and other advanced nodes.

Fast Turnaround with Predictable PPA

As you implement the Arm cores on Cadence’s RTL-to-signoff flow, we bring in experienced R&D staff and product engineers who have worked closely with Arm to build reference flows. These technical experts also have experience helping with the PPA push on several tapeouts worldwide on advanced Arm designs, spanning a range of technologies from 40nm to 10nm and below.

Cadence’s digital implementation reference flows are supported by our early collaboration with Arm. With our reference flows, you get design techniques, from RTL to GDSII, for Arm processors, reducing time to silicon with predictable PPA results. Contact your Cadence Sales representative for more information. The flows are also optimized with Arm POP IP core-hardening acceleration technology. Using these flows, you’ll be equipped to efficiently produce optimized SoCs based on Arm big.LITTLE processing systems.

Optimizing for Low Power

Cadence provides a comprehensive solution to design, verify, and optimize power consumption on Arm-based SoCs:

- Functional verification of all the power modes of Arm cores is accelerated using the Xcelium simulator and Palladium® Z1 emulation platform

- Joules RTL Power Solution helps to accurately estimate power at an early stage of the design and to identify peak power under realistic system usage scenarios

- The Genus Synthesis Solution and the Innovus Implementation System help to concurrently optimize leakage and dynamic power while simultaneously maximizing performance and minimizing area

- Conformal® Low Power is the industry-leading low-power formal tool that is routinely used to validate Arm-based SoC designs

- Cadence signoff tools, including Tempus Timing Signoff Solution, Quantus Extraction Solution, and Voltus IC Power Integrity Solution, help accelerate signoff, so you can tape out Arm-based SoCs with confidence

- All tools in the low-power flow support power intent for Arm-based SoCs described in industry-standard CPF and IEEE 1801 power formats

-

ケイデンス、モバイルデバイス向けシリコンの成功を加速するため、Armとの協業を拡大 06/29/2022

-

次世代Armプレミアムモバイルプラットフォーム設計のテープアウトに向けてArm社と協業 05/25/2021

We partnered closely with Cadence to utilize the Innovus Implementation System during the development of our ARM Cortex-A72 processor. This demonstrated a 5X runtime improvement over previous projects and will deliver more than 2.6GHz performance within our area target.

Noel Hurley, General Manager, CPU Group, ARM