Key Benefits

- The industry’s first static timer integration for constraints and CDC signoff enables modeling the design and constraints, using the same interpretation as the Tempus Timing Signoff Solution, to provide customers with 100% signoff accuracy at the RTL

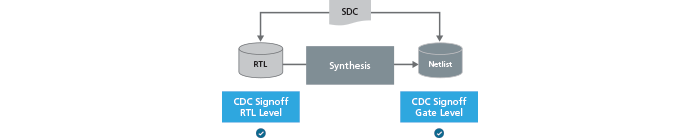

- CDC signoff verifies structural correctness of CDC in the design from early RTL through implementation

- Constraints signoff checks for correctness and completeness of constraints at the IP level and lets users perform hierarchical block versus top consistency checks at the SoC integration level

- Smart analysis generates accurate low-noise reports, providing insights into the design and the constraints intent and enabling users to diagnose root cause failures and signoff rapidly, thereby saving weeks to months in the design schedule

- Multi-CPU parallelization delivers up to 10X faster turnaround time on SoC designs

Achieving first-pass silicon success with rapid execution continues to be a growing challenge for today’s complex designs. Structural signoff is an important step to achieving this success. Converging on signoff-quality constraints to meet aggressive power, performance, and area (PPA) requirements and signing off on clock domain crossings (CDCs) with the accurate constraints are critical in this process.

Cadence® Conformal® Litmus is the next-generation tool delivering the fastest path to SoC-level constraints signoff and CDC signoff.

The key technology benefits of Conformal Litmus are:

- Industry’s first signoff static timer integration: With this integration, the Conformal Litmus can accurately model the design and the constraints using the same interpretation as the Tempus™ Timing Signoff Solution, providing customers with 100% signoff accuracy at the register-transfer level (RTL)

- Multi-CPU parallelization: Verification can be parallelized across multiple cores, delivering up to 10X faster turnaround time on system-on-chip (SoC) designs

Constraints Signoff

SoCs are built hierarchically by assembling subsystems. The subsystems are comprised of legacy designs and many commercially available IP. The IP and their respective timing constraints are developed and validated with their own timing-intent goals before the subsystems and SoCs are realized. Verifying correctness and completeness of the constraints at the IP level and consistency at the SoC level is critical for converging on signoff-quality constraints.

To address these requirements of constraint signoff, Conformal Litmus offers a rich set of built-in rules to verify issues such as missing constraints, timing exception overlaps, and conflicts at the IP level. It also verifies that the intent of the IP-level constraints is consistent with that of the SoC-level constraints.

The Conformal Litmus smart analysis generates accurate, low-noise reports that shorten debug time and help users achieve signoff-quality constraints rapidly.

CDC Signoff

SoC systems have multiple interfaces and sub-blocks that operate on clock domains inherently asynchronous to each other. The designs have extremely complex asynchronous clock schemes that must be verified at every stage in the design flow. If unverified, these crossings can be catastrophic and cause costly chip re-spins.

The Conformal Litmus CDC signoff verifies correctness of CDC structures between the asynchronous clock domains from early RTL through implementation flows.

- Easy setup: Supports timing signoff constraints and includes a TCL scripting environment with powerful control and reporting capabilities. It also supports the Cadence Stylus Common User Interface

- Comprehensive CDC verification: Conformal Litmus performs comprehensive checks to verify proper implementation of synchronization schemes to mitigate metastability and to prevent glitches and re-convergence. Conformal Litmus also verifies the correctness of complex CDC structures, including handshake synchronizers, bus synchronizers, and FIFOs

- Smart signoff: After performing comprehensive analysis, Conformal Litmus presents the results in a very intuitive way. All insights required to understand the CDC intent are readily available, which helps users to diagnose root cause failures easily and signoff rapidly

- Capacity: The Conformal Litmus multi-CPU parallelization infrastructure can process very large SoC-level designs and is scalable to billion gate design sizes.

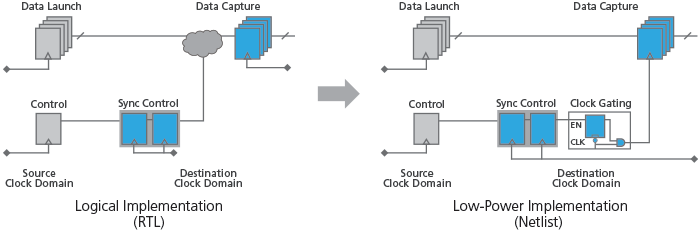

- Gate-level netlist verification: Post-synthesis, various insertion steps (such as power, test, scan etc.) can introduce unintended crossings. The Conformal Litmus gate-level netlist analysis can identify these erroneous domain crossing paths that can be potentially catastrophic for the chip

Training and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.

Find Answers in cadence technical forums