Product Overview

Tensilica Fusion G DSP Family

Multi-purpose, fxed- and foating-point DSP with exceptional out-of-the-box performance

The scalable Cadence Tensilica Fusion G DSP Family includes two high-performance, general-purpose, fixed-and floating-point vector processors: the Fusion G3 DSP and the Fusion G6 DSP. This easy-to-program DSP family, with its highly advanced auto-vectorizing compiler and optimized DSP library, provides exceptional out-of-the-box performance for both DSP and control code. Its comprehensive instruction set, along with extensive integer and foating-point data type support, make it ideal for compute-intensive signal processing applications in automotive, consumer, mobile, internet of things (IoT), and industrial applications.

Overview

Overview

As devices strive to become smarter, they need to interact more extensively with the world around them. This includes continuously innovating with newer and more sophisticated algorithms to process real-world sensor or derived data. The rapid cycle of innovation is more easily enabled by the high-performance Fusion G DSP Family, with its rich and orthogonal instruction set and high-precision fxed- and foating-point data types. Software development is simplifed with programming in C/C++, an auto-vectorizing compiler, and an extensive DSP software library, all courtesy of the mature Cadence Tensilica Xplorer integrated development environment. Further gains in performance may be achieved with the simple addition of application-specifc instructions that seamlessly integrate with the DSP’s instruction set and are fully supported by the optimized C/C++ compiler and SDK.

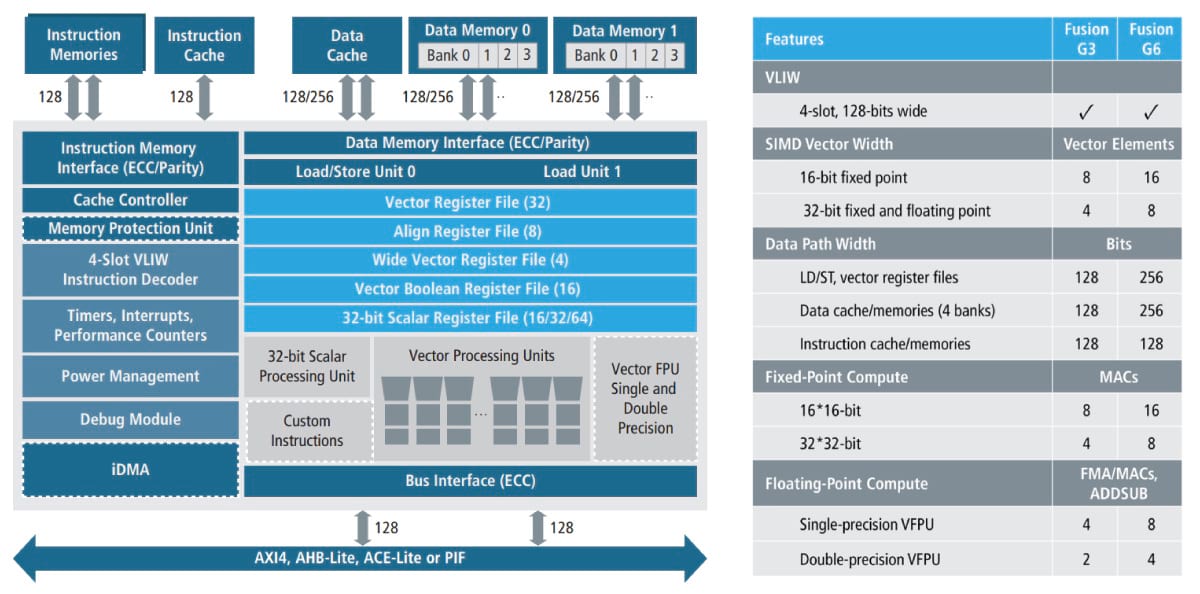

The Fusion G DSP Family features an 11-stage, 4-slot very long instruction word (VLIW) pipeline and scales with single-instruction multiple-data (SIMD) data paths. The Fusion G3 DSP supports 4-way vectorization for 32-bit integer types and single-precision foating-point. The Fusion G6 DSP doubles the performance with 8-way vectorization. Further levels of vectorization are also supported with native 8-, 16-, 32-, and 64-bit data types. Dual load-store and load units, coupled with vector and wide accumulation vector register fles ensure maximum data throughput for the computational units.

The Fusion G DSP Family is built on the confgurable Xtensa LX 32-bit scalar processor, with fexible memory and I/O subsystems, an optional integrated DMA controller (iDMA), and optional memory protection unit (MPU). The high performance, low power, and small footprint make the Fusion G DSP Family ideal for highly integrated, embedded SoC designs with single or multicore processors running real-time control and DSP applications.

Fusion G DSP Family Features and Benefits

Key Fusion G DSP Family Features

| Family Features | Fusion G3 DSP | Fusion G6 DSP |

|---|---|---|

| Load/store | Dual 128-bit load/store and 128-bit load units | Dual 256-bit load/store and 256-bit load units |

| Instruction lengths (bits) | 128, 64, 24, 16 | |

| VLIW | 128 bits wide, 2- or 4-issue slots | |

| SIMD | 2/4/8/16-way for integer, 2/4-way for foating point | 4/8/16/32-way for integer, 4/8-way for foating point |

| Data formats | 8/16/20/32/40/64/80 real integer, 32/64 real and complex foating-point | |

| Vector register fles | 32 entries x 128-bit, 4 entries x 320-bit (wide data) | 32 entries x 256-bit, 4 entries x 640-bit (wide data) |

| ALU operations/cycle | 2, 4, 8, 16 for 64, 32, 16, 8-bit | 4, 8, 16, 32 for 64, 32, 16, 8-bit |

| Multiply bit width | 8 x 8, 16 x 16, 32 x 32, 64 x 64 | |

| MACs/cycle | 1, 4, 8, 16 for 64, 32, 16, 8-bit | 2, 8, 16, 32 for 64, 32, 16, 8-bit |

| 16-bit complex MAC throughput | 2 per cycle | 4 per cycle |

| Guard bits | 4/8/16-bit on 16/32/64 types (utilizing 20/40/80-bit accumulators) | |

| Aligning load | Available in either of two slots | |

| Addressing modes | Post-increment, reverse, circular, and general | |

| Floating-point confguration options | IEEE-754 compliant, single-precision vector foating-point or single- and double-precision vector foating-point | |

| Floating-point operations | Vector MAC, FMA, ADDSUB, ALU, and type conversion, including to/from half-precision | |

| MAC/FMA/ADDSUB per cycle | 2, 4 for double, single-precision foating-point | 4, 8 for double, single-precision foating-point |

| Division/reciprocal/RSQRT | Included in ISA: integer division and foating-point division/reciprocal/RSQRT | |

| Vector-programming support | M-way, 32-bit based | |

| FFT acceleration | ADDSUB included for 2X FFT speedup (fxed- and foating-point) | |

| Image processing | Scatter gather and histogram | |

| Vector predication | ALU, MAC, LOAD/STORE, etc. | |

| DMA support | Integrated DMA controller option and support for external DMA controller | |

Toolchain and Design Flow

The Fusion G DSP Family is delivered with a complete set of software tools, including: