Cadence® Virtuoso® ADE Verifier is designed to provide the analog verification engineer or architect a global view of the circuit status. Part of the Virtuoso ADE Suite, the Virtuoso ADE Verifier works in conjunction with Virtuoso ADE Assembler, enabling tests created in those environments to be linked to the highest level design requirements and monitored to ensure all aspects of the design are coming together as planned. Together, these tools provide a cohesive and complete design solution for analog, custom, RF, and mixed-signal ICs.

Overview of Virtuoso ADE Suite

Cadence® Virtuoso® ADE Verifier is designed to provide the analog verification engineer or architect a global view of the circuit status. Part of the Virtuoso ADE Suite, the Virtuoso ADE Verifier works in conjunction with Virtuoso ADE Assembler, enabling tests created in those environments to be linked to the highest level design requirements and monitored to ensure all aspects of the design are coming together as planned. Together, these tools provide a cohesive and complete design solution for analog, custom, RF, and mixed-signal ICs.

The Virtuoso ADE Suite enables designers to fully explore, analyze, and verify a design against design goals so that they can maintain design intent throughout the design cycle. As the industry’s leading solution for analog simulation control and management, the Virtuoso ADE Suite allows users to flexibly select the product(s) that best support their design goals as they move through the design flow.

The Virtuoso ADE Explorer provides a quick entry into the analysis process with easy execution of simulations, including support for running Monte Carlo statistics, corner sweeps, pass/fail analysis, and real-time tuning with the Cadence Spectre® Simulation Platform.

The Virtuoso ADE Assembler extends the Virtuoso ADE Explorer’s capabilities across multiple testbenches simultaneously, allowing the user to monitor all aspects of the larger analog block they are creating by enabling easy and direct review of all results and generating specification-comparison sheets and datasheets as needed. The Virtuoso ADE Assembler also contains targeted features for parasitic analysis, design migration with parameter re-centering, and worst-case corner development to simplify variation analysis tasks.

To handle the key challenges of advanced-node or high-sigma designs, the Virtuoso Variation Option enables fast Monte Carlo analysis for FinFETs, high-yield estimation, mismatch contribution, sensitivity, and advanced optimization flows.

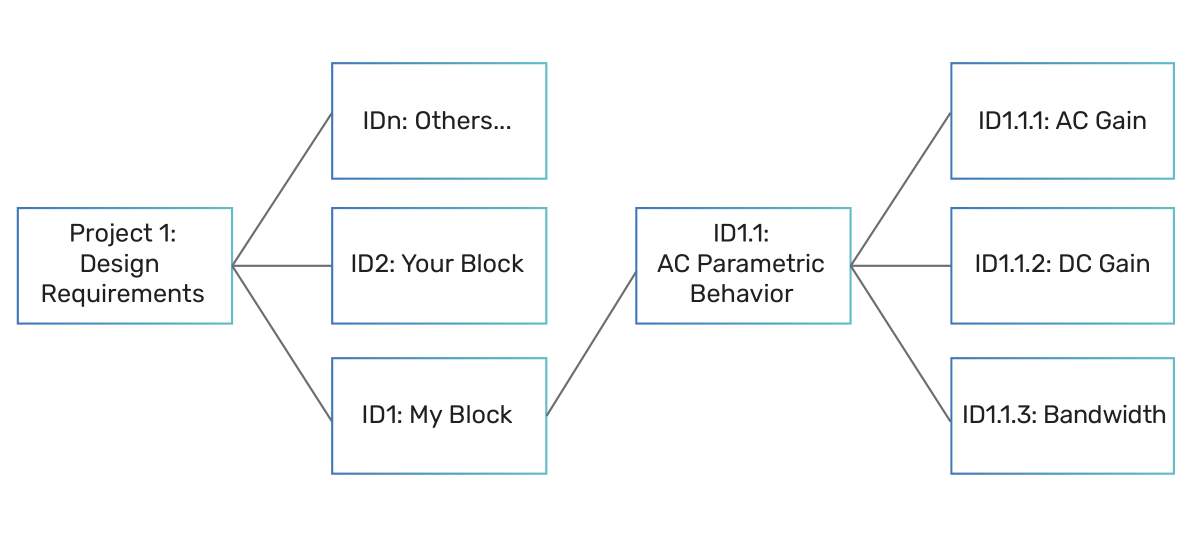

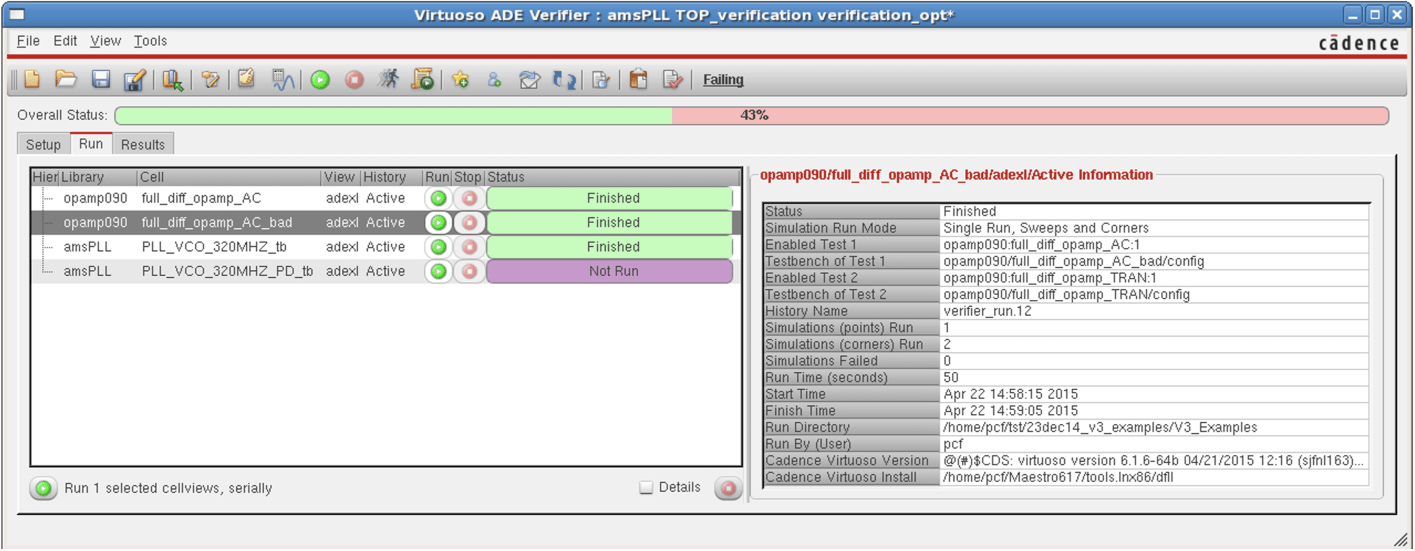

Finally, the Virtuoso ADE Assembler supplies information to the Virtuoso ADE Verifier, which is designed to match the highest level circuit specifications with individual analysis tests being developed by different users or design sites. Because status is managed in one location, as shown in Figure 1, circuit architects know the complete status of the design at all times.

Virtuoso ADE Verifier Overview

Virtuoso ADE Verifier enables analog electrical design verification, which is an unfamiliar concept to many analog design engineers. It provides a high-level overview of an entire design, linking high-level requirements such as power consumption, gain, and bandwidth to the individual tests that are being created for specification measurement. Virtuoso ADE Verifier can link together a group of specification measurement tests across multiple designers or locations and provide the pass/fail status in one easy-to-read window. The Virtuoso ADE Verifier can also quickly identify requirements that have no assigned measurements and offer visual clues if too few tests are linked to a particular measurement.

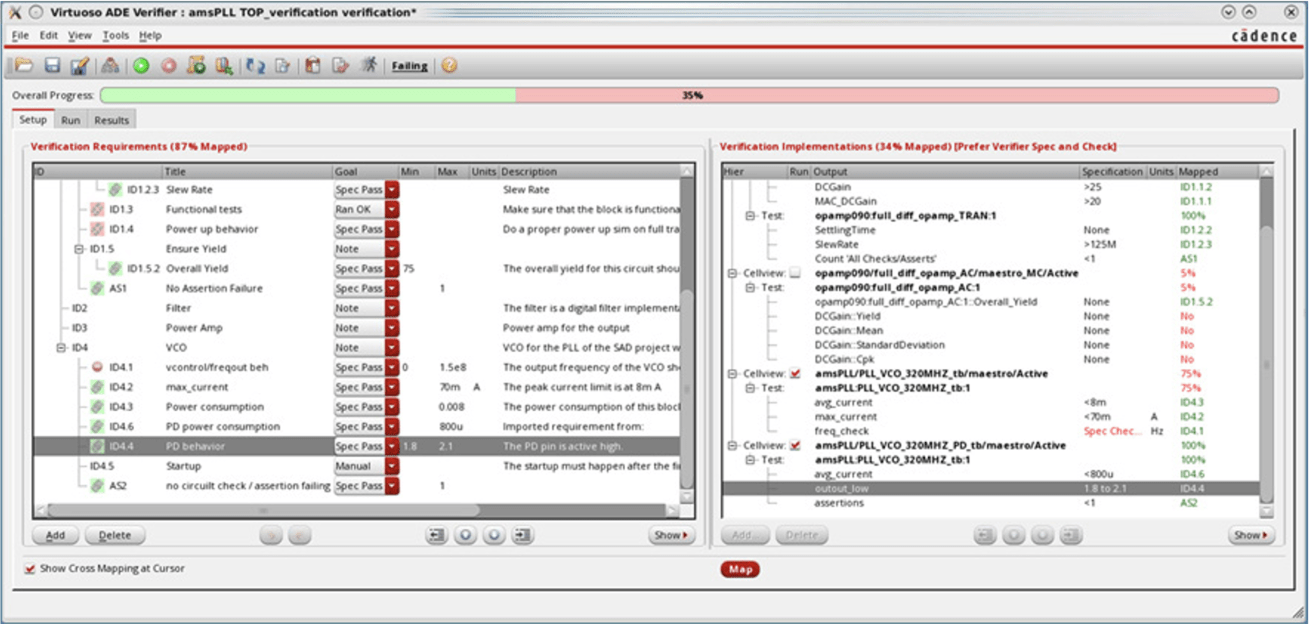

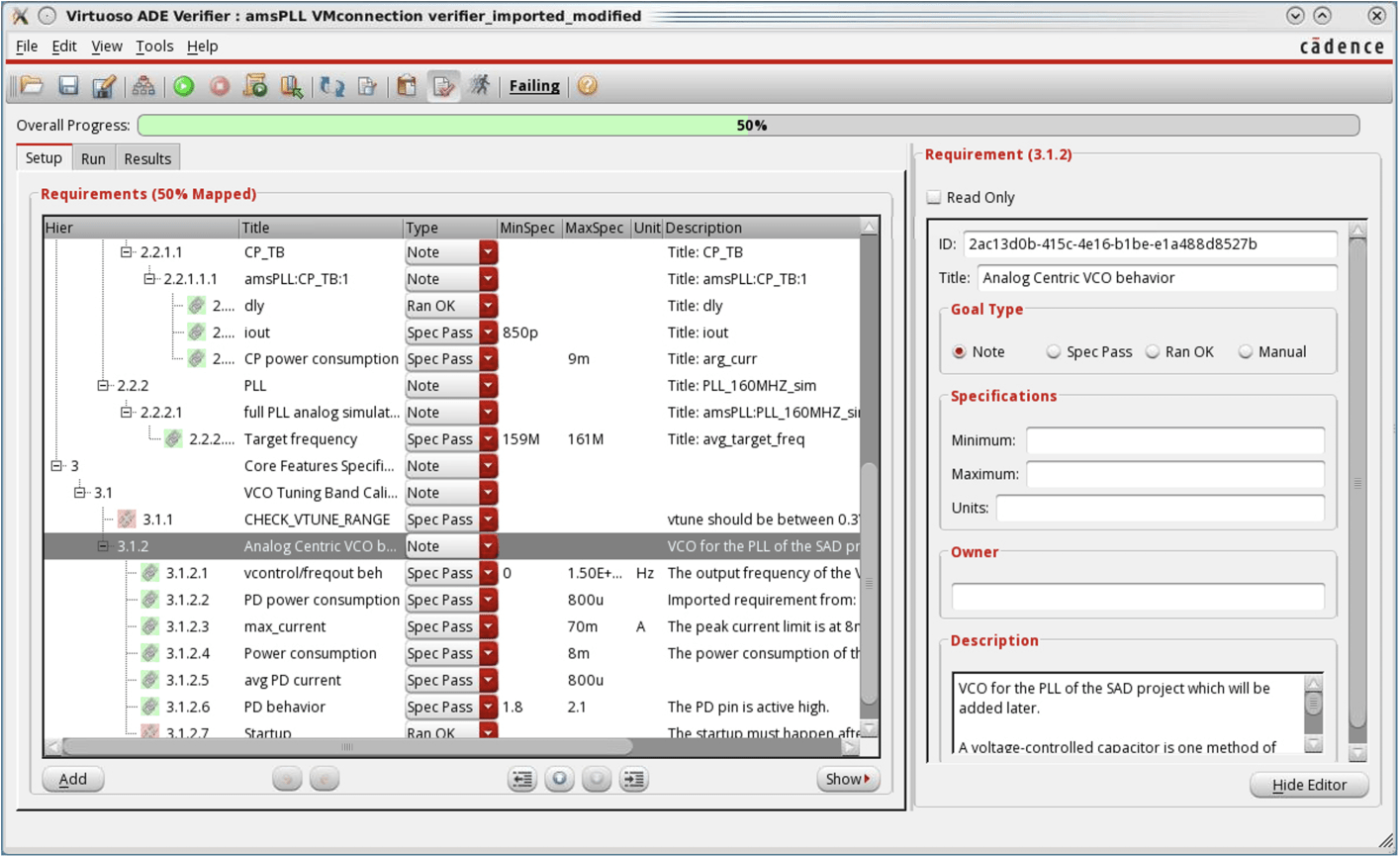

Users can choose to first enter the high-level specifications and blocks that will be tested, parceling out the specific test creation and simulations to individual engineers. Or, if the tasks have already been assigned through a traditional method, the Virtuoso ADE Verifier can load the tests and any results achieved in the Virtuoso ADE Assembler and link them to the high-level specifications. Once the connections are in place, updates are easily managed because the Virtuoso ADE Verifier is integrated into the Virtuoso platform. Regression runs can be triggered for late changes, across a single group of tests or all of them. See Figures 2 and 3.

Benefits

Features

Planning flow for analog design

Virtuoso ADE Verifier is designed to allow the entry of high-level design specifications that must be achieved by all the blocks in the design. Specific blocks can be identified, and proposed tests created and then documented to specify what needs to occur in the block design. This planning flow allows the chip architect to begin by identifying the chip “needs” first, parceling them out across the design teams to set up specific tests that measure various specifications. Once the engineers create the specific tests, which can include any capability inside the Virtuoso ADE Assembler, the tests are linked back to the high-level specification. Simulation information is also linked back so that overall design goals can be viewed and the pass/fail/run status immediately seen.

The Virtuoso ADE Verifier is designed to handle significant supporting documentation that can be used to fully document the blocks, including which tests were created and why, status of simulation runs, dates, engineers, and design location. See Figure 4.

Integration flow for analog design

Virtuoso ADE Verifier can also be used to create the high-level specification hierarchy after individual tests have already been created. This feature is useful when the design is divided among individual engineers outside of the Virtuoso platform. Bringing all the parts back together in a fully integrated cockpit makes it easy to see if tests are out-of-date, or if particular specifications have been missed or are in conflict with different parts of the design. In addition, pulling all the tests back together in a single location enables any late changes to be run by the Virtuoso ADE Verifier to see if any tests start failing. Engineers affected by failures can be notified that the change has impacted their portion of the design.

Job monitoring

Simulation jobs can be monitored whether they are run from within the GUI or use command-line scripting. The job monitor window shows test progress and can inform the architect about any failures within the run that need further investigation. Runs can be launched, sorted, and stopped from this single window. See Figure 5.