Cadence® Joules™ RTL Design Studio allows RTL designers to rapidly get early and accurate insight into the physical design effects of power, performance, area, and congestion (PPAC). Front-end designers can locate problems in the design layout, trace them to the source code, and automatically give actionable guidance to improve RTL for better PPAC. Simultaneously, implementation engineers benefit from this early debugging because they can now allocate resources to fix issues that cannot be fixed at the RTL level.

Overview

Cadence® Joules™ RTL Design Studio allows RTL designers to rapidly get early and accurate insight into the physical design effects of power, performance, area, and congestion (PPAC). Front-end designers can locate problems in the design layout, trace them to the source code, and automatically give actionable guidance to improve RTL for better PPAC. Simultaneously, implementation engineers benefit from this early debugging because they can now allocate resources to fix issues that cannot be fixed at the RTL level.

In the past, RTL designers were siloed from implementation engineers, creating a disconnect between the front end and implementation. This disconnect caused extra back-and-forth iterations between the two teams, prolonging the design cycle and significantly delaying time-to-market. Major timing and congestion issues should be resolved before handoff to achieve effective physical implementation. It is possible to solve 20%-40% of the physical implementation challenges in the RTL coding and architecture1 if accurate estimates and intelligent debug are available early enough.

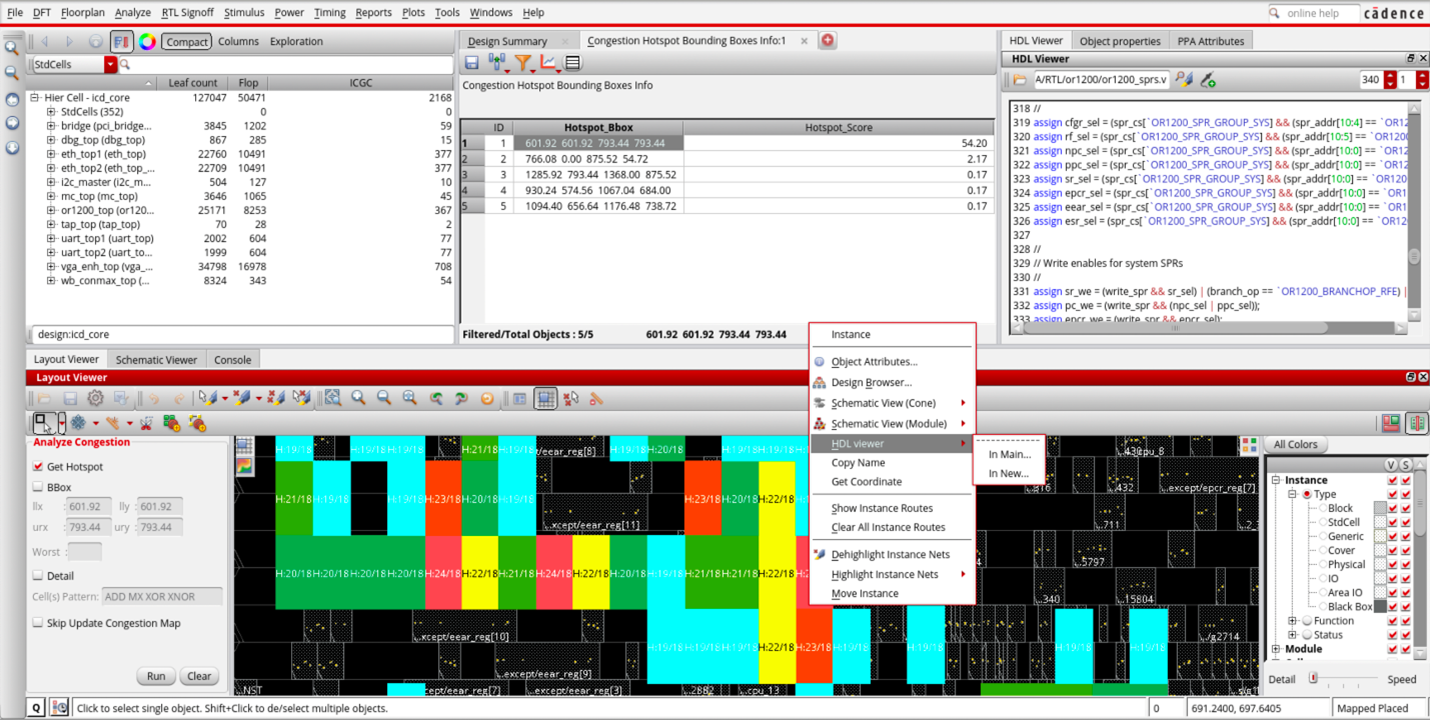

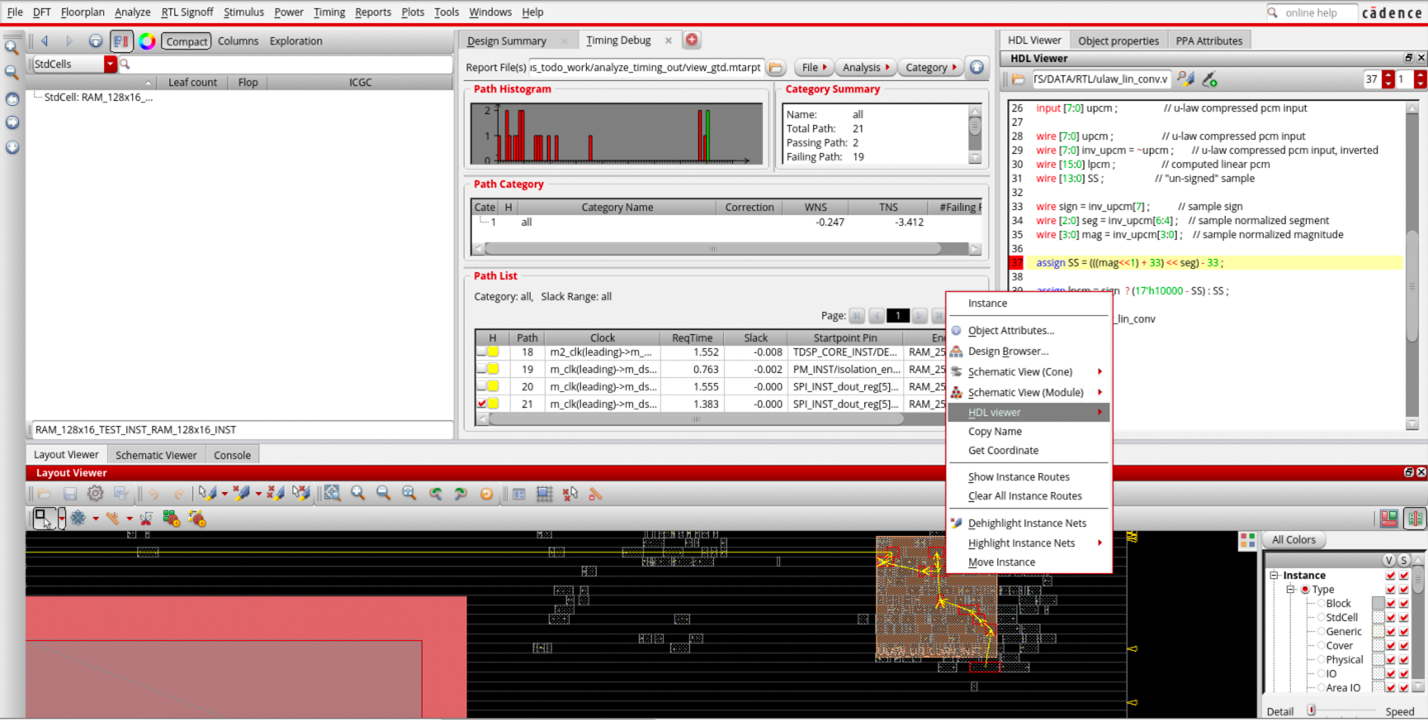

Joules RTL Design Studio assures front-end designers that the source code handoff will be fully optimized and able to achieve PPAC goals. The solution’s PPAC estimates are driven by the core engines from Cadence’s industry-leading Innovus™ Implementation System, Genus™ Synthesis Solution, and Joules RTL Power Solution, meaning that users can trust the accuracy of their design decisions. Its unique intelligent debugging assistant system sets Joules RTL Design Studio apart. This expert system triages possible causes of violations, and the additional insights empower designers to understand how to address issues in their RTL, leading to smarter and more efficient products.

Joules RTL Design Studio has tight integrations with the generative-AI solution, Cadence Cerebrus™ Intelligent Chip Explorer, to explore design space scenarios, such as floorplan optimization and frequency versus voltage tradeoffs. In addition, the Cadence Joint Enterprise Data and AI Platform integration allows trend and insight analysis across different versions of the RTL or across previous project generations.

OS Platform Support

Joules RTL Design Studio supports:

Cadence Services and Support

References

- Vanderlip, Jeff. "Physical RTL optimization solves problems early." EETimes DesignLines. November 15, 2002.