Datasheet

Assura Physical Verification

Design rule checking and layout vs. schematic verification

Cadence Assura Physical Verification—a key component of the design verification suite of tools within the Cadence Virtuoso Custom Design Platform—is the physical verification solution of choice for AMS/custom designers. It utilizes hierarchical processing and multiprocessing for fast, efficient verification in both interactive and batch mode.

Overview

Assura Physical Verification

Assura Physical Verification forms a key component of the design, parasitic extraction and simulation flow within the Virtuoso Custom Design Platform. As a trusted solution with many hundreds of users worldwide, it enables design teams to check, identify, and correct design and connectivity errors to achieve design sign-off before tape-out.

The technology uses hierarchical processing and multiprocessing techniques to rapidly facilitate accurate identification and correction of design rule errors in even the most advanced designs. With its GUI-guided debugging environment, Assura Physical Verification accelerates the debug and rework cycle and so reduces overall verification cycle time. Assura Physical Verification provides the best choice for fast and siliconaccurate analysis of custom, AMS, and RF IC designs and IP blocks.

Benefits

Features

Unified Design, Verification, and Analysis Environment

Assura Physical Verification is an integral part of the Virtuoso Custom Design Platform. Every release of Assura Physical Verification is flow tested with the other platform components. The resulting unified environment accelerates custom design, verification, analysis, and simulation leading to increased design productivity, chip performance, and silicon yield.

Performance and capacity

Assura Physical Verification uses hierarchical processing and multiprocessor techniques to increase performance and capacity. Assura Physical Verification efficiently processes highly repetitive structures (such as memory) with its hierarchical processing techniques. A hierarchical debugging capability further accelerates the debug cycle because multiple instances of errors in the same hierarchy only have to be corrected once. Finally, multiprocessing increases design throughput by leveraging costeffective and ubiquitous multi-CPU hardware.

Interactive and batch verification

Assura Physical Verification supports runs in interactive and batch mode. Interactive physical verification integrated within the Virtuoso Custom Design Platform helps designers to maximize silicon performance and yield in hand-crafted, full custom IP. Designers can then script and run Assura Physical Verification in batch mode once the custom IP blocks are assembled as a finished chip. A single rule file supports both interactive and batch verification modes.

Electrical rule checks

A comprehensive set of electrical rule check (ERC) commands verifies that designs conform to connection, tracing, and specific connectivity properties that are established for a given fabrication process or process variant. Assura Physical Verification provides full set of ERC capabilities, including:

Unique pattern checking capability

Certain advanced checks, such as metal enclosure of contact at line-end, are not easy to write and are best checked using pattern recognition methods. Assura Physical Verification incorporates unique pattern checking capabilities to accelerate advanced rule development and maintenance for checks that would be difficult to write using traditional approaches. This approach can provide up to 20x performance improvement for advanced checks, which in turn can improve the overall run-time for the entire DRC task by up to 2x.

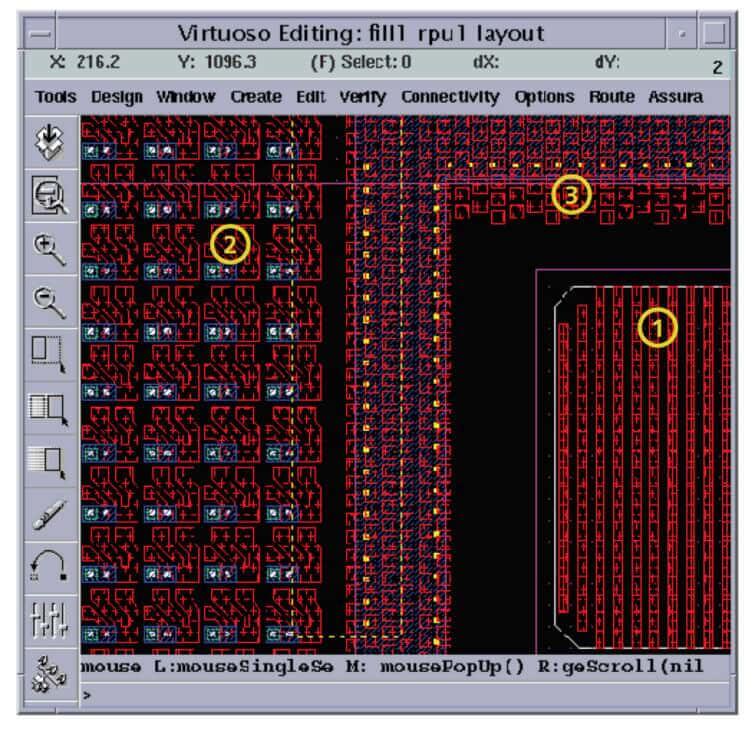

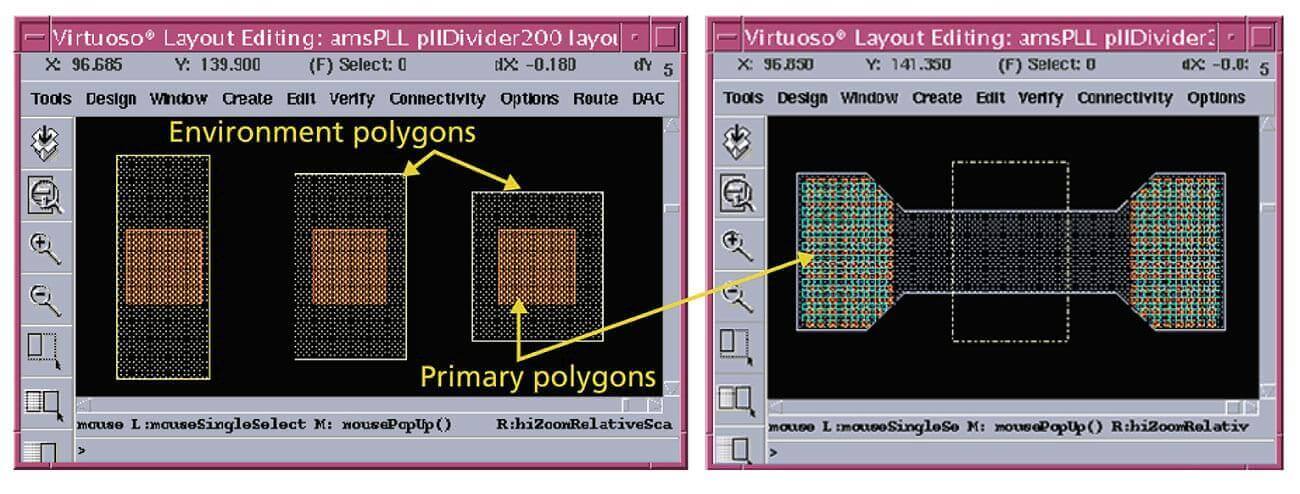

Density check and metal fill

Assura Physical Verification offers contextsensitive fill patterns, meaning users can place whatever patterns wherever they are needed in the layout. Users can customize fill patterns and shapes (e.g., custom fill cells, squares, rectangles, skewed, bridging bars) as necessary to balance layout density. The area fill command is also capable of connecting area fill features. Assura Physical Verification can perform area fill in flat or hierarchical mode.

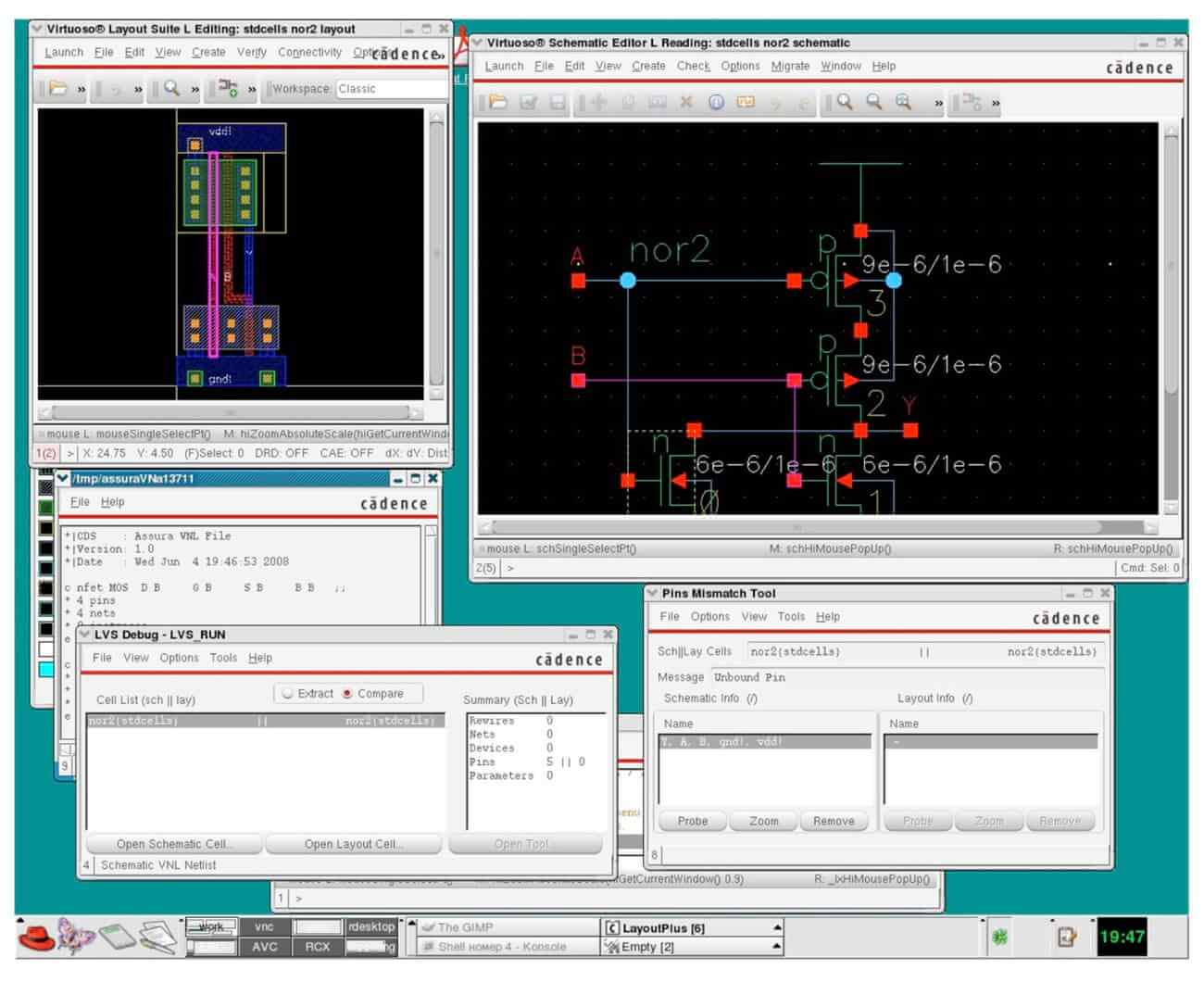

GUI-guided LVS debug environment

Assura Physical Verification offers a GUI debug environment that interactively steps users through the process of resolving LVS errors. Once the LVS run is complete, users can choose to open the LVS debug tools, such as the short locator and rewire function, from the pop-up window to examine and correct the errors.

Support of mixed-signal designs

Assura Physical Verification has the ability to recognize standard and special devices (e.g., n-terminal devices, drawn inductors, multi-emitter/collector bipolar transistors, STI, ROMs, etc.), making it an excellent choice for mixedsignal designs. All devices extracted by Assura Physical Verification are automatically netlisted and passed into Cadence QRC parasitic extraction to avoid double-counting during parasitic extraction. Assura Physical Verification also has the capability to process mixed-signal designs that combine schematics from CDL, SPICE, and Verilog.