Brochure

PHY IP for HBM2 for Samsung 10LPP

Overview

Overview

Artificial intelligence (AI), high-performance computing (HPC), image processing, and autonomous driving applications generate and consume large volumes of data and require very high memory bandwidth. The Cadence Denali PHY IP for HBM2 for the Samsung 10LPP Process is an ideal solution for meeting these high-performance applications.

The PHY IP for HBM2 is comprised of architectural improvements drawn from previous-generation DDR5 and LPDDR4 PHYs, achieving breakthrough performance, low energy per bit, and low area relative to the bandwidth provided. The PHY IP for HBM2 was developed by experienced teams with industry-leading domain expertise and extensively validated with multiple hardware platforms. It is engineered to quickly and easily integrate into SoCs, and is verified with the Denali Controller IP for HBM2 as part of a complete memory subsystem solution.

Product Details

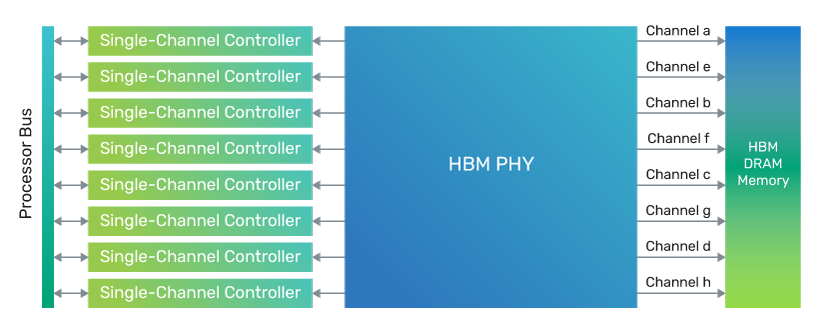

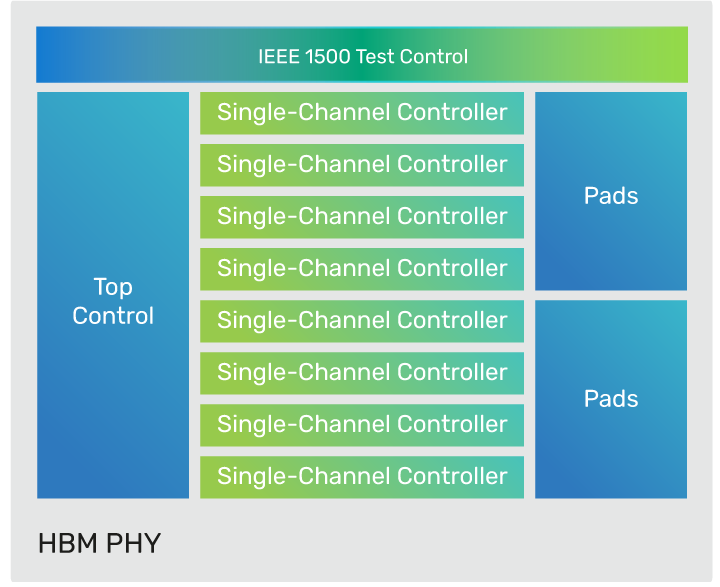

The PHY IP for HBM2 consists of a DFI interface to the memory controller for each channel, configurable PHY data slices, PHY control block (initialization and calibration logic), IEEE 1500 control block, and external register interface (configuration and test).

Benefits

Key Features

Top Control

The Top Control receives read or write requests from the controller through the external register interface. All parameters are defined through this interface to configure different features of the PHY IP for HBM2.

Single-Channel PHY

A single-channel PHY has a built-in PHY-independent (PI) leveling core, which supports training/leveling without interaction with the HBM controller.

IEEE 1500 Test Controller

The IEEE 1500 test controller provides bump connectivity testing and repair, training, temperature detection, mode register setting, and shared reset generation. It receives command requests from the PHY IP for HBM2 and implements them on the HBM DRAM stack through the standard IEEE 1500 interface. All channels of the PHY IP for HBM2 share the single test controller.

External Register Interface

The external register interface is a Cadence-proprietary interface to access the data slice registers.

Availability

The HBM2 PHY IP provides the following support:

| Protocol | Transfer Rate | Process Node |

|---|---|---|

| HBM2 | 2.4Gb/s | Samsung 10LPP |