Jasper RTL Apps

Smart formal verification apps incorporating machine learning to improve verification productivity

Key Benefits

- Finds more bugs in less time, earlier in the design process, compared to other verification methods

- Machine learning-enabled Smart Proof technology for 2X faster proofs out of the box and 5X faster regressions

- Advanced design scalability for 2X design capacity increase and 50% memory footprint reduction

- Signoff-accurate formal coverage with intuitive analysis GUI

- Eases debug and what-if analysis

The Cadence® Jasper™ RTL Apps feature machine learning technology and core formal technology enhancements.

Smart Proof Technology

The Jasper RTL Apps represent the latest stage of ongoing proof-solver algorithm and orchestration improvements. They incorporate Smart Proof technology to improve verification throughput, while machine learning is used to select and parameterize solvers to enable faster first-time proofs. Additionally, machine learning is used to optimize successive runs for regression testing, either on premises or in the cloud. With Smart Proof technology, proofs speed up on average by 2X out of the box and by 5X on regression runs.

Advanced Design Scalability

Given today’s larger and more complex SoC designs, the design compilation process sets the maximum size of design, and the compute resources necessary, to start formal analysis. The Jasper RTL Apps deliver more than 2X design compilation capacity with an average of 50% reduction in memory usage during compilation. Additionally, engineers can effectively scale design capacity through advanced parallel compilation technologies that optimally use available compute resources and run proofs in the cloud.

Formal Signoff Enhancements

Formal coverage technologies let engineers perform IP signoff purely within the Jasper RTL Apps. These formal signoff technologies include improved proof-core and checker coverage accuracy, techniques to derive meaningful coverage from deep bug hunting, and formal coverage analysis views. Ease your debug and what-if analysis with the powerful Jasper Visualize™ Interactive Debug Environment incorporating the QuietTrace™ debugging capability. Together, those features deliver signoff-quality formal coverage metrics and enable multi-engine chip-level verification closure.

![]() Request white papers on

formal verification for post-silicon debug, property synthesis, low power, register-transfer level (RTL) designer

signoff, Superlint, and cache-coherent protocols.

Request white papers on

formal verification for post-silicon debug, property synthesis, low power, register-transfer level (RTL) designer

signoff, Superlint, and cache-coherent protocols.

See What Customers Have to Say About the Jasper RTL Apps

Click through to the next section for articles and presentations.

Articles

- Cavium Adopts JasperGold Architectural Modeling by Paul McLellan, SemiWiki

- How I Unwittingly Started BRCM's Formal Verification Users Group by Normando Montecillo, Broadcom

Customer Presentations

- Evolution of Formal Usage in Arm® Austin CPU Group (JUG 2014) by Ross Weber of ARM

- Accelerating SoC Verification By Using Formal Apps in the DV Flow (CDNLive India 2015) by Siva Evani of Analog Devices

- Code Coverage Closure Using Formal Technique (CDNLive India 2014) by Kranthi Kumar of IBM, Sravani Tripura of IBM, Neelamekakannan of IBM, and Nitin Neralkar

- Formal Verification of Packet Processor (JUG 2015) by Dinker Patel of Broadcom

- Code Coverage Formal Unreachability Analysis (CDNLive EMEA 2015) by Ricardo Dantas of Dialog Semiconductor

- Bug Hunting in Deep State-Space (JUG 2015 Best Paper Award winner) by Jim Kasak of Hewlett-Packard Company

- Formal Sign-off with Formal Coverage (JUG 2015) by Ashutosh Prasad and Vigyan Singhal of OSKI Technology and Vikram Khosa of ARM

- Getting Formal with vManager (JUG 2015) by Stuart Hoad of PMC Sierra

- Why All Designers Should Do Unit-Level Verification (and Hopefully Using a Formal Tool) (When Effective) (CDNLive Israel 2015) by Ofer Sobel of Qualcomm Technologies

- NoC Functional and Deadlock Verification Using Formal (CDNLive India 2015) by Deepti Kansal, Supriya Bhattacharjee, Nirmal Arumugam, Sr., and Maruthi Srinivas of Qualcomm India Private Limited

- IPK Use, Reuse, and New Development (JUG 2015) by Lun Li of Samsung

- Solve Functional Verification Challenges Using Smart Formal Verification Approaches (CDNLive India 2015) by Harish M and Ashwini Padoor of Texas Instruments

-

Jasper RTL Apps

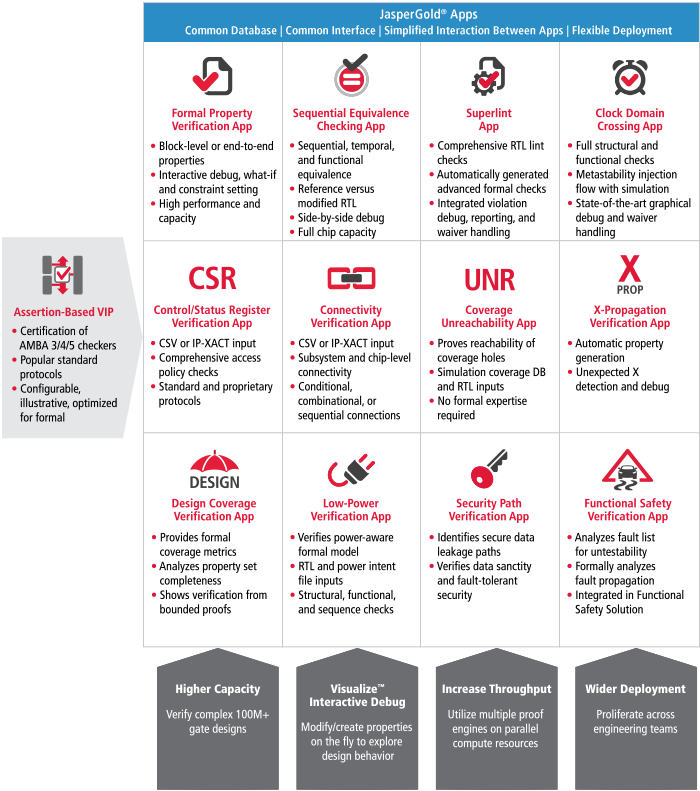

- Jasper FPV App

- Jasper Sequential Equivalence Checking App

- Jasper Design Coverage Verification App

- Jasper Coverage Unreachability App

- Jasper X-Propagation Verification App

- Jasper Control and Status Register App

- Jasper Connectivity Verification App

- Jasper Superlint App

- Jasper Behavioral Property Synthesis App

- Jasper Low-Power Verification App

- Jasper Security Path Verification App

- Jasper Clock Domain Crossing App

- [REDIRECT] Assertion-Based Verification IP

- Jasper FSV App

As long-time customers of Incisive formal and simulation solutions, we are impressed with the next-generation JasperGold platform. As well as improved debug and ease-of-use, we’ve achieved a significant increase in performance compared to Incisive Enterprise Verifier, as measured by proof convergence in a given time.

Mark Dunn, Executive Vice President, Imagination Technologies

"With the ability to find bugs weeks earlier in the design process, we’ve reduced late-stage RTL changes, which enables the team to save additional time when we get to the functional verification stage.”

Hobson Bullman Vice President and General Manager, Technology Services Group, ARM

“We’ve identified functional and structural CDC issues earlier in the RTL signoff phase using the JasperGold CDC App. Eliminating these bugs earlier in the process has increased the quality of our designs and saved us between two and four weeks on the design and verification time for each of our IP.”

David Vincenzoni Design Manager at STMicroelectronics

Scale your tools with Cadence OnCloud Marketplace

Learn MoreTraining and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.

Find Answers in cadence technical forums