overview

Fastest Simulator to Achieve Verification Closure for IP and SoC Designs

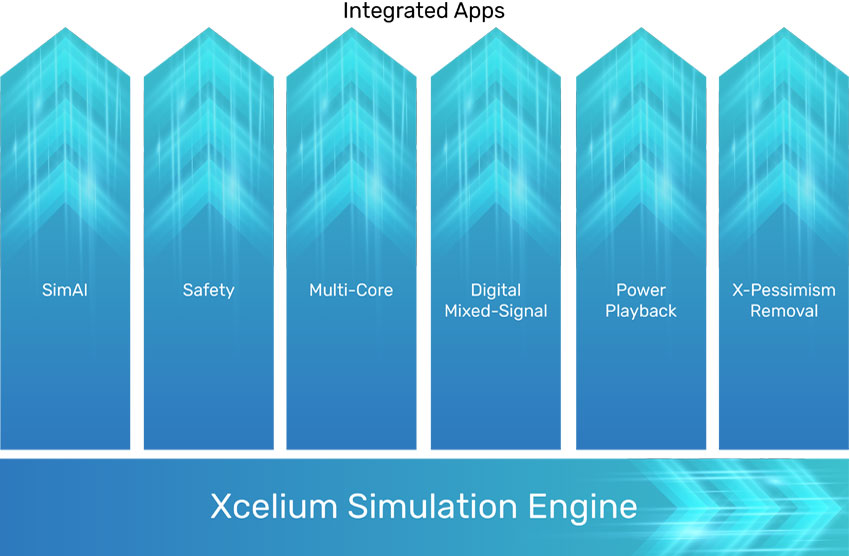

Cadence Xcelium Logic Simulator provides best-in-class core engine performance for SystemVerilog, VHDL, SystemC®, e, UVM, mixed-signal, low power, and X-propagation. It leverages a set of domain-specific apps, including mixed-signal, machine learning-based test compression, and functional safety, that enable design teams to achieve verification closure early for IP and SoC designs.

Key Benefits

Industry-Leading Simulation

Broad Language Support

Support for SystemVerilog, VHDL, SystemC, e, UVM, and IEEE UPF standards

Best-in-Class Performance

Automated parallel and incremental build technologies to support the compilation of big SoC designs and best-in-class simulation engines for best regression throughput, including a multi-core engine to speed-up long-running test cases

Accelerate with Apps

Xcelium Apps such as mixed-signal, machine learning-based test compression, and functional safety for ease of mixing and matching different technologies needed throughout the design and verification cycles

Portfolio of Apps

Xcelium Apps work natively with the Xcelium Logic Simulator and enable design teams to achieve the highest verification performance at both the IP and full-chip level of modern SoC designs.

The Xcelium SimAI App harnesses the power of machine learning technology. It builds models from regressions run in the Xcelium simulator, enabling the generation of new regressions with specific targets. This includes efficient soak testing of the entire design or specific areas and improved regression efficiency. The app also features cousin bug hunting, a unique capability that uses information from difficult-to-hit failures to expose cousin bugs. With these advanced machine learning techniques, SimAI offers the potential for a significant boost in productivity, promising an exciting future for our users.

The Xcelium Mixed-Signal App enables native co-simulation with Cadence Spectre SPICE analog simulation, as well as advanced SystemVerilog real number model-based simulation.

The Xcelium Multi-Core (MC) App significantly reduces runtime for long-running high activity tests by multi-threading the Xcelium kernel, such as on gate-level design for test pattern simulations.

The Xcelium Safety App is ISO 26262 certified and enables serial and concurrent fault simulation, which when combined with Cadence’s safety verification full flow, comprising Jasper Safety, vManager Safety, and Midas Safety Planner, enables the highest performance safety campaign execution for ISO 26262 compliance.

The Xcelium PowerPlayback (PPB) App enables massively parallel Xcelium replay of waveforms captured by Palladium emulation onto a timing-annotated gate-level netlist for glitch-accurate power estimation of multi-billion gate SoC designs.

The Xcelium X-Pessimism Removal (XPR) App shortens debug time by using advanced algorithms to make the propagation of “X” values in simulation more accurate.

Podcast Series

Espresso and Electronics – Quick Sips of EDA Wisdom

CUSTOMER STORIES

See what customers have to say about Xcelium Logic Simulator

related products

Xcelium simulation is part of the broader Cadence verification full flow and supports the company’s Intelligent System Design strategy, enabling SoC design excellence.

Scale your tools with Cadence OnCloud Marketplace

Learn MoreTraining and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.

Find Answers in cadence technical forums