システム設計者は、DDRxやPCIExpress®(PCIe®)などのプロトコルを使用して、製品のパフォーマンス、電力、帯域幅の要件をサポートしています。 デザイン・オーサリングとレイアウトツールは、設計サイクルの要求に対応するために必要なスピードと使いやすさを提供しているでしょうか? PCBのデザイン・オーサリングと実装プロセスを加速するために、階層的なインターフェース対応のアプローチを採用し、その途中で設計品質、性能、および信頼性を向上させることができたらどうでしょうか?

さて、最新バージョンのCadence® Allegro® PCBデザイン・フローでは、インターフェース対応の設計機能が強化されました。 結果は? 最大15%のデザイン・オーサリングと実装が可能です。 この機能により、より高度な抽象度でPCB設計ができるため、DDR3、DDR4、シリアルATA(SATA)、PCIeなどの標準ベース・インターフェースをより高速に配線が可能です。

今日の高速インターフェースをサポート

インターフェースを考慮した設計機能がどのように働くか見てみましょう。 伝統的なデザイン・オーサリングツールは、バスやバンドル、および信号グループの単一レベルの階層的な定義で動作します。 しかし、今日のインターフェースは単一レベルの階層でモデル化することはできません。 他の課題には、制約の増加、設計密度の増加、多ピン・デバイスの増加に伴うピンピッチの縮小、設計サイクル時間とリソースの縮小に伴う設計配線時間の増加などがあります。

インターフェースを素早く簡単に接続するために、Allegro PCBデザイン・フローには階層的なインターフェース考慮の設計機能があります:

- 高い抽象度でオーサリングを可能にして生産性を向上

- インターフェース定義をレイアウト設計者に渡す

- 重要なコンポーネント配置をガイドし、配線プランを可能にする

- 自動インタラクティブ・テクノロジーを使用して、インターフェースのブレークアウト、配線、チューニングをさらに高速化

Allegro Design Entry HDLに機能統合されたPCBスケマティック・オーサリング・テクノロジーにより、スケマティック内に新しいグラフィック・オブジェクトが使用され、インターフェースと階層ネットグループをインスタンス化することができ、コンポーネントおよびブロックへのインターフェースの構成と接続、そしてコンポーネントへのインターフェースの適用を行います。

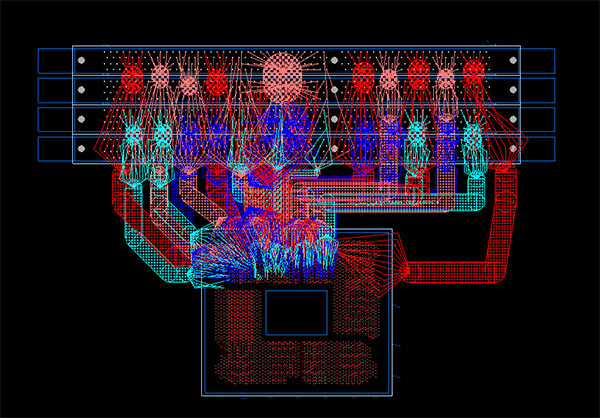

この機能は複数の階層をサポートするため、論理的な方法でグループ化された信号に制約を適用する方がはるかに簡単になります。インターフェースを意識するAllegroツールのAllegro Design Authoring、Allegro Constraint Manager、およびAllegro PCB Editorは、デザインキャンバス上のネットグループを自動的に作成し、ビジュアル的に識別します。 ツールは、また、バイトレーンを含むサブグループを含むようにネットグループを"ネスト"することができます。 インターフェースの全体的な物理ドメインをビジュアル化して、不適切な部分を表示することができます。 また、ネットグループの色分けによって、問題のある領域を簡単に特定し、適切なレイヤー分布を適用することができます。

まとめ

Allegro PCBデザイン・フローでは、階層型のインターフェース意識の設計機能を使用できるため、DDRxやPCIeなどの高速インターフェースの配線は、より高速で、より簡単な提案となります。 この機能は、さらに高いレベルのビジュアル化でPCB設計をサポートし、配置のビジュアル的な指標を提供しながら設計のオーサリングと実装を迅速化し、設計サイクルの早い段階での配線問題を特定できるようにします。