Uniquely equipped to let you perform a broad range of analysis tasks from a single tool—including electrical rule checking, interconnect model extraction, signal integrity (SI) and power integrity (PI) studies, and design-stage electromagnetic interference analysis—Cadence® Sigrity™ SPEED2000™ technology is a layout-based finite difference time-domain (FDTD) simulation tool for IC package and/or board analysis with multiple workflows to guide the user through the various analysis tasks. Included is a combination of circuit and transmission-line simulations with a fast, special-purpose electromagnetic field solver that computes dynamic interactions between signal, power, and ground on IC package and board signals and planes.

The Sigrity SPEED2000 technology is designed to work with popular chip/package/board design flows. The tool lets you perform time-domain analysis to confirm that designs meet specified targets, it understands complex voltage noise propagation (including return-path discontinuities), simulates simultaneous switching noise (SSN), and helps you identify improvement opportunities. The Sigrity SPEED2000 technology provides a transient simulation environment for both SI and PI of package and/or PCB. Interconnect model extraction can be performed to support reflection-focused (level 1) or crosstalk-focused (level 2) simulation in a pure circuit simulator such as the Cadence Sigrity SystemSI™ simulator. In addition, the Sigrity SystemSI and SPEED2000 technologies can be used together to support detailed power-aware (level 3) SI analysis using the FDTD-direct workflow.

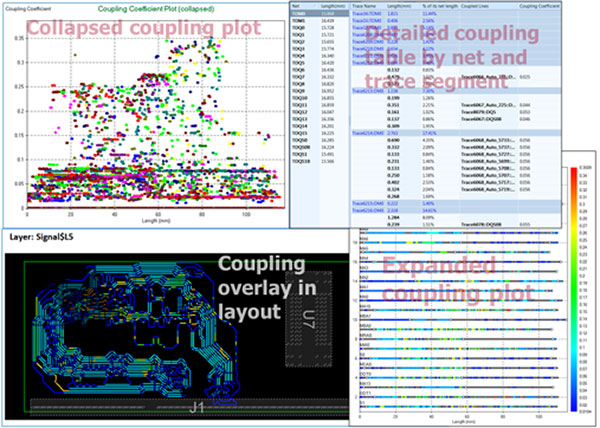

Another popular Sigrity SPEED2000 workflow is power-aware electrical rule checking (ERC). This unique technology expands beyond classic impedance and crosstalk rule checking by including estimated noise coupling from power and ground planes that may be ringing.

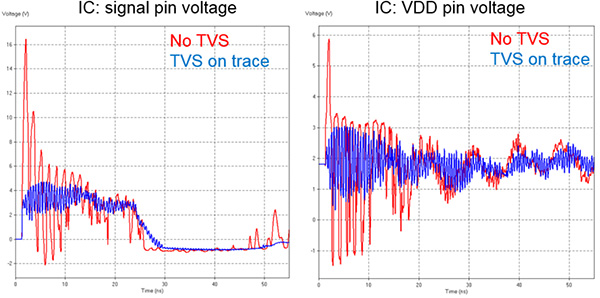

The electro-static discharge (ESD) workflow is used to test the impact of sudden and unexpected flow of electricity from an external source such as human contact or plugging in a cable with a charge. The flow includes defining the placement of an ESD gun model and then observing the impact to the board, signals, and planes. Transient-voltage-suppression (TVS) diodes and their ability to clamp the voltage peak are included in the ESD simulation.