概要

アナログ設計のベストソリューションがさらに進化

Cadence.AI Generative AI PlatformのアプリケーションであるCadence Virtuoso Studioは、カスタム/アナログ設計における30年にわたる業界知識とリーダーシップを活用し、RF、ミックスシグナル、フォトニクス、高度なヘテロジニアス設計などのシステムを幅広くサポートします。革新的な人工知能(AI)技術、クラウド対応、インフラの改善、ケイデンス製品間の統合がこれらの設計フローを補完し、実世界に向けた本物の設計を効率的に提供するためのハブを構築します。

主な利点

アナログ設計のベストソリューションがさらに進化

Virtuoso Studioカスタムデザインソリューションは、革新的な機能、比類のない生産性を実現するインフラの再構築、そして従来のデザインの枠を超えた新しいレベルの統合を提供します。

統合ソリューション

チップ設計から先端パッケージ、プリント基板レイアウトまでサポート

インフラの生産性

スループットと生産性を向上させる、プレーナーおよびFinFETベースの包括的な自動化

クラウド対応

100回のシミュレーションが1,000回になったときのために、大規模なスケーラビリティとクラウドに対応したソリューションを提供

革新的な生成AIの活用

AI対応ツールで次世代デザインを学習・改善

ヘテロジニアスの統合

RFおよびフォトニクスシステムの2.5Dまたは3Dデザインのヘテロジニアス統合を可能に

ハイライト

総合的な統合ソリューションがVirtuoso Studioの基盤

カスタムIC

ケイデンスのカスタム集積回路(IC)設計ソリューションは、回路図から設計の全フェーズを通じて自然に流れる設計意図を管理するなど、自動化とカスタムクラフトの理想的なバランスを提供します。豊富な解析環境は、レイアウト前とレイアウト後の寄生素子を考慮し、仕様と比較した回路の状態をリアルタイムに把握することを容易にします。レイアウトツールは、ルールの複雑さに関係なく、正しい 設計の接続性を促進する有効な機能を備えています。フロントエンドとバックエンドの両方が統合された検証手法は、アナログ、RF、ミックスシグナル設計において回路性能に影響を与えるすべての相互依存性を考慮し、設計の進捗状況をリアルタイムに把握することができます。

先端ノード

先端ノード・プロセスは、カスタム/アナログ設計者に対し、より厳しくなる電力と性能仕様に加え、製造とばらつきの複雑な相互依存を課しています。Cadence Virtuoso advanced-node platformは、設計者がこれらのプロセスノードのシリコンを最大限に活用できるようにする革新的な機能を備えています。

Virtuoso advanced-node platformは、これらの課題に対処するための個々のポイント・ツールを改善し、同時に、先端プロセスノードで効率的に設計するために不可欠な、迅速なレイアウトプロトタイピング、インデザインのサインオフチェック、スケマティックとレイアウト設計者の密接なコラボレーションを可能にする新しい設計手法も提供します。

ヘテロジニアス設計

異なる種類の半導体を1つのシステムに統合することで、小型化・省電力化を実現するとともに、より高性能なRF、フォトニクス、有線インターフェースを提供します。チップレット を統合することで、個別に最適なプロセスで回路を実装することができ、全体的なコスト削減と市場投入までの時間短縮につながります。Virtuoso Studioの数々の進化により、設計者は電気、電磁界、光信号のマルチファブリック協調解析や、電力・熱解析を含むシステムレベルの統合・検証など、ヘテロジニアスの設計課題に対応できます。

マイグレーション

Virtuoso Studioは、カスタムIC設計のためのマイグレーションツールの次の時代を切り開くものです。プロセスノード間のデザインマイグレーションは、多くのツールの世代にわたって進化してきました。先端ノードの顧客を支援するため、世界のファウンドリはケイデンスと協力して、スケマティックとレイアウトを新しいノードに効率的にマイグレーションする新しい技術を生み出し、最適な結果を保証するために最新の解析ツールを使用しています。

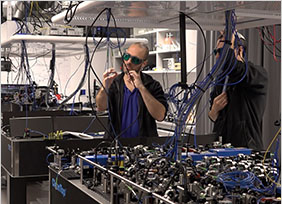

フォトニクス

Virtuoso Studioをベースにした電気/フォトニック設計自動化(EPDA)環境は、モノリシック(電子部品とフォトニック部品の両方を搭載したシングルチップ)およびハイブリッド(フォトニックICの上に従来の電子ICを搭載した3D-ICスタック)双方のアプローチをサポートしています。EPDAの包括的なフローは、スケマティックの取り込み、回路シミュレーション、スケマティックドリブン・レイアウト実装に加え、複雑なフォトニクス用SKILL PCellや高度なフォトニクスレイアウトジェネレーターをサポートします。また、ハイブリッドシステムの電子部品とフォトニクス部品の協調設計も含まれています。

RF設計

より洗練されたワイヤレス接続デバイスの需要により、高性能でコスト重視の新世代のシリコン製品が求められており、多くの場合、高集積、マルチデバイス、マルチファブリックモジュールとして実装されています。

Cadence Virtuoso RF Solutionは、時間領域と周波数領域の両方でシリコンで実証されたシミュレーション・エンジンに基づくRF解析を提供します。ミキサー、トランシーバー、パワーアンプ、デバイダ、スイッチド・キャパシタ、フィルタ、フェーズロック・ループ(PLL)など、幅広い種類のRFICについて、設計上の意図を提供し検証を可能にします。この強力な設計環境は、RFIC、RFモジュール、パッケージの協調設計をサポートし、データの手動変換による設計の失敗を排除します。

Resources

Browse Recommended Resources

Training and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.

Find Answers in cadence technical forums