White Paper

Revolution by Evolution: Getting to the Next Technology Breakthrough in Analog Simulation

近年のテクノロジーの進歩、Advanced Nodeの使用やMore than Mooreデザインにより、アナログ設計者やカスタムICの設計者は、これらの進歩から恩恵を受ける新しい設計方法を受け入れなければなりません。これらの変更により、さらに多くのポストレイアウトの寄生情報を持った大規模デザインをシミュレーションする必要性が生じました。また、フラッシュ・メモリー、MRAM、センサー・アレイなどの多くのカスタムICデザインはSPICE精度のシミュレーションが求められます。これらの要望を満たすには、現世代の回路シミュレータよりもはるかに高い性能と規模に対応した新世代のSPICEエンジンが必要です。次世代のSpectre®回路シミュレータであるSpectre X Simulatorは、アナログやミックスシグナル、カスタムICデザインのシミュレーションの次世代の要望に対処するために開発されました。

Overview

はじめに

数年前、私は、90年代後半にCadenceのIPグループが設計した10bitのパイプラインADCを使った顧客の設計を支援しました。このADCが設計された当時、SINAD(signal-to-noise and distortion)を測定するトップ階層のシミュレーションは、完了までにおおよそ 128時間を要しました。2015年に同じシミュレーションを実行すると、単一 CPU上の実行で、約10分で終了します。確かに、シミュレーション時間が向上した理由の半分は、コンピュータ・ハードウェアの性能の進歩に由来します。けれども、改善のその他の半分は、Cadence Spectre Accelerated Parallel Simulator(APS)の進歩によるものです。Spectre Accelerated Parallel Simulatorの数値計算エンジンは、シミュレーション時間を短縮しシミュレーションのデザイン・サイズを大きくするように機能改善が続けられました。マルチコア・サーバー上でのSpectre Accelerated Parallel Simulatorの実行の実際の効果は、過去には不可能だったデザインの検証が可能になったことです。例えば、この ADCの256回のMonte Carloシミュレーションを16コア・マシン上で実行すれば、3時間以内に完了します。

これで、全てのシミュレーションの問題が解決したと思うかもしれませんが、言うまでもなく話はもっと複雑です。私たちに恩恵をもたらす法則は私たちの頭痛の原因でもあります。つまり、ムーアの法則(Mooreʼs Law)[1]によりシミュレーションの性能とキャパシティが劇的に向上しますが、その一方で、設計者の生活をさらに「エキサイティング」にするという課題をもたらします。

ムーアの法則の作用から、それがアナログ設計者にどのような影響をもたらしたのかを考えてみます。回路シミュレーションに対するムーアの法則の考慮するべき影響としては、次の3つの項目が考えられます。

これらの各項目は設計全体の技術的な課題を指数関数的に増加させ、これらは設計者にも影響を与えます。アナログ・シミュレータへの依存度を高めるには、回路規模の大幅な増加や解析の課題があっても、シミュレータの性能を向上させる必要があります。

Emerging Simulation Challenges

SoC設計の最も重要な影響の1つは、デジタルの設計者が使用するのと同じプロセス・ノードを使用して高性能なアナログIPを設計しなければならないことです。そのため、アナログ設計者が過去の設計で用いた精巧なトランジスタや受動素子を使用せずに、アナログ・デザインを設計しなければなりません。その結果、設計者はディープ・サブミクロン・プロセスやAdvanced Nodeプロセスの機能(即ち、高密度ロジック)を利用してアナログ機能を実装するように、回路構成をアーキテクチャから再び考える必要があります。

New architectures

これら新しいアーキテクチャは、シミュレータに異なる要件を課します。その一方で、時間領域で線形性とノイズを解析する唯一の方法は、トランジェント解析を実行して結果をフーリエ解析し、時間領域の応答を周波数領域の応答に変換することです。この種の解析は、コンパレータのオフセット電圧の解析からPLLのVCOのキャリブレーション、ループフィルターの周波数の算出[3、4]、さらには、完全デジタルPLL[5、6]まで、さまざまなところで使用されます。他方、これらの新しいアーキテクチャは、さまざまな動作モードにおいて正確な相互作用が必要な多くの要素から構成されるため、アナログの機能検証が必要となります。回路シミュレータは、多くの異なる種類のシミュレーションが実行できるように簡単に設定を変えることができるオプションを持つように、高い柔軟性が求められます。

Post-layout challenges in advanced-node designs

ムーアの法則の二つ目の影響は、回路設計におけるプロセス・スケーリングの影響です。主要なサイズが縮小されるにつれて、インターコネクトとデバイスの寄生素子の相対的な影響が増加します。昔から、アナログ設計者は回路性能へのトランジスタの影響を解析するために、プリレイアウトの回路図のシミュレーションを使用してほとんどのデザイン・テストを実行していました。近年の傾向では、Advanced Nodeの設計の場合、トランジスタ・モデル内に多数のデバイスの寄生素子が含まれることから、たとえレイアウト前のシミュレーションでもポストレイアウトのシミュレーションの様に実行することを考えなければなりません。

Advanced Nodeトランジスタを用いた高性能なアナログ回路の設計では、寄生素子を含んだシミュレーションの必要性があり、トランジスタと寄生RC素子の比率が1:100を超える可能性があることから、課題がさらに複雑になります[7]。SerDesは、特に困難なデザインだと考えられます。SoCにデータ・コンバーターのようなアナログ・ブロックが含まれていなくても、SerDesはデジタルSoCのI/Oブロックとして機能するため、SerDesが必要となります。SerDesは、クロック/データ・リカバリー回路と組み合わせたクロック・ジェネレーターにPLL回路を使用します。結果として、SerDesの設計では、複数の設計の課題に直面します。それらは、解析されなければならない膨大な寄生素子をもたらすAdvanced Nodeトランジスタで設計されます[8]。さらに、SerDes設計では、クロック信号の信号品質を維持することが不可欠なことから、ポストレイアウト・シミュレーションが特に重要となります。寄生成分によりクロック・ラインにノイズが混入されると、結果としてSerDesの不必要な信号ジッタを生じます。

More than Moore

ムーアの法則の三つ目の影響は、More than Mooreの影響です。これは、新しいアーキテクチャを必要とする可能性がある、より大きく高度に統合された設計に現れる影響です。この影響では、スケーリングを大きくしても、デザインの統合レベルを上げることができません。代替となるのは、高度なパッケージングやスタッキング、新素材によりデザインの統合レベルを上げることです。例えば、3Dフラッシュ・メモリーと磁気メモリーの、新しいテクノロジーを考えてみます。3Dフラッシュ・メモリーは、単一のメモリー・セルに複数ビットのデータを格納することができます[9、10、11、12]。メモリー・セルへの複数ビットの格納では、SPICEを用いてのみシミュレーションが可能な精巧なプログラムと読み出しアルゴリズムが必要となります。磁気抵抗メモリーは、磁気領域に情報を格納する不揮発性メモリーの一種です。従来の不揮発性メモリーとは異なり、これらのメモリー・セルは電圧ではなく電流を使用してプログラムされます。この違いは小さく見えますが、デザインのシミュレーション方法に大きな影響を与えます[13]。電流の正確なシミュレーションは、SPICEシミュレーションを必要とします。電流の正確なシミュレーションは、SPICEシミュレーションを必要とします。

Dennard’s Law

ムーアの法則が有名な一方で、アナログ設計に影響するもう一つの「法則」に デナードの法則(Dennardʼs Law、デナード・スケーリングや比例縮小則とも呼ばれています)があります。Robert Dennard氏は「…デナード・スケーリング則では、一定のエリア・サイズに対するチップ電力の総計はプロセス世代間で同じになる。」と述べています[14]。デジタル回路とは異なり、アナログ回路の消費電力はプロセス・テクノロジーに比例しません。アナログ回路の消費電力を削減するには、新しい回路アーキテクチャとより高度な電源管理技術の開発が不可欠です。デジタルの設計者がUPF(unified power format)[ 15]などの電源管理するための自動化ツールを使用するのとは異なり、アナログ設計者はトランジスタレベルのシミュレーションによりデザインを検証する必要があります。ダイナミック・チェックなどの機能は、ローパワー設計により生じる可能性のある回路の問題を特定することに利用できるように改善が続いています。例えば、パワーダウン中の回路内のフローティング・ゲートは、リーク電流の原因となります。一方で、チェックを使用するには、回路をSPICEシミュレーションする必要があります。回路動作の各モードのみを検証するのではなく、モードを切り替えるときにも適切な動作がされているかを確認する必要があります。これは、FastSPICEのシミュレーションでは不可能な回路の動作の高速かつアナログ精度の検証を要求します。

Introducing Cadence Spectre X Simulator

Cadence Spectre X Simulatorは、25年以上にわたり業界をリードするSpectreの実績のあるシミュレーション精度を維持しながら最大10倍のパフォーマンス向上を実現する、超並列回路シミュレータです。新しいSpectre X Simulatorは、これまでのCadenceのシミュレーション・ソリューションと比較して5倍の大規模なデザインを扱うことができ、ポストレイアウトの検証フローにおいて数百万のトランジスタと数十億の寄生素子を持った回路を効果的にシミュレーションできます。新しいSpectre X Simulatorは、ミックスシグナル・シミュレーションやRF Optionに対応し、実証された精度を持ち、大規模分散シミュレーションに対応した、より高速な実行時間を実現しながら簡単に適用が可能という利点があります。

Using Spectre X Simulator for Analog and Custom IC Design and Verification

Spectre Circuit Simulatorはアナログ設計者が考慮する精度に対処するために開発され、25年以上にわたりアナログ設計のための信頼されたゴールデン・リファレンスなシミュレータです。Spectre Circuit Simulatorはアナログ設計者が考慮する精度に対処するために開発され、25年以上にわたりアナログ設計のための信頼されたゴールデン・リファレンスなシミュレータです。Spectre Circuit Simulatorはアナログ設計者が考慮する精度に対処するために開発され、25年以上にわたりアナログ設計のための信頼されたゴールデン・リファレンスなシミュレータです。

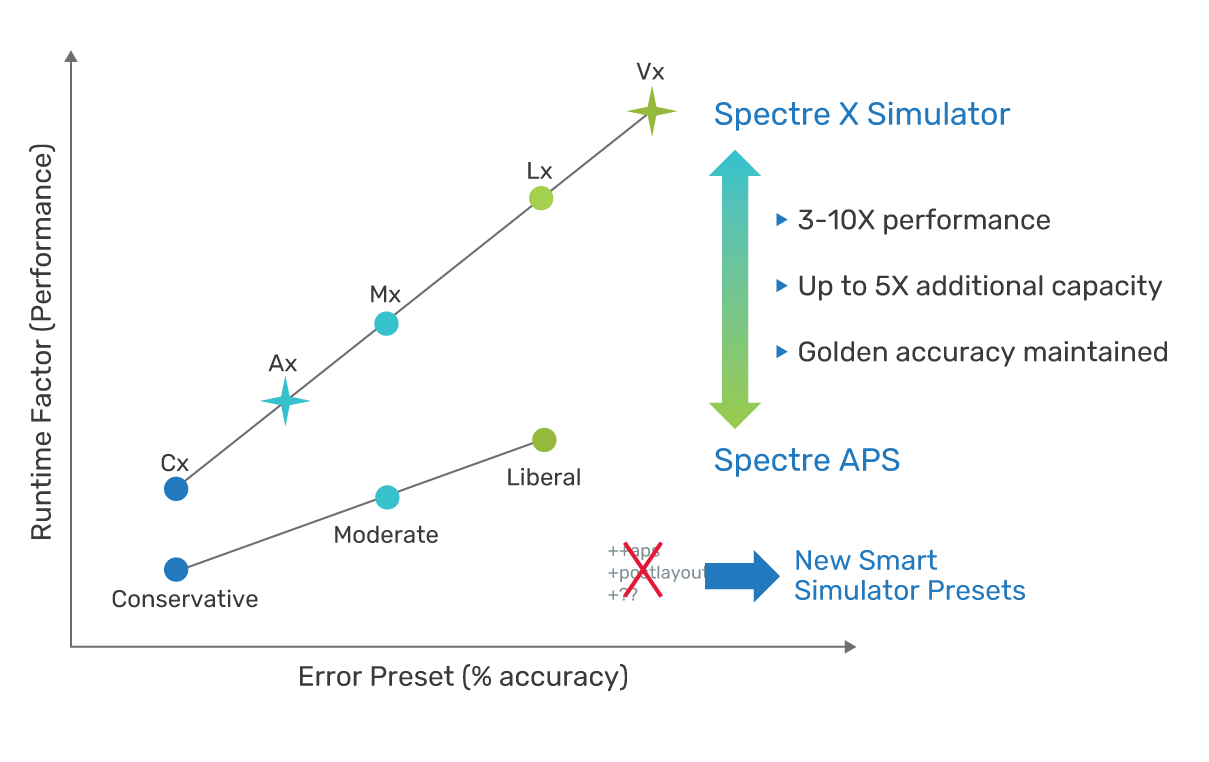

これらのエラー・プリセットはアナログ設計者に活用され、シミュレータ・オプションを個別に調整しなくても必要な精度の調整を可能にします。これらのエラー・プリセットはアナログ設計者に活用され、シミュレータ・オプションを個別に調整しなくても必要な精度の調整を可能にします。Spectre Circuit Simulatorが最初に開発されてから、シミュレーション技術は進歩しています。これにより、Spectre X Simulatorの開発とあわせてエラー・プリセットが更新されました。5つのエラー・プリセット, cx、ax、mx、lx 、vx は、Spectre Simulatorの実績のあるシミュレーション精度を維持しパフォーマンスを大きく加速しながら、より詳細にシミュレータの制御を可能にします。これらのプリ・セットは以下の様になります。

しかし、シミュレーションの実行時間を削減するだけでは十分ではありません。。既に論じているように、デザインはより多くの寄生素子を持ち、ますます大きくなり、シミュレーションのモードは増加し、さらに多くのシミュレーションの実行を必要とします。Spectre X Simulatorは、行列演算のキャパシティが拡張され、そのキャパシティはSpectre Accelerated Parallel Simulatorと比較して5倍になりました。結果、Spectre X Simulatorは、精度を落とすことなく2千万を超えるトランジスタと10億の寄生デバイスを持ったデザインのシミュレーションを可能にします。

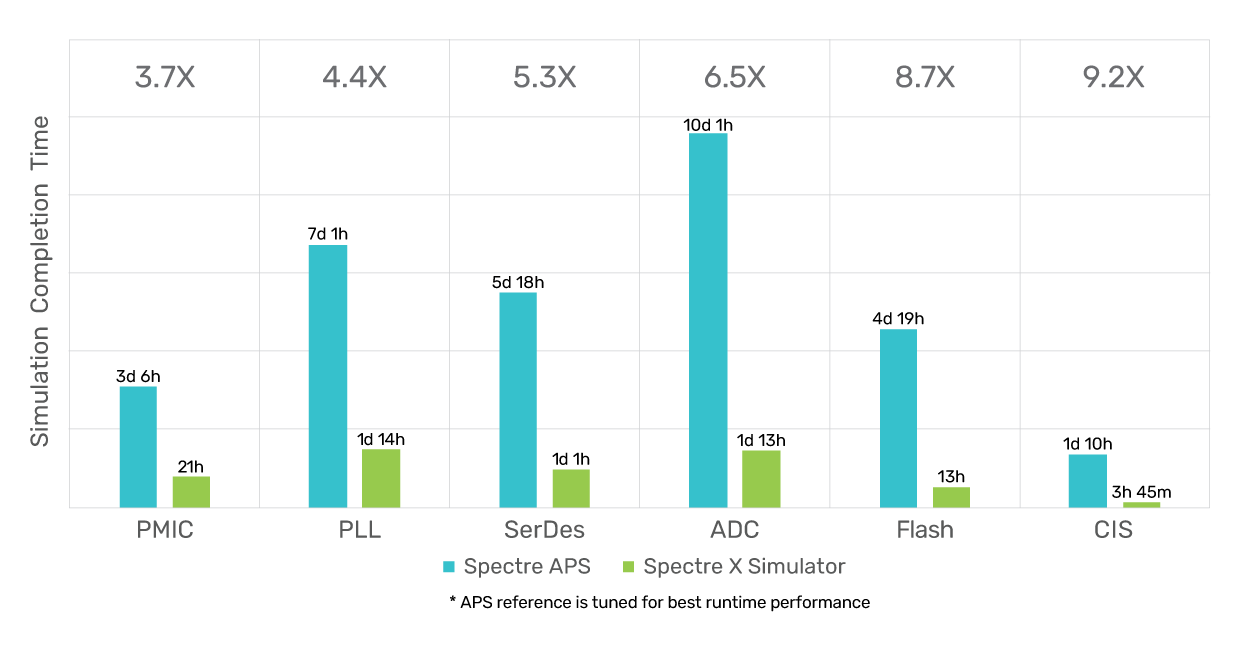

コアのシミュレーション技術の改善に加えて、Spectre X Simulatorには、設計タスクに対する マート・シミュレーション のアプローチが組み込まれています。スマート・シミュレーションは、シミュレーションされるデザインに基づいて、必要に応じて、ポストレイアウト・シミュレーションや高耐圧シミュレーション用のテクノロジーを有効にすることで、インテリジェントに最適化し、デザインに適用するシミュレータの機能です。これらの改善による効果は、幅広いデザインの検証時間を改善します。結果は、図 2を参照ください。

Massively Distributed Simulation

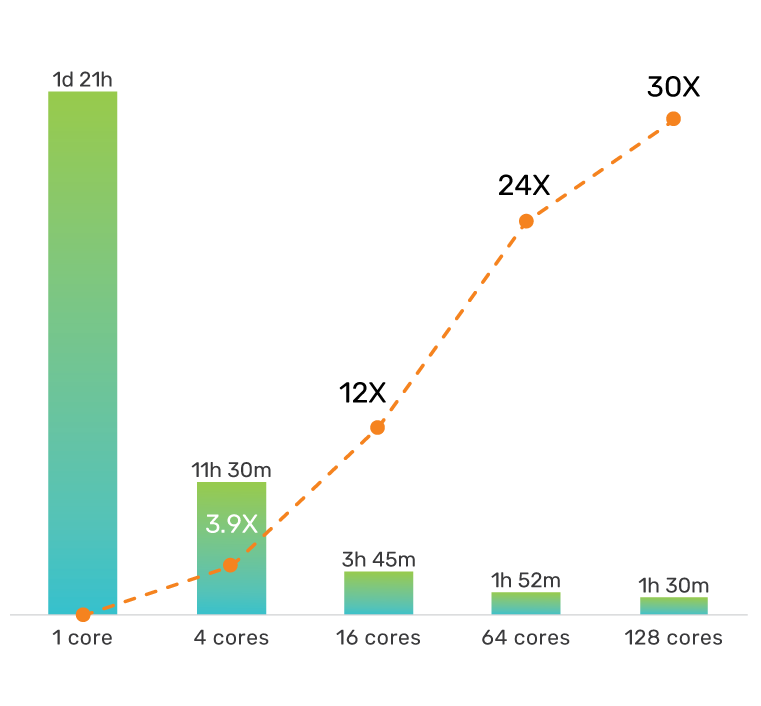

Spectre X Simulatorは、最新のコンピュータ・ハードウェアを活用して、スケーラブルに大規模に分散されたシミュレーションを実現します。このXscaleテクノロジーは、トランジェント解析およびハーモニック・バランス(HB)解析シミュレーションの効率的な分散を可能にします。Xscaleテクノロジーは、異なるマシン上の同時に最大128コアを使用したネットワーク上でテストされており、大規模並列実行を可能にして、今日の回路規模の制限を5倍に拡大します。シミュレーション・ジョブを分散する前に、シミュレーションの回路行列は部分に分割され、異なるマシン上で計算されます。シミュレーション結果の精度が低下しない様にシミュレーションを分割するために、いくつかの課題を克服しています。

CMOSイメージ・センサーは、分散シミュレーションの効果が得られるデザインの一つの例です。CMOSイメージ・センサーは、ピクセル・アレイから構成されています。画素の各カラムはADCを含む信号処理部からなるセンサーに接続されています。各信号処理部の伝達関数が他の全てのカラムの伝達関数と一致していない場合、例えば画像の背景の青空の色が変化するなど、不自然な画像になってしまうことがあります。

伝達関数の違いは、電源メッシュの電圧降下によって生じます。そのため、CMOSイメージ・センサーの解析はSPICEシミュレーションにとって難しい課題です。タイミングや電圧での要求される高い精度、デザインは物理的に大規模、シミュレーションではレイアウトの寄生情報を含む必要があります。この組み合わせにより、CMOSイメージ・センサーの検証は、これまで未解決な課題とされてきました。以下の図 3は、Spectre X Simulator を使用してCMOSイメージ・センサーを分散シミュレーションしたときの速度向上を表しています。シミュレーション時間が30倍に速度向上されたことで、1日半から1時間半に短縮されました。

採用のしやすさ

Spectre X Simulatorは、Spectre Simulation Platformに新しく追加されたシミュレータです。Spectre X SimulatorはSpectre Simulation Platform上に構築されていることから、Spectreのインフラストラクチャ機能を引き継いでいます。例えば、Spectreネットリストの読み込み、同じモデルや同じスティミュラスなどのサポートにより、Spectre Accelerated Parallel Simulatorの置き換えを可能にし、既存のデザインやテストベンチで、変更や編集を必要としないでSpectre X Simulatorの向上されたパフォーマンスやキャパシティの利用が可能です。Spectre X Simulatorの導入により、追加のエラー・プリセットを使うことができます。これは、シミュレータを調整することなく、設計要件に基づいて適切にシミュレーションの実行時間と精度の選択が可能な効果のあるモードです。ムーアの法則とデナードの法則の影響についての項では、新しいアプリケーションに対処するためのSpectre X Simulatorの必要性を説明しました。メモリーやローパワー・アプリケーションの動作検証のため、追加のエラー・プリセットの提供が必要となります。Spectre X Simulatorは、Spectre AMS Designerシミュレータのアナログ・ソルバーとして使用することができ、大規模なミックスシグナル・デザインの 検証が可能です。また、Spectre RF Optionと一緒に使用してハーモニック・バランス解析の高速化が可能です。

まとめ

次世代SPICEシミュレータであるCadenceのSpectre X Simulatorは、以下を含む、新たに設計者が直面する課題に対処するように開発されました。

Spectre Accelerated Parallel Simulatorと同様に、Spectre X Simulatorは既存のSpectre Simulation Platform上に構築され、導入コストを最小限にして、新規ユーザーも短期に使い方を習得することが可能です。

Spectre X Simulatorには新しいエラー・プリセットが導入されています。これらのエラー・プリセットにより、デザインに合わせてより柔軟なシミュレーション・パフォーマンスと精度の最適化が可能です。Spectre X Simulatorエンジンには、デバイス・モデルとポストレイアウト・シミュレーションの新しい最適化機能が組み込まれていますが、実績のあるシミュレーション精度を保ちながらパフォーマンスを向上することが可能です。Spectre X Simulatorの行列ソルバーは、従来の行列ソルバーと比較して5倍のシミュレーション・キャパシティを持っています。Spectre X Simulatorは、スケーラブルな大規模分散シミュレーションの実行が可能です。Spectre X SimulatorのXscaleテクノロジーは、最新のコンピュータ・ハードウェアを利用して、異なるマシン上の128コアへの効率的な分散シミュレーションを可能にします。Spectre X Simulatorは、近年の設計の回路性能の検証の課題に取り組むアナログ設計者およびカスタムIC設計者の要望に応えるために開発されました。

参考資料

- G. Moore, “Cramming More Components onto Integrated Circuits,” Electronics, vol. 38, no. 8, p. 114, 1965.

- M. Miyahara, Y. Asada, D. Paik, and A. Matsuzawa, “A low-noise self- calibrating dynamic comparator for high-speed ADCs,” Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC), Nov. 2008, pp. 269–272.

- Kok-Foong Chong, Liter Siek, Benjamin Lau, “A PLL with a VCO of improved PVT tolerance”, in Integrated Circuits (ISIC) 2011 13th International Symposium on, pp. 464-467, 2011.

- D. Collins, A. Keady, and R. Farrell, “Fast frequency calibration of VCO’s in phase-locked loops,” IET Irish Signals and Systems Conference (ISSC 2010), Cork, 2010, pp. 147-151.

- G. Marzin, S. Levantino, C. Samori, and A. L. Lacaita, “2.9 A Background calibration technique to control bandwidth in digital PLLs,” 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, 2014, pp. 54-55.

- S. C. Hong, “An all-digital phase-locked loop system with high performance on wideband frequency tracking,” IEEE Trans. on Circuit and Systems, vol. 52, no. 10, 2009.

- David Axelrad, “What’s in the Future for High-Speed SerDes?“, Design & Re-Use Magazine, [Online]. Available: [Accessed April 30, 2019].

- B. Fuller, “Parasitic Extraction Tips for Advanced Nodes,” ARM Community SoC Design blog [Online]. Available: [Accessed April 30, 2019].

- H Aochi, “BiCS Flash as a Future 3D Non-Volatile Memory Technology for Ultra High-Density Storage Devices”,2009 IEEE International Memory Workshop, Monterey, CA, 2009, pp.1-2.

- A. Nitayama and H. Aochi, “Bit Cost Scalable (BiCS) technology for future ultra high density memories,” 2013 International Symposium on VLSI Technology, Systems and Application (VLSI-TSA), Hsinchu, 2013, pp. 1-2.

- K. Park et al., “Three-Dimensional 128 Gb MLC Vertical nand Flash Memory with 24-WL Stacked Layers and 50 MB/s High-Speed Programming”, IEEE Journal of Solid-State Circuits,50, no. 1, pp. 204-213, Jan. 2015.

- C. Kim et al., “A 512-Gb 3-b/Cell 64-Stacked WL 3-D-NAND Flash Memory,” in IEEE Journal of Solid-State Circuits, vol. 53, no. 1, pp. 124-133, Jan. 2018.

- B. Fuller, “Circuit Design Trends: 3D-ICs Extend Scaling,” [Online]. Available: [Accessed April 30, 2019].

- R. Dennard, et al., “Design of ion-implanted MOSFETs with very small physical dimensions,” IEEE Journal of Solid-State Circuits, vol. SC-9, no. 5, pp. 256-268, Oct. 1974.

- M. Ramezani and C. Choi, “A Better Tool for Functional Verification of Low-Power Designs with IEEE 1801 UPF.” [Online] Available: [Accessed May 30, 2019]

- H. Xu and A. A. Abidi, “Analysis and Design of Regenerative Comparators for Low Offset and Noise,” in IEEE Transactions on Circuits and Systems I: Regular Papers.