Technical Brief

RF/マイクロ波設計ソフトウェア

Cadence AWR Design Environment, Version 15

Overview

はじめに

データレートと大容量化の要求を満たすために、通信、航空宇宙/防衛、および車載アプリケーションでは、MIMO(Multiple-in-Multiple-Out)およびビームステアリングフェーズドアレイに対して、より多くの帯域幅、ミリ波(mmWave)スペクトル、および空間効率が利用されています。小型でコスト重視のデバイスに対するニーズに加えて、RF/ミリ波フロントエンド部品は、これらの新しいシステム要件、実現技術の要求、およびスペース/コストの考慮事項に対応するために進化し続けています。

これらの性能、統合、コスト/スペースの目標に取り組むエンジニアリングチームは、ますます複雑化する製品要件を満たすために努力しながら、市場投入までの時間のプレッシャーに直面しています。これらの製品を市場に投入しようとするエンジニアは、広帯域およびミリ波用に設計された、より大規模で高密度の集積回路/サブシステムの性能を正確に予測するために、クラス最高の解析技術と設計自動化を必要としています

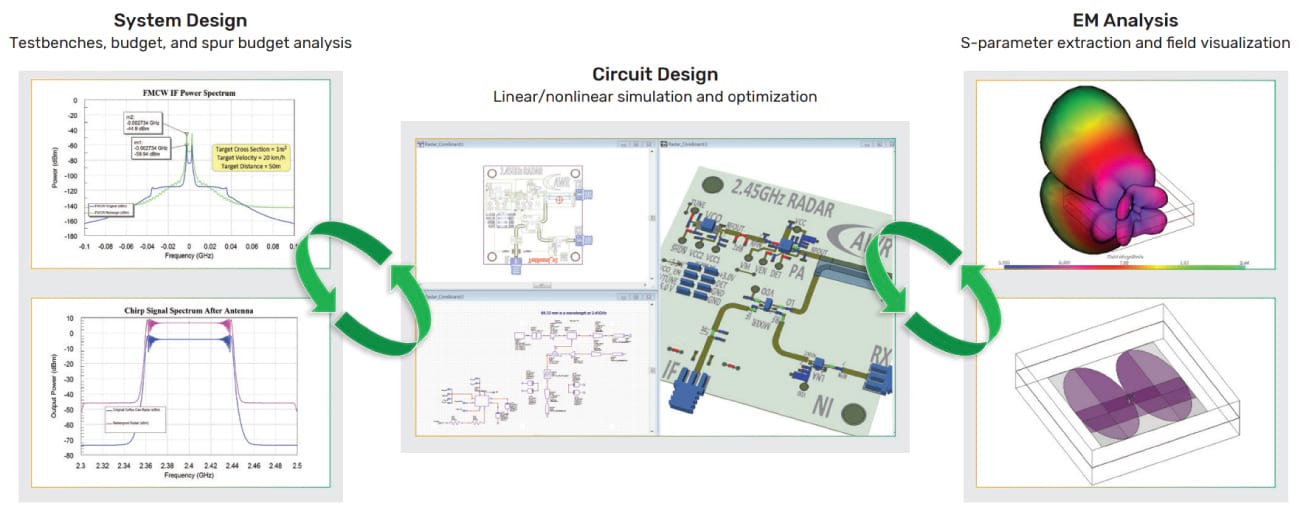

スペクトラムさらに、これらの製品は複数の設計ツールにまたがる多様なエンジニアリングチームによって開発されているため、RF設計ソフトウェアは、ミックスドシグナル電子システムの開発に使用されるより広範なクラスのEDAとの相互運用性を提供する必要があります。製品開発のスループットを最適化し、設計を成功させるには、このソフトウェアは、集積回路、システム、電磁界(EM)解析、合成、最適化をシームレスに行うとともに、エンジニアリングの生産性をサポートする自動化を提供する必要があります。これらの機能は、AWR Microwave Office、AWR Visual System Simulator(VSS)、AWR AXIEM、およびAWR Analystソフトウェアを含むCadenceのAWR Design Environmentソフトウェアに組み込まれており、RF/マイクロ波エンジニアが次世代の通信およびレーダーフロントエンドエレクトロニクスを開発するための堅牢で完全なプラットフォームを提供します。

さらに、Cadenceは、AWR Design Environmentソフトウェアのバージョン15(V15)リリースにより、電子システムのすべての設計要素に計算ソフトウェア機能を提供するインテリジェントシステム設計戦略を通じて、RF/マイクロ波の設計と統合に取り組んでいます。この戦略の中核をなすのは、クラス最高のRF、マイクロ波、ミリ波回路、システム、EM解析、半導体、パッケージ、PCB設計用のIP、クラウドでのスケーラブルなアクセスを備えた最適化されたEDAツールポートフォリオなど、優れた設計です。

V15の利点

AWR Design Environment V15は、III-Vおよびシリコン(Si)集積回路(IC)、マルチテクノロジ・モジュール、PCBアセンブリを開発および統合するエンジニアリング・チームに、設計効率の向上と初回の成功をもたらす、主要な新機能および改善された技術を提供します。新しい解析、より高速で大容量の解析技術、時間を節約する設計の自動化、パワーアンプ(PA)とアンテナ/アレイの設計、EMモデリング、ヘテロジニアス技術間のRF/マイクロ波統合をサポートする5G New Radio(NR)準拠のテストベンチにより、エンジニアリングの生産性が向上します。

設計環境と自動化

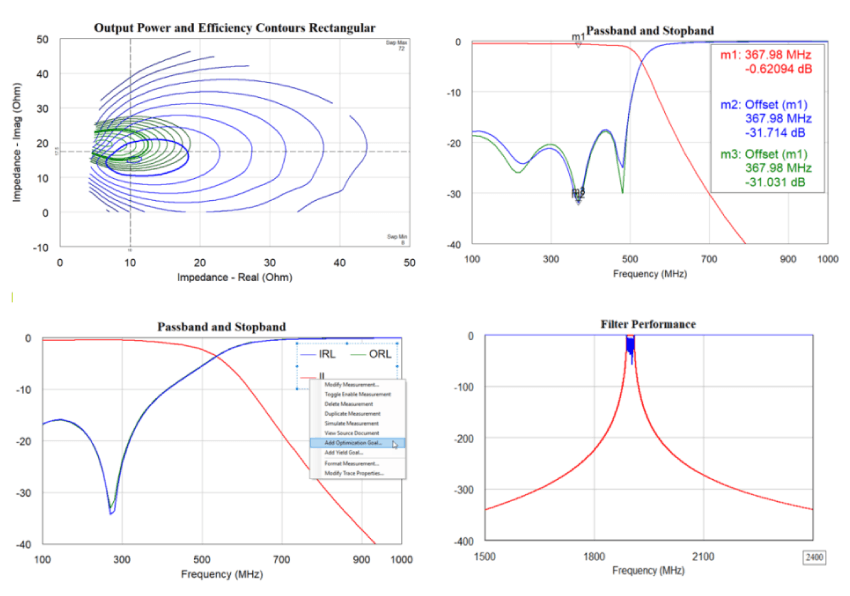

新しい設計環境と自動化機能により、個々のエンジニアやエンジニアリングチームは、設計入力、データ表示、プロジェクト管理をより効率的に行うことができます。設計者は、応答のプロットから直接最適化目標を調整し、設計ルールに準拠したインテリジェントネット(iNet)をリアルタイムで配線し、ガーバーベースのレイアウト設計をAWR Design EnvironmentにインポートしてEM解析を行い、手元の設計作業により多くのユーザー機能を提供できます。

| AWR Design Environment V15の特長 | ||||

|---|---|---|---|---|

| 環境/自動化 | 回路シミュレーション | EM解析 | システム解析 | 物理設計/レイアウト |

長方形プロットでのロードプルコンター テンプレートベースのメジャメント 最適化目標をグラフ上で直接追加/編集 色分けされたマーカーと数式のグループ化 |

迅速で厳密な安定性解析 2トーン励起用の低周波ロードプル 統合されたTX-Line計算機/合成 PDK/ベンダー部品による回路合成 |

より速く、より堅牢なアダプティブメッシング 高速で正確なDCソルバー ピークアンテナメジャメント |

事前設定済みの 5G NR テストベンチ・ライブラリ フェーズドアレイMIMOバスサポート デジタル・プリディストーション(DPD)によるPAの線形化 |

リアルタイムDRC準拠のiNetsルーティングガイド 混在可能な物理単位/グリッドのサポート 2クリックデータ入力モード プロパティページの編集によるレイアウトオブジェクトのサイズ変更 EM解析用のガーバーファイルのインポート |

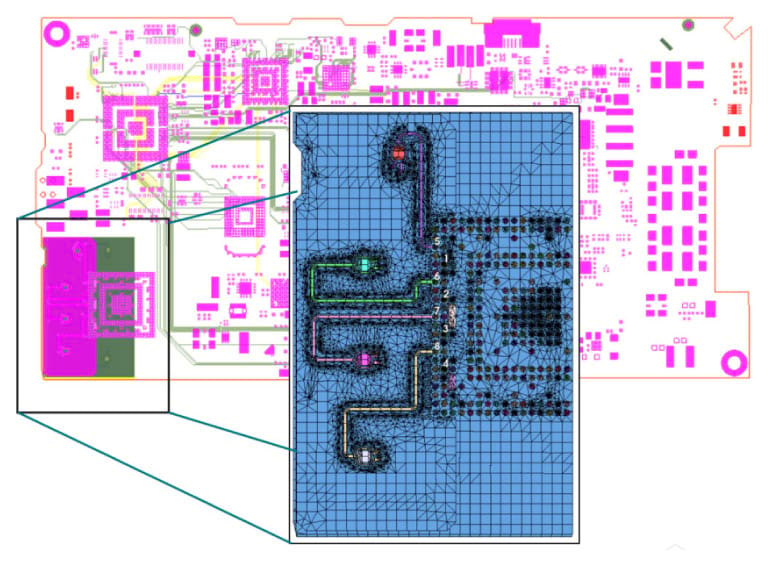

RF/ミックスド・シグナル・エレクトロニクス・システムの大型化と複雑化に対応するため、V15の新しい高速レイアウトおよび3Dビューア・レンダリング機能により、ユーザーは大型構造物のズームイン、ズームアウト、回転を行い、あらゆる角度から遅延なく物理設計を検査することができます。Cadence Allegro® PCB Designerやその他のレイアウトツールからIPC-2581またはODB++ファイルとしてインポートされた大型の基板は、PCB編集ウィザードを使用してEM解析の編集と準備を行う前に、視覚的に簡単に検査できます。

さらに、AWRソフトウェアのV15は、マルチテクノロジ・システム内でのRF/マイクロ波フロントエンド部品統合のサポートを拡張します。AWR Microwave Officeのレイヤプロセス定義ファイル(LPF)は、物理レイアウト設計のためのプロセスレイヤとパラメータを定義します。異なる半導体プロセスやラミネート基板を利用するヘテロジニアス基板やマルチチップモジュールの解析のために、AWR Design Environmentソフトウェアは、階層化が可能な単一のプロジェクト内で複数のプロセス定義をサポートします。ソフトウェアの「プロセスごとの技術」に対応するLPFの単位により、さまざまなプロセスで特定の技術に最も適した単位(ミルやミクロンなど)を指定できます。

電力増幅器の解析と設計のサポート

帯域幅の要件を満たすために、5Gシステムはサブ6GHzで連続したスペクトルと不連続なスペクトルを集約し、ミリ波周波数では利用可能な帯域幅の利点を利用しますが、どちらも高いピーク対平均電力比(PAPR)が存在する場合に直線性と効率の問題に対処する必要があるPA設計者にプレッシャーをかけます。

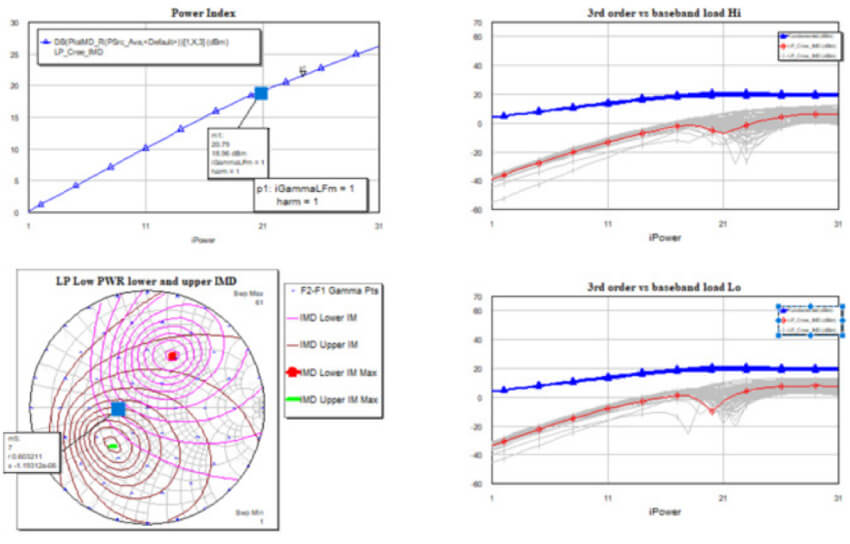

広帯域PAでは、帯域幅に対するベースバンドインピーダンスの変動がデバイスの直線性に影響を与える可能性があり、その結果、瞬時信号帯域幅に対して非対称に変化する相互変調歪み(IMD)レベルが発生します。この問題はメモリ効果に関連しており、通常、ビデオバイパスコンデンサを使用してベースバンドインピーダンスを短絡で終端することで対処されます。

ただし、別のベースバンドインピーダンス条件を考慮することで、性能を向上させることができます。たとえば、PA開発者は、エンベロープトラッキング(ET)などのアクティブなベースバンド注入アーキテクチャを採用した場合に、直線性が大幅に向上することを実証しています。

AWRソフトウェアのV15により、設計者は、2トーン励起下で動作するPAのビデオ帯域ロードプル解析を通じて、PAの直線性性能を最適化できます。設計者は、IMDと3次インターセプトポイント(IP3)の結果を(F2-F1)インピーダンスの関数としてプロットし、スィープされた入力電力に対する相互変調積を直接調査することができます。

ロードプル解析は、4次および5次高調波でのインピーダンス調整や、性能対負荷インピーダンスの視覚化を強化するための長方形プロット上の等高線生成機能もサポートしています。

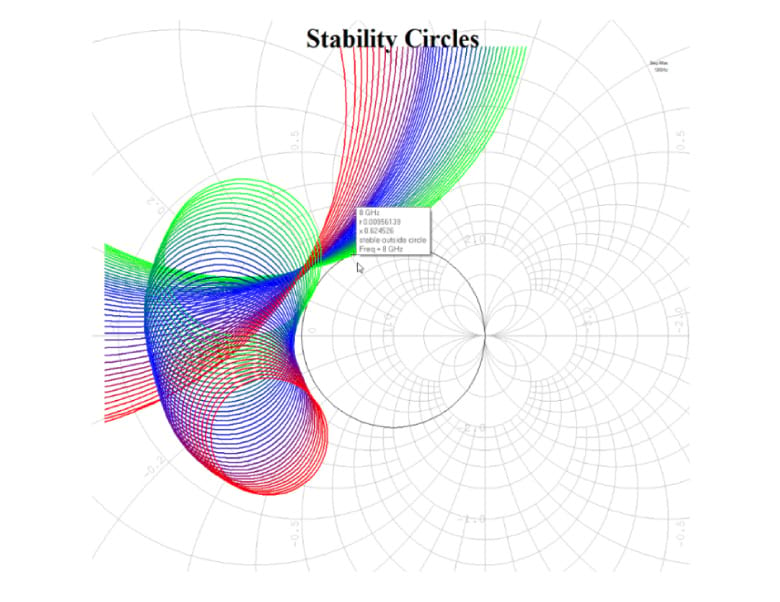

ミリ波アンプ設計用に設計されたトランジスタは、低周波数でゲインが高いため、潜在的なスプリアス発振が発生しやすくなります。 安定性解析は、アンプの設計と最適化、特にこれらの高ゲインデバイスにとって重要です。

線形回路解析から導出された一般的に使用されるKおよびμファクタは、2ポートの回路が無条件に安定しているかどうかを正確に予測できますが、並列に接続された多段アンプやデバイスの不安定性を検出することはできません。NDFやループゲイン手法などの他の安定性解析では、これらの制限を克服できますが、計算量が多くなるため、最適化を実行するには遅すぎます。

従来のループゲイン安定円の包絡線を評価するためのループ・ゲイン・エンベロープ手法は、安定性解析に対するこのより厳密なアプローチの解析時間を数時間から数秒に短縮し、安定性の最適化に理想的であることが示されています。AWRソフトウェアのV15は、ループ・ゲイン・エンベロープ・コード・モジュールとイクエーション・ブロックを使用してこの方法をサポートしており、新しいアンプ設計に簡単に適用できます。ループ・ゲイン・エンベロープ安定度解析のサポートは、設計者に以下の利点をもたらします。

従来のループゲイン安定円の包絡線を評価するためのループ・ゲイン・エンベロープ手法は、安定性解析に対するこのより厳密なアプローチの解析時間を数時間から数秒に短縮し、安定性の最適化に理想的であることが示されています。AWRソフトウェアのV15は、ループ・ゲイン・エンベロープ・コード・モジュールとイクエーション・ブロックを使用してこの方法をサポートしており、新しいアンプ設計に簡単に適用できます。ループ・ゲイン・エンベロープ安定度解析のサポートは、設計者に以下の利点をもたらします。

合成によるRF設計の高速化

伝送線路の特性インピーダンスと電気的長さ(遅延)は、1/4波長インピーダンス変換器、ウィルキンソン電力分配器/合成器、ハイブリッドカプラ、フィルタなどのパッシブRF/マイクロ波回路の周波数依存回路応答を制御するために使用される2つの重要な設計パラメータを表します。

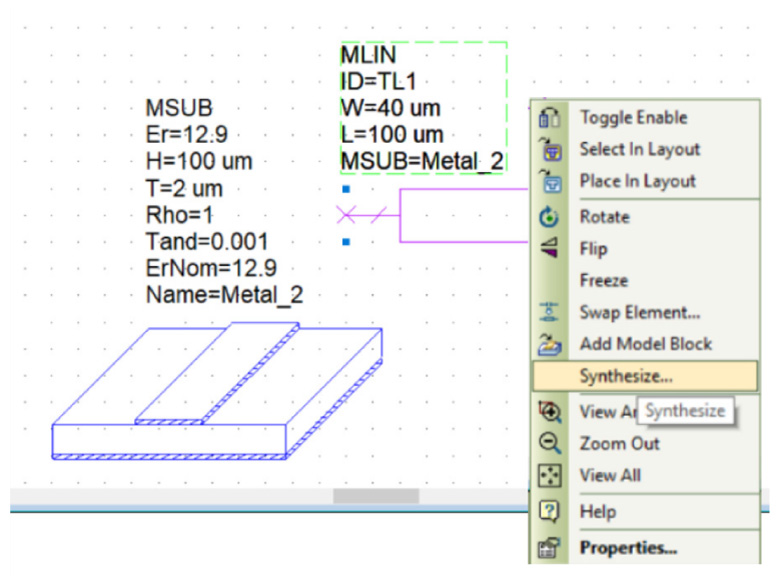

AWR Design Environment V15を使用すると、設計者は、所望の電気的特性に基づいて、特定の基板のマイクロストリップ、ストリップライン、またはコプレーナ導波路構造の物理的特性(幅、長さ)を直接合成できます。

同様に、電気的特性は、回路図に配置された単一またはエッジ結合の伝送線路の物理的特性から直接計算できます。回路モデルパラメータの合成は、伝送線路計算機を起動して、伝送線路プロパティダイアログボックスに結果を手動で転送することなく、これらの伝送線路の正確なレイアウトを生成するための重要なデータを提供します。

強力な設計支援として合成をさらに拡張する拡張された回路合成ウィザードは、表面実装PCBベースの設計用にAWR Microwave Officeベンダー・ライブラリの部品を直接使用して最適な整合回路を生成できるようにすることで、困難な広帯域およびマルチバンドPAおよび段間インピーダンスの整合回路のインピーダンス整合回路の開発を迅速化します。この機能は、プロセス・デザイン・キット(PDK)のモデルもサポートしているため、整合回路合成機能を拡張して、モノリシック・マイクロ波集積回路(MMIC)PAやその他のMMICベースの設計を含めることができます。

EM解析とアンテナ

IC、パッケージ、基板構造のEM解析の速度と規模を向上させるために、AWR AXIEMメッシングおよびソルバ技術にいくつかの重要な改善が加えられ、メッシュ品質が向上して解析の実行時間が短縮され、メッシュを縮小してより大きな問題を解決できるようになりました。

AWR Design Environment V15では、高アスペクト比ファセット(HARF)の堅牢な修復により、問題のあるメッシュファセットを自動的に検出して削除できるようになりました。このソフトウェアは、金属および誘電体のサブナノメートル(nm)のz軸分解能(以前は最も近いnmに丸められていました)をサポートしており、金属-絶縁体-金属(MIM)コンデンサなどのサブナノメートルの多層IC構造のモデリングを高速化します。

大規模のPCBとシリコン(Si)オンチップ部品の両方に、RF性能に影響を与えない製造上の特徴が含まれている可能性がありますが、問題のサイズを大きくして、EM解析が遅くなる可能性があります。AWR Design Environment V15では、形状の前処理ルールが拡張され、Siプロセス(多数の金属層を処理)に対応し、ユーザー指定のレイヤ上および指定した領域の内側/外側のアレイを介して統合できるようになりました。

さらに、AWR AXIEM DC ソルバ (バイアス回路などの低周波動作の特性評価に使用) の機能強化では、新しいスパース対称行列技術が採用され、時間とメモリ使用量が 10 倍から 100 倍節約されます。

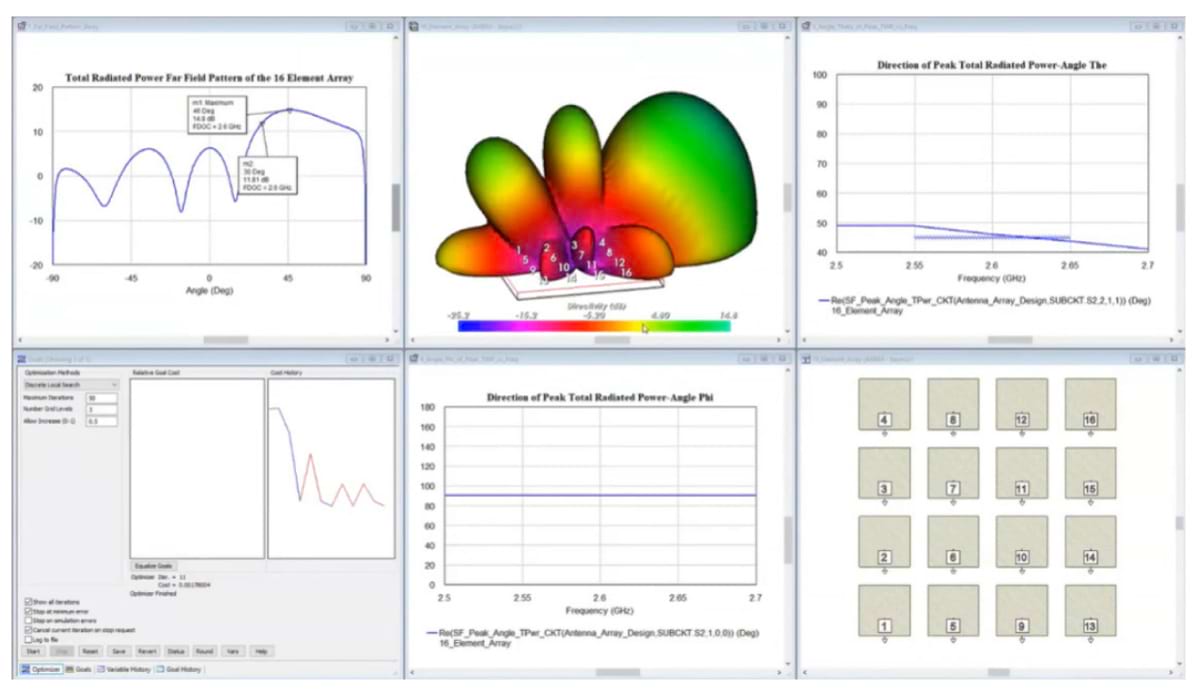

AWR Design Environmentソフトウェアを使用すると、総電力や、アンテナの「カット」全体にわたる特定の偏波の電力など、さまざまなアンテナ性能項目を確認できます。ソフトウェアのV15では、新しいピークアンテナメジャメントが導入されており、設計者はアンテナの性能を指示するための最適化目標と変数を簡単に設定できます。

たとえば、アンテナ設計者は、AWR AXIEMまたはAnalystソフトウェアを利用してフェーズドアレイ設計を、ポインティングボアサイトから特定のシータに簡単に変更できます。さらに、E-Phi、E-Theta、E-LHCP、E-RHCP、および総放射電力のアンテナ放射パターンピークを、メジャメントおよび最適化ダイアログボックスから直接、スィープされる周波数の関数としてプロットできるようになりました。これらの測定には、静的および回路駆動の両方のバリエーションがあります。

アンテナ設計者は、アンテナの負荷、回路の整合を直接解析し、Analystモデル内で周波数に依存する回路部品をモデル化できるようになりました。アンテナに埋め込まれた抵抗、インダクタ、コンデンサ(RLC)部品、および整合回路は、追加のポートや回路協調解析を使用することなく解析できます。アンテナ解析のモデル周波数依存部品を使用して、再構成可能なアンテナやより広帯域なアンテナを設計することもできます。

5G NRライブラリとDPDモデル

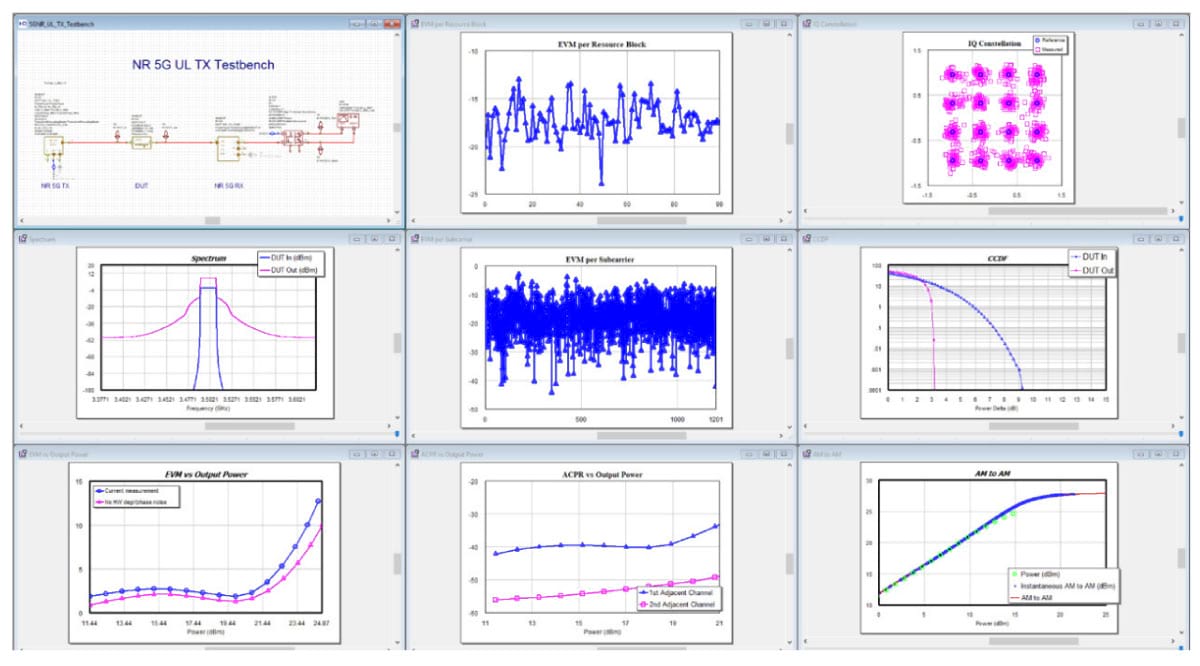

5G NRライブラリは、システムレベルの測定を使用してRF部品やRF系を評価するために使用できる、構成が簡単な信号源と受信器を提供します。新しいテストベンチは、ダウンリンクとアップリンクの両方でTX/RX機能をサポートする事前構成済みの5G NR TX/RXブロックと測定により、部品の設計と評価プロセスを加速します。

柔軟な信号構成により、可変信号電力、キャリア周波数、変調および符号化方式(MCS)、帯域幅、サブキャリア間隔をサポートし、サブ6GHz(FR1)およびミリ波(FR2)帯域の仕様で定義された要件を満たします。

5G NR受信機のテストベンチには、ビット・エラー・レート(BER)、ブロック・エラー・レート(BLER)、スループットなどの感度測定があらかじめ設定されています。新しい 5G NR TX テストベンチは、相補累積分布関数 (CCDF)、AM to AM/PM、スペクトラム、エラーベクトル振幅 (EVM)、隣接チャネル電力比 (ACPR)、IQ コンスタレーションなどの性能指標を解析するための、事前設定されたさまざまな測定による送信器の解析とデバイス検証をサポートします。

サブ6GHz帯(FR1)とミリ波帯(FR2)の両方に定義されたダウンリンク・テスト・モデルは、基地局の出力電力、不要な放射、スプリアス・エミッション、相互変調、直交位相偏移変調(QPSK)、16、64、256直交振幅変調(QAM)などのさまざまな変調タイプのEVM、周波数誤差などの測定を行うための5G NR信号を提供します。AWR ナレッジベースから入手できるサンプルプロジェクトは、Third Generation Partnership Project (3GPP) TS 38.141 Section 4.9.2 に従って構成された NR 5G 送信器および受信器を実証し、事前構成済みのシステム・ダイアグラムと関連する結果グラフを含み、解析の準備が整っています。

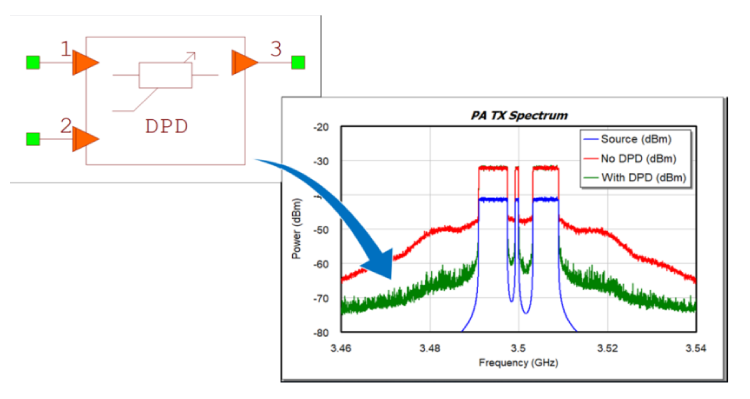

AWR Design Environment V15には、非線形アンプを線形化するアルゴリズムを提供する新しいデジタル・プリディストーション(DPD)ブロックも含まれています。この DPD モデルは、メモリ多項式、一般化メモリ多項式、2 次動的偏差低減 (DDR2)、およびルックアップテーブルをサポートしています。新しいモデルを実証するために、AWR Microwave Officeソフトウェアに実装されたPAに給電するドライバアンプを使用して、サンプルプロジェクトを作成しました(AWR KnowledgeBaseから入手可能)。AWR Microwave Officeのサブサーキットは、マルチユーザータイプの動作を解析するように構成された3.5GHzの直交周波数分割多重(OFDM)信号によってAWR VSSシステム設計ソフトウェアで励起されます。

DPD モデルでは、デバイス出力からのフィードバック信号が信号源の信号と共に、選択したアルゴリズムの初期計算と増分更新に使用されます。このブロックには、DPD の初期設定に使用できるさまざまなソルバーが用意されています。その結果、DPDがある場合とない場合のデバイス性能を比較し、スペクトル再成長、IQコンスタレーション歪み、およびCCDFの改善が示されました。市販のDPDソリューションのオプションも用意されており、ラボと同じアルゴリズムを解析で実行できます。

まとめ

AWR Design Environment V15ソフトウェアは、Cadence のEDAソリューションポートフォリオに、新しく強化されたRF/マイクロ波設計および解析を提供します。高度な設計自動化により、手作業による設計タスクを削減し、ツールの相互運用性をサポートすることで、エンジニアリングのスループットと生産性を最適化します。

新しい回路解析機能は、多段アンプと平衡アンプの高速かつ厳密な非線形安定性解析と、相互変調歪みを低減するために低周波インピーダンス終端を最適化するビデオ帯域のロードプルに対応しています。回路合成は、ベンダーの部品とPDKを使用したインピーダンス整合回路開発と、回路図から直接起動する新しい統合伝送線路計算機能と合成機能をサポートします。

堅牢な解析エンジンは、チップ、パッケージ、基板の特性評価において、強化されたメッシングとスマートな形状処理を備えたEM解析を使用して、大規模な構造をより迅速に解析します。 事前設定された5G NR準拠のテストベンチは、PAおよびRF系の検証用の信号源と測定を提供します。