Datasheet

Stratus High-Level Synthesis

仕様からシリコンまでの最速パス

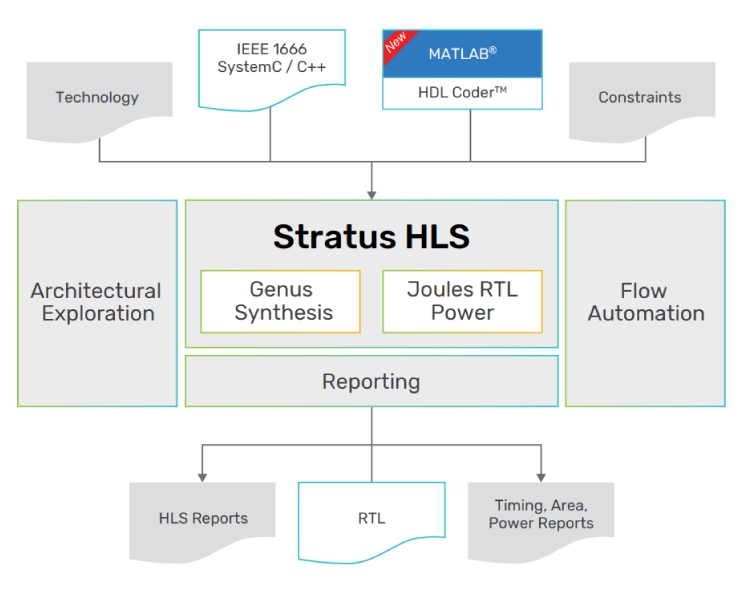

Cadence Stratus High-Level Synthesis (HLS) は、抽象度の高い IEEE 1666 SystemC、C++、および MATLAB 記述から、ASIC、システムオンチップ(SoC)、およびFPGAをターゲットとした高品質なレジスタトランスファレベル(RTL)の設計インプリメンテーションを自動的に実現します。Stratus HLS による製品設計は、一貫した高品質な結果、完成された機能性、完全な設計カバレッジなど、その成功例は世界中に広がっています。画像処理、ワイヤレス、マシンラーニング(ML) アプリケーションに最も広く使用されているほか、Stratus HLSのテクノロジで作られた製品は、家や自動車からポケットの中まで、多くの場面で活用されています。

Overview

概要

Stratus HLS により、設計チームは抽象度の高い IEEE 1666 合成可能なSystemC、C、C++、 MATLAB モデルから、高品質の RTLインプリメンテーションを迅速に設計、検証することができます。モデルはStratus integrated design environment (IDE) を使用して容易に設計可能です。Stratus HLSの合成可能な SystemC IP は、一般の算術演算やデータ型と同様に、汎用バスインタフェースやポイントツーポイント通信プロトコルのシミュレーションおよび合成モデルを提供します。

Stratus HLS の設計環境では、Cadence Genus synthesisやJoules RTL power エンジンを活用することで、パワー、パフォーマンス、エリア(PPA) の結果は、通常、手書きRTL で達成される結果と同等、もしくはそれ以上になります。フロントエンド設計者はCadenceデジタルフローとの完全な統合を通じて、高品質な PPA 見積りを取得します。

Stratus HLS を使用すると、SystemC、C、C++、MATLAB モデルを新しいテクノロジプラットフォームにリターゲットでき、従来の手書き RTL より簡単に再利用できます。Stratus graphical user interface (GUI) を使用すると、設計者は高位合成環境内から PPAのトレードオフを動的情報や静的情報から評価することもできます。

Stratus HLS はtransaction-level models (TLM) からゲートまでの、何百ものブロックの設計・検証フローを自動化します。さらに、Stratus HLS は、Cadence ツール群のフルフローと緊密に統合しているため、フローの終盤に短期での解決が要求されるengineering change orders (ECO) とレイアウト上での配線性の問題の現実的な解決に役立ちます。

特長

IEEE 1666 SystemC、C、C++ 合成

Stratus HLS は、業界標準の IEEE 1666 SystemC および C、C++ のセマンティクスをサポートします。

SystemC クラスライブラリはモジュール化、並列化、ビット精度を提供し、設計者は使い慣れた階層化を使用して、設計の複雑さを管理できます。SystemC は階層とマルチスレッドをサポートすることにより、同時動作するアルゴリズムとそのインターフェイスの設計・検証を可能にします。

Stratus HLS では、ハードウェアインターフェイスを備えたハードウェアモジュールのコンテキストに、C または C++ アルゴリズムコードを自動的に配置することもできます。

幅広い適用性

Stratus HLSの利用と共に構築されたシリコンは、世界中の数多くの製品に組み込まれています。それら製品は、画像処理、ワイヤレス、および MLアプリケーションの分野で最も広く使用されているほか、幅広いアプリケーションで使用されています。

Stratus HLS は、アンタイムド、タイムドの SystemC および C++ モデル (両方の混在を含む) をサポートし、設計者に最大限の柔軟性を提供します。出力は、設計仕様に合わせて、最大スループットの実現に向け完全パイプライン化 (サイクルごとに新しいデータ)、スループットを低下させてパイプライン化(複数サイクルごとに新しいデータ)、またはパイプライン化しないこともできます。また、ハードストールやソフトストール、パイプラインデータドレインやバブルスカッシングなど、複数のパイプラインストールモードもサポートしています。Stratus HLS は、生成RTLのfinitestate machine (FSM)、データパス、およびメモリインターフェイスが、最も複雑なストールシナリオであっても正しく実装されることを保証します。

Stratus IP ビルディングブロックには、アプリケーション固有の IP と汎用 IP が含まれます。たとえば、Stratus ラインバッファ IP は画像処理および動画アプリケーションで、複雑なデータ型はワイヤレスアプリケーションで広く使用されます。また、浮動小数点型の bfloat のサポートには ML 、artificial intelligence (AI)アプリケーションで使用されます。一方で、すべての設計において、ポイントツーポイントおよびバスベースの通信 IP を活用できます。

階層設計

Stratus HLS は、単一のブロック、または HLS ブロックと RTL ブロックの両方を含むモジュールの複雑な階層に適用可能です。Stratus HLSの設計と検証の自動化により、設計者は 一つ、部分、またはすべてのモジュールを合成し、SystemC と RTL を組み合わせたシミュレーションや検証を行うことができます。

各モジュールには、一つ、またはそれ以上の SystemC スレッドやメソッドを用意します。そして、 Stratus 通信IP を使用し、各モジュールを SystemC または RTL としてシミュレートできますStratus 通信 IP を使用しても SystemC と RTL の混在シミュレーションが可能であり、またユーザはSystemCとRTL間を接続するために複雑な混在シミュレーション環境を準備する必要はありません。また、設計が複数のクロックドメインを持っていたとしても、Stratus clock-domain crossing (CDC) IP により、信号がクロック境界を越えて正しく伝搬されます。

Stratus HLS は、階層モジュールの作成もサポートします。設計者が関数単体や生成されるFSM、データパスを個別のモジュールとして実装することも可能です。Stratus HLS では、SystemCコードを複雑に書き直す代わりに、Tcl やディレクティブを使用して、これを行うことができます。

Stratus HLS は、メモリテストポートを最上位モジュールに引き上げたり、メモリをモジュール階層の外側に抽出したりする機能を含め、階層内外での多様なメモリの実装方法をサポートしています。

Cadenceベリフィケーションスイートと統合された Stratus HLS は、アサーション、デバッグ、波形、元の SystemC 設計へのリンクなど、自動化された言語混在 (SystemC および RTL) 検証とデバッグをサポートします。

GUI

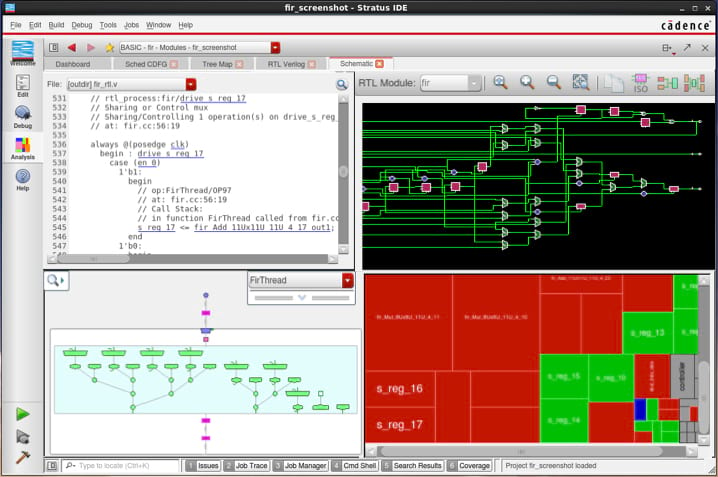

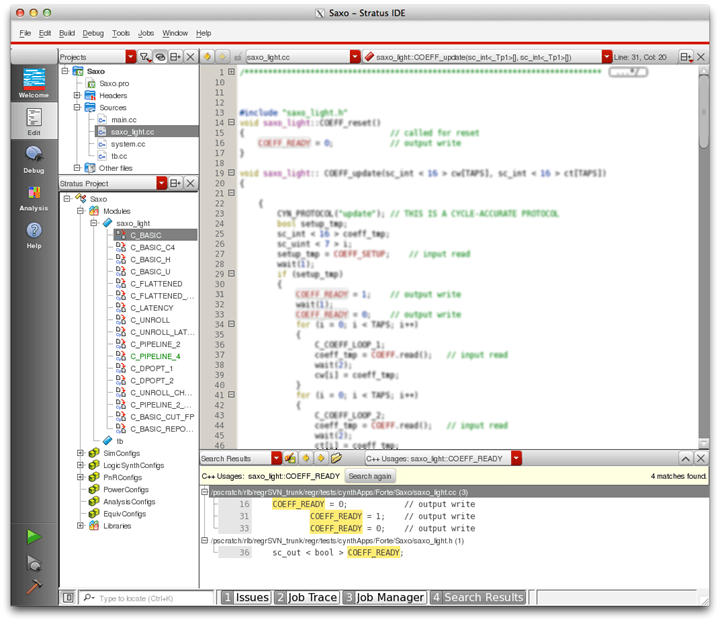

Stratus GUI には IDE が内蔵されており、新規ユーザー、上級ユーザー共に、簡単かつ直感的にSystemC開発を行うことができます。標準的な IDE 機能に加え、Stratus IDE を使用すると、事前に定義された設計テンプレートを使用して、新たなモデルを簡単かつ迅速に作成でき、設計とデバッグにかかる時間を短縮できます。

Stratus 解析環境には、SystemC および RTLソースリンク、コントロール/データフローグラフ、スケマティックビューワ、パイプライン解析のほか、アーキテクチャの最適化に対する影響を判断するための QoR レポートおよび可視化機能が含まれています。一般的には GUI 経由で最も多用されますが、このような解析は Stratus Tcl API 経由でも使用できます。

IP ビルディングブロック

Stratus HLS は、設計者が短期間で設計を立ち上げられるように、合成可能なビルディングブロックを提供しており、 IP ライブラリと Stratusインターフェイスジェネレーターが含まれています。最適化されたこれらの機能IPは高位のSystemC コードで実装されているため、性能やエリアを損なうことなくRTLに実装可能です。その結果、設計・検証プロセスを加速する、真の再利用可能な設計 IP となります。

Stratus IP ライブラリには、高速シミュレーションモデルとビット精度合成可能なモデルが含まれています。

設計・検証フローの自動化

Stratus HLS は、完全に統合された自動化システムを搭載しています。一つの Tcl ファイルから、以下のすべての設定と自動化が可能です。

この自動化により、設計者は Stratus HLS を使用して複数のアーキテクチャとインプリメンテーションを検討できると同時に、設計初期の TLMモデルからゲートまで一貫した環境を提供することで検証を向上させることができます。

ECOサポート

設計フローのどの時点でも設計変更が必要になる場合があります。設計フローの後半で変更が発生した場合でも、Stratus HLSのECOモードは開発スケジュールへの影響を最小化する際に有効です。

新たにRTL を作成して RTL-GDSIIインプリメンテーション全体を完全にやり直す代わりに、Stratus HLS は最小限の変更で RTLインプリメンテーションを作成します。Cadence Conformal ECO Designer が ECO パッチを作成し、設計やスケジュールに対する変更の影響を最小限に抑えることができます。

Conformal ECO Designer と連携すると、パッチはネットリスト、配置配線された設計、またはメタルオンリーの ECO が可能な場合は、ポストマスクネットリストでも適用できます。これにより、パッチが正しく、設計はQoR目標を満たします。

ローパワー最適化

Stratus HLS により、設計チームは、ファイングレインドブロックレベルのクロックゲーティング、FSM 最適化、パワー指向の演算スケジューリング (再順序付け) など、手書きのRTL では実現が困難または不可能な、複雑なローパワー最適化を自動化できます。

設計者は、Stratus HLS の探索機能を使用して、設計 PPAを迅速にトレードオフすることができます。MLにおける精度や無線通信における損失など、アプリケーションにより、追加で考慮が必要なクライテリアもあります。

これらの最適化により、設計によってはローパワー最適化による最大50%の電力削減が可能になります。

設計収束

Stratus HLS は、生成RTL に対し、各パスを徹底的に解析し、演算をスケジュールすることで、より容易に、タイミング収束を実現し、指定のクロック周期内に収めます。

Stratus HLS は、データパス最適化テクノロジ(特許取得済み)と組み込みGenus synthesis により、指定されたテクノロジライブラリを用いてデータパスコンポーネント、マルチプレクサ、レジスタを構築し、正確なタイミングとエリアのモデルを生成します。

ユーザーはStratus HLSが各クロック周期に演算をどれだけ積極的に落とし込むかを制御することができます。Stratus HLSの活用により、タイミング収束の問題解決に費やされる、数ヶ月に及ぶバックエンドでの作業期間が短縮できます。

フロントエンド設計者は、Stratus HLSとGenus physical synthesisとの統合により、配線混雑の問題を早期に可視化してフィードバックすることで、早期にバックエンドの問題を回避できます。

ビヘイビア IPの再利用

Stratus HLS は、ビヘイビアIP の作成と適用を可能にし、真のIP再利用を提供します。

Stratus HLS を使用すると、検証済みのソースコードを変更せずに、様々なプロセステクノロジ、クロック周波数、PPA ターゲットに対して再利用できます。アルゴリズム、アーキテクチャ、インターフェイスの変更は、高位設計で段階的に行うことができ、以前のような広範な RTL 書き換えは不要となります。

ビヘイビア IPの再利用をすることで、設計全体の工数が大幅に削減され、return on investment (ROI) が最大化されます。