Datasheet

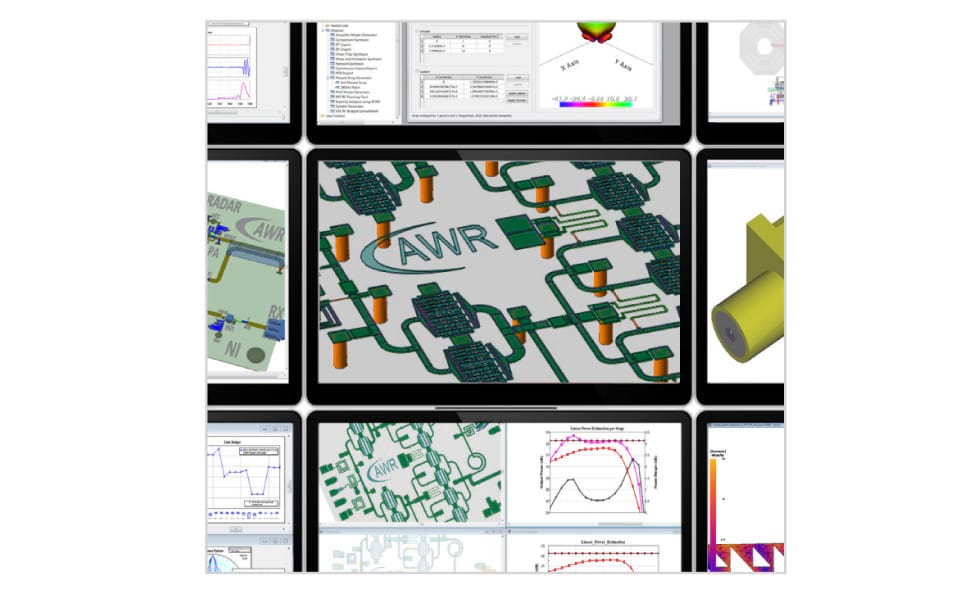

AWRソフトウェアを活用したMMIC設計

MMICの製品開発を支える解析と設計フローの技術

III-V 族半導体デバイスは、モバイルデバイス、通信インフラ、航空宇宙アプリケーション向けに優れた RF 性能を提供します。最適な性能を実現するには、信頼性の高い回路解析、電磁界(EM)検証、通信テストベンチ、および電気設計を物理的実現につなげる設計フローが必要です。Cadence AWR Design Environmentソフトウェアは、革新的なユーザーインターフェイスと、エンジニアリングの生産性を高め、初回での成功を保証する設計入力、解析、および物理設計ツールの完全な統合を備えた、最先端のフロントツーバックのモノリシックマイクロ波集積回路(MMIC)設計フローを提供します。

Overview

製品の強み

設計管理

高度なレポート/測定管理により、設計者は複数の解析結果を同時に追跡し、単一の場所で測定データソースとパラメータを管理し、単一のダッシュボード表示でリンクされたレポートの組み合わせを作成できます。簡略化されたパワーアンプ(PA)測定では、アンプの性能を表す一般的な方法である、出力電力に対する利得の圧縮や効率などの非線形測定を簡単にプロットできます。

解析

回路ベースのアノテーションは、電流密度と重要な電圧に関する解析のフィードバックを即座に提供し、レイアウトを行うずっと前に信頼性の問題を正確に指摘します。統合されたデータベースのアーキテクチャは、電気設計と物理設計を動的にリンクして、その場での EM 検証と製造準備が整ったレイアウトを実現します。

Cadence AWR APLAC ハーモニックバランス (HB) シミュレータは、線形および非線形の周波数領域解析と時間領域の過渡解析を組み合わせており、その速度と最も困難な問題でも収束することで知られています。これは、非線形性の高い問題、アクティブなデバイス数が多い回路、およびマルチトーン条件下で動作する MMIC に対処します。

製造のための設計

製造向け設計 (DFM) は AWR ソフトウェアプラットフォームに組み込まれており、ファウンドリに認定されている PDK でプロセス固有の金属線路とオンチップ部品に対して正確なモデリングを提供しています。GDSII レイアウトファイルの出力は、専用の製造ツールへの設計情報の転送をサポートします。

主要なMMICファウンドリと協力して開発されたPDKは、AWR Design Environmentソフトウェアを使用するエンジニアに、回路図、スケーラブルなレイアウトのパラメータ化セル(PCell)、高度なレイアウト機能、接続チェック/ハイライト表示に加え、事前定義された基板スタックアップと事前構成された解析設定による正確なEM解析を提供します。

AWR ソフトウェアのお客様は、設計の失敗を減らすことで収益性を最大化します。ソフトウェア内の歩留まりおよびコーナー解析は、設計者が回路性能の統計的変動を調査し、既知のプロセス公差に基づいて指定されたパラメータの公称値を変更することで製造歩留まりを最適化するのに役立ちます。