Datasheet

Conformal ECO Designer

ECO automation for greater predictability and design convergence

Cadence Conformal ECO Designer enables designers to implement RTL engineering change orders (ECOs) for pre-and post-mask layout, and offers early ECO prototyping capabilities for driving critical Yes/No project decisions. Cadence ECO solutions combine automatic ECO analysis, logic optimization, and design netlist modification with world-class equivalence checking to provide superior performance, productivity, and predictability, helping you achieve convergence on your design goals.

Overview

Cadence ECO Solutions

After transistors and layout are finalized, designers must use Engineering Change Orders (ECOs) to implement surgicalchanges to designs without requiring the schedule cost of re-running a full implementation flow. All ECOs focus on delivering products to market as soon as possible with minimum violations. ECOs can span a variety of scenarios from adding or removing logic in a design, to more subtle changes such as cleaning up routing; Cadence offers the only truly automated ECO solution from RTL to GDSII.

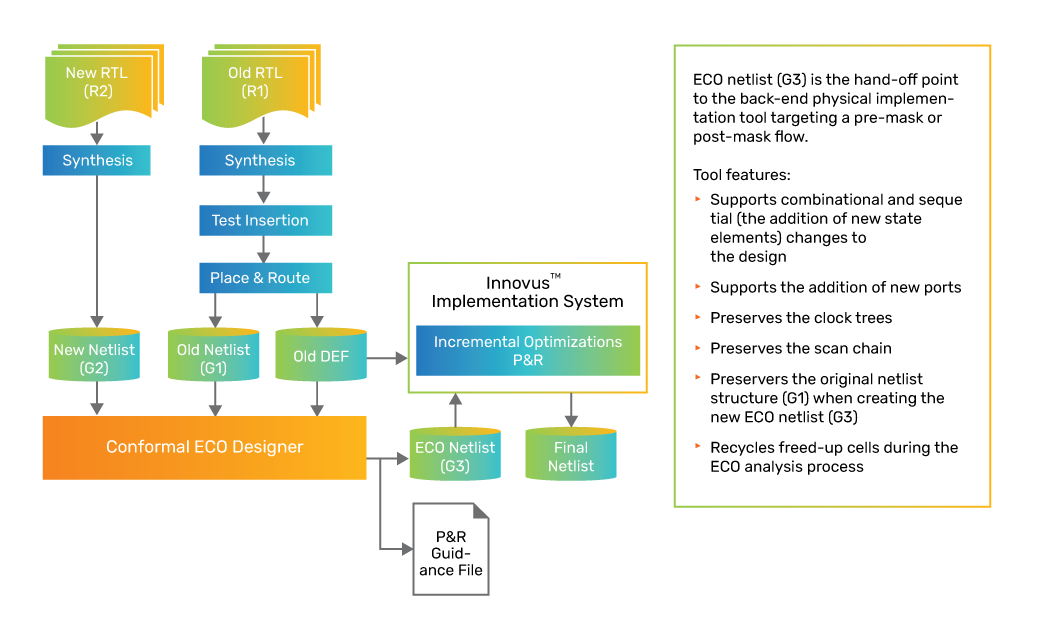

Regardless of design flow stage, Cadence offers comprehensive and automatic ECO solutions. Conformal ECO Designer handles ECO automation for RTL-level functional changes; Genus Synthesis Solution manages logic synthesis and ECO logic optimization; and Innovus Implementation System manages the physical implementation of the ECO changes. The combination brings automation and predictability to the ECO process.

Conformal ECO Designer

Conformal ECO Designer is a unique technology that offersfunctional ECO analysis, optimization, and generation capability. It combines proven equivalence checking and functional checks, and uses formal techniques to analyze, abstract, and implement the functional ECO.

Conformal ECO Designer is available in two configurations: an XL offering, which targets primarily the pre-mask ECO flow, and a GXL offering, which targets the pre-mask and post-mask ECO flow with metal layers and spare gates. The GXL configuration leverages physical database knowledge to generate ECO placement guidance for downstream place-and-route tools.

Benefits

Features

Conformal ECO Designer combines logic equivalencechecking for the most complex SoC and datapath-intensive designs with functional ECO analysis, design netlist modification, and logic optimization.

Equivalence checking for ECOs

During development, a design will undergo numerous iterations, and each step might introduce logical bugs. Conformal ECO helps designers to identify and correct violations immediately by checking the functional equivalence of different versions of a design at various stages.

In an ECO implementation process, equivalence checkingplays an important role. It identifies the incompatiblemodules and logic cones during ECO analysis. For instance, in Figure 2, the original netlist is compared against the new netlist to determine what has changed. In addition, equivalence checking is used at the end of the process to ensure the ECO implementation was successful in both front-end and back-end signoff.

Functional ECO analysis

Conformal ECO Designer provides an ECO analysis engine to identify the discrepancy between the original design netlist and the new one. With this engine, rather than analyzing ECOs on the entire design, users can more efficiently inspect specific modules within the design hierarchy. Once the ECO analysis is completed and the logic changes optimized, Conformal ECO Designer will modify the original netlist to add new functions and output an ECO netlist. In addition, Conformal ECO Designer can create an ECO script that can be used to directly change the placeand-route database.

Spare gate mapping for post-mask ECOs

Conformal ECO Designer (GXL) can also read the DEF layout database corresponding to the original design netlist, LEF, Liberty synthesis libraries, and SDC to optimally map ECO logic to standard cell and gate-array spare gates. The mapping engine will be influenced by timing and spare cell location. With this function, designers can estimate ECO feasibility at an early stage and drive convergence in the back-end implementation flow.

Conformal ECO Designer (GXL) can also recycle freed-upcells in the ECO mapping process. The output is the ECO netlist and a spare gate mapping file, which instructs the place-and-route tool on how to map the newly added ECO logic to specific spare logic resources in the layout.

Smart setup and diagnosis

Conformal ECO Designer includes a set of intelligent analysis commands to ease setup and diagnosis. For example, Smart setup investigates the current environment and automatically fixes common setup issues for new users. In tandem, non-equivalent analysis can be invoked if non-equivalences are encountered and can present concise root cause information for quicker debug. For hierarchical designs, Conformal ECO Designer includes smart technology for accelerating setup requirements through boundary condition profiling.