Brochure

Initiator Controller IP for MIPI SoundWire

Overview

Overview

Today’s leading-edge mobile devices provide increasingly integrated functionality that enables growing volumes of content and video, more ways to control and interact, and longer battery life. The MIPI Alliance defines semiconductor standards for mobile devices that support growing complexity and reduced device form factor.

The Cadence IP Family for MIPI Protocols delivers area-optimized interface IP with the low power and high performance required for today’s leading-edge devices. One member of this family is the Cadence Initiator Controller IP for MIPI SoundWireSM v1.2, providing low-cost, low-power connectivity for audio data transport and control.

Developed by experienced teams with industry-leading domain expertise and extensively validated with multiple hardware platforms. The Controller IP is engineered to quickly and easily integrate with other MIPI compliant IP.

The Controller IP is part of the comprehensive Cadence Design IP portfolio comprised of Interface, memory, analog, and system and peripheral IP.

Product Details

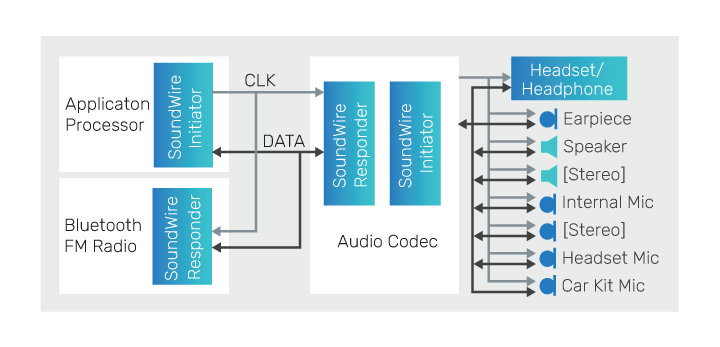

The Controller IP is designed to provide low-cost, low-power connectivity for audio data transport and control. The SoundWire interface is utilized to provide two types of connectivity. The first carries PCM audio data between a mobile application processor and a standalone audio codec or Bluetooth/FM radio controller. The second type carries PDM audio between the audio codec and MEMS microphone or speaker amplifiers.

Benefits

Key Features

Register and Command/Response FIFO Access

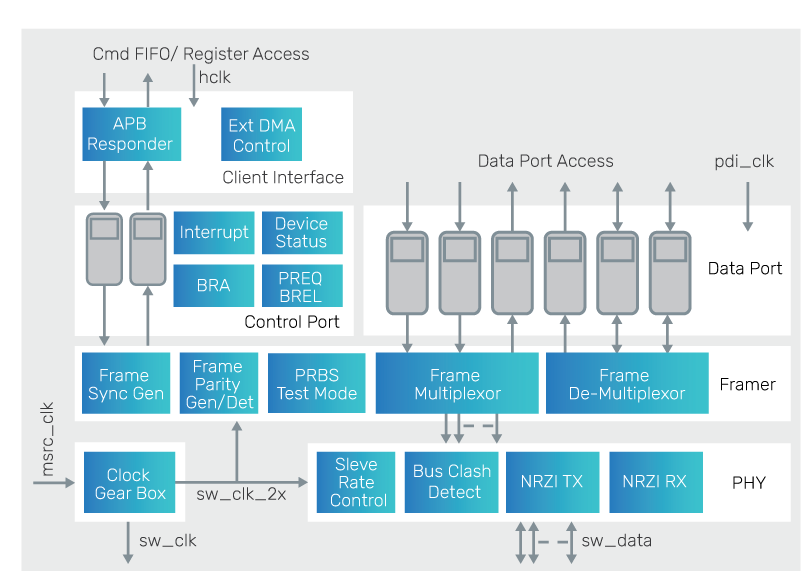

The control registers can be accessed from a 32-bit AHB-Lite client interface. All registers are mapped to host memory space. Certain timing critical registers are banked to allow synchronous switching without interruption to data streams. The initiator controller also deploys two 32-bit command FIFOs for command issuance (TX) and status tracking (RX). They are accessible through the AHB interface or direct command/response to be attached to an external DMA engine.

Control Port

The control port supports READ/WRITE/PING commands generation. It also generates synchronization patters that allow responder controllers to synchronize to the bus. The control port controls the bus release mechanism as well as monitoring the status of all devices that are attached to the bus and rises an interrupt in case of status change

Data Port

Frame Transport

The initiator controller supports isochronous, TX-controlled, RX controlled, and fully asynchronous transport modes and standard-based frame parameters: offset and sub-frame offset, Hstart and Hstop, sample interval, BlockPackingMode, BlockGroupCount, and LaneSelect.

Digital PHY Interface

The Controller IP provides a standard interface to the external PHY module with data, data enable, bus keeper enable signals, and slew rate control output. It also provides initialization and calibration logic for training the DQS alignment for each data slice.