TSMCとケイデンスが協業し、AI主導の先端ノードの設計フロー、シリコン実証済みの IPおよび3D-ICソリューションを提供

26 Sep 2024

要旨:

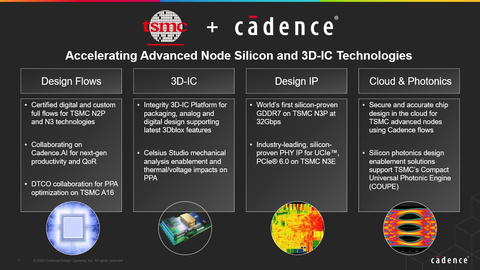

- 最新のTSMC N2PおよびN3テクノロジに対応したAI主導のデジタルおよびカスタム設計フローを提供

- PPAを最適化するA16設計ソリューションでケイデンスとTSMCが協業

- パッケージング、アナログ、デジタル設計を統合したCadence Integrity 3D-IC Platformが最新の3Dblox機能をサポート

- Celsius Studioによるメカニカル解析、熱/電圧によるパワー/IR/STAへの影響、What-if解析を含む協業

- TSMC N3テクノロジ上の32Gbpsで動作する業界初のシリコン実証済みGDDR7 IPを含む、設計IPがAI factoryを強化

- ケイデンスのソリューションはTSMCシリコンフォトニクス・テクノロジーをサポートしており、クラウド上でのセキュアなチップ設計をサポート

ケイデンス・デザイン・システムズ社(本社 米国カリフォルニア州サンノゼ市、以下ケイデンス)は、9月25日(米国時間)、TSMCと協業し、AIを活用した先端ノード設計と3D-ICの生産性を高め、製品性能を最適化することを発表しました。AIアプリケーションの急速な普及により、膨大なデータセットと計算を処理できる高度なシリコン・ソリューションに対するかつてない需要が生まれています。こうした急増する要件に対応するため、業界は先端ノード・シリコンと3D-IC技術の限界に挑戦しています。

TSMCとケイデンスはこの革命の最前線に立ち、性能を向上させながら市場投入までの時間を短縮できるよう、顧客のために全力を尽くしています。

ケイデンスはTSMCと協業し、AIを活用した先端ノード設計と3D-ICの生産性を高め、製品性能を最適化します。AIアプリケーションの急速な普及により、膨大なデータセットと計算を処理できる高度なシリコン・ソリューションに対するかつてない需要が生まれています。TSMCとケイデンスは、性能を向上させながら市場投入までの時間を短縮できるよう、お客様を支援していきます。

TSMCは、業界をリードするケイデンスのデジタルおよびカスタムIC設計フローを、TSMCの最新のN3およびN2Pプロセス・テクノロジでの実装およびサインオフ用に認定しました。長年の DTCO(Design Technology Co-Optimization)パートナーとして、TSMCとケイデンスは、A16の消費電力、性能、面積(PPA)を最適化するために協力し、バックサイド配線などの高度な機能を可能にするEDA機能を追加することで、その伝統を引き継いでいます。

ケイデンスとTSMCはまた、AIを活用した次世代のデジタルおよびアナログ設計自動化を推進するため、Cadence.AIでも協業しており、業界をリードする生産性と結果品質を実現しています。Cadence.AIは、設計と検証のあらゆる側面をカバーするチップ・トゥ・システムのAIプラットフォームです。TSMCとケイデンスの協業は、主に3つの領域に焦点を当てています。

- Cadence® Cerebrus™ Intelligent Chip Explorerは、AIをデジタル設計に適用し、最適なPPAに収束

- Cadence Joint Enterprise Data and AI (JedAI) プラットフォームは、設計デバッグと解析に生成AIを使用し、PPA解析を支援

- ケイデンスのVirtuoso® Studioは、レガシーなカスタム・アナログ設計を最新のノードに移行し、回路の最適化と高シグマ・モンテカルロ解析を実行

Cadence Integrity™ 3D-ICプラットフォームは、最先端のシステムレベル探索ソリューションであり、パッケージング、アナログ、デジタルのインプリメンテーションを統合するシングルベンダープラットフォームであるため、効率的な3D-IC設計が可能です。これは、最新の3Dblox機能と構成要素をすべてサポートすることで、技術革新の新たな機会を切り開くものです。TSMC 3DFabric™技術の超高密度相互接続を可能にするため、TSMCとケイデンスは、ダイ間およびダイから基板への接続に対応した次世代の大容量基板ルーターで協業しています。

マルチフィジックス解析と最適化は、3D-IC技術の成功に不可欠な要素です。TSMCとケイデンスは、電気/熱解析に加えてTSMC 3DFabricの歪み/応力解析を可能にするために協力しており、ケイデンスのCelsius™ Studioの反り/応力解析シミュレーション結果が検証されています。電力/IR/STAに対する熱と電圧の影響も、TSMC 3DFabric用のCadence Integrity 3D-IC Platform内で有効化され、検証されています。

AI Factoryのデータに対する飽くなき欲求は、相互接続に対する要件を高め、消費電力のエンベロープを押し上げています。ケイデンスは、Universal Chiplet Interconnect Express™ 1.0、PCI Express®(PCIe®) 6.0、TSMC N3上で32Gbpsで動作する世界初のシリコン実証済みGDDR7など、チップレット間やデータセンター間でデータを効率的に移動するための重要なIPを幅広く取り揃えています。これらのチップ間で増大する通信の課題に対処するため、ケイデンスのシリコンフォトニクス設計支援ソリューションは、TSMCのCompact Universal Photonic Engine(COUPE)をサポートしています。

TSMCとケイデンスは、車載分野のリーダーと共同で協力しています。今日の車載設計に含まれるシリコンは増加の一途をたどっており、TSMC N5Aやそれ以降のN3Aなど、現在および将来のプロセス・ノードに対応するIP開発はさらに重要になっています。

TSMCとケイデンスはまた、TSMCの先端プロセス・ノード向けに、クラウド上でも高精度、高品質な設計が行えるように、フロントからバックエンド設計までフローを提供する協業を行いました。この協業により、相互の顧客はケイデンスの幅広いCloud Solutionを採用することで、設計スケジュールを短縮することができます。

TSMCコメント

Dan Kochpatcharin氏(head of Ecosystem and Alliance Management Division)

「ケイデンスとの協業により、TSMCのN2テクノロジ向けにAIに最適化された設計フローを実現し、3D-IC設計の進歩を推進することに成功しました。これは、デジタルおよびカスタムソリューションにおける大きな飛躍を意味し、AIインフラを支える技術革新への道を開くものです。」

ケイデンス・コメント

Chin-Chi Teng(senior vice president and general manager of the Digital & Signoff Group)

「TSMCとケイデンスは、世界の設計をシリコンの現実へと変える長年にわたるパートナーシップで成功を収めてきました。「私たちは、TSMCの最新プロセス技術に対応したAI搭載のEDAソフトウェアによって、シリコン設計の未来に革命を起こそうとしています。TSMC A16や3Dbloxのような次世代技術向けの革新的なソリューションに関する我々の継続的な協力関係は、明日のAI Factoryへの道を開くものです。」

ケイデンスについて

ケイデンスは30年以上にわたり蓄積してきた演算処理ソフトウェア(computational software)の専門知識を基盤とする電子システム設計業界のリーダーです。Intelligent System Design戦略のもと、設計コンセプトを実現するためのソフトウェア、ハードウェア、IPを提供しています。ケイデンスのお客様は、世界で最も革新的な企業であり、ハイパースケールコンピューティング、5G通信、自動車、モバイル、航空宇宙、コンシューマー、産業向け、ヘルスケアなど成長市場において開発される様々なアプリケーションに向けて、チップからボード、システムに至るまで、卓越した電子製品を提供しています。フォーチュン誌は9年連続で、ケイデンス社を「働きがいのある会社ベスト100」に選出しています。ケイデンスに関する詳細についてはcadence.comをご参照ください。

Category: Featured

Media Contacts