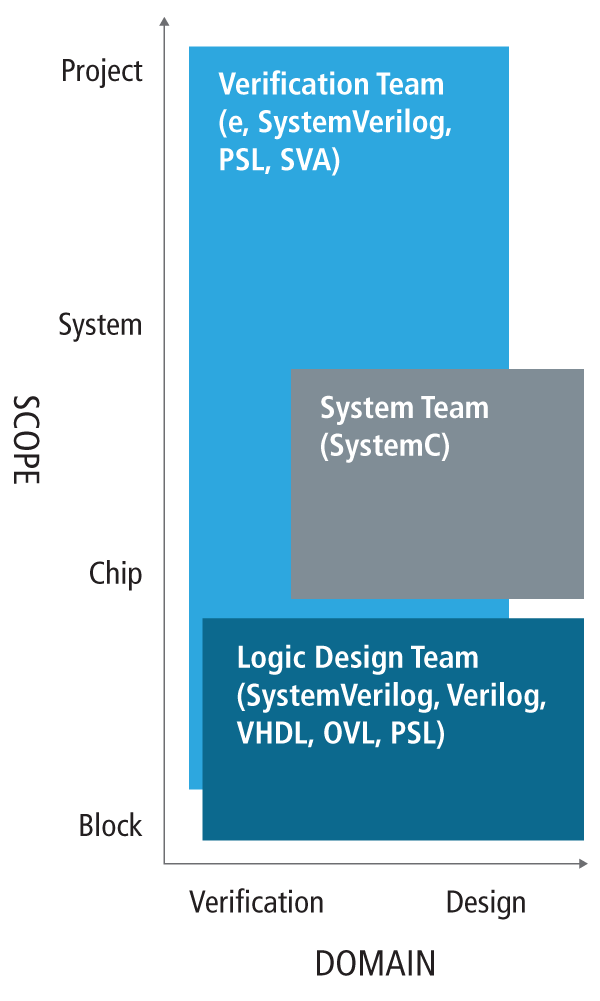

Verilog

Verilog is the incumbent de facto and IEEE standard (IEEE 1364-2001) for RTL design. Used widely since the 1980s and supported by all major EDA vendors, Verilog is the basis for most logic synthesis tools. The language provides good support for ASIC design and verification of simple and moderately complex chips. While it has limitations for more complex designs, Verilog remains the language of choice for a broad cross-section of today’s designers who are not involved in leading-edge projects or who use it as an implementation language in a multi-language design and verification flow.

VHDL

VHDL (IEEE 1076) enjoys a similar position to Verilog in terms of its scope and application to synthesizable design. Its appeal is rooted in its precise semantics and higher level abstraction. VHDL does continue to evolve with the latest update standardized in 2008 (IEEE 1076-2008).

SystemVerilog

SystemVerilog is an IEEE 1800 standard that expands on base Verilog language by adding convenience and abstraction extensions for design, assertions, and verification. The new design features enable more efficient design coding through virtual interfaces, generators, enumerated types, and more. The testbench features enable object-oriented programming using dynamic types, randomization, constraints, and more, so that SystemVerilog can be applied to complex verification tasks.

Property Specific Language (PSL)

PSL (IEEE 1850) supports Verilog, VHDL, and SystemC. It includes multiple abstraction layers for assertion types ranging from low-level boolean and temporal to higher level modeling and verification. PSL does continue to evolve; the latest update is the IEEE 1850-2010 standard.

SystemC

SystemC (IEEE 1666) is ideal for transaction-level modeling and high-performance reference modeling. SystemC can also be synthesized; there’s a technical committee of the Accellera Systems Initiative working on a standard language subset for synthesis. Testbenches for SystemC can be written in SystemC, but many product teams choose UVM and/or e, enabling reuse of the tests at the next lower level of abstraction with Verilog and VHDL.

Encryption

With more design teams distributed across different regions, there’s an increased need to exchange IP within a single company and among companies in a design chain. The IEEE P1735 Recommended Practice for Encryption and Management of Electronic Design IP seeks to standardize the safe interchange of IP. The practice leverages public key encryption that allows multiple tools in the design chain, from multiple vendors, to operate on the IP.