Pegasus Computational Pattern Analytics

High-performance production-proven layout processing

Key Benefits

- In production use for 20+ years to process largest chip databases with unmatched performance

- Fully enabled with data analytics and machine learning

- Production-proven in the cloud with massive distribution and parallelization for faster throughput and linear scalability

- Wide range of applications at both major foundries and fabless semiconductor companies

- Versatile built-in and customizable applications

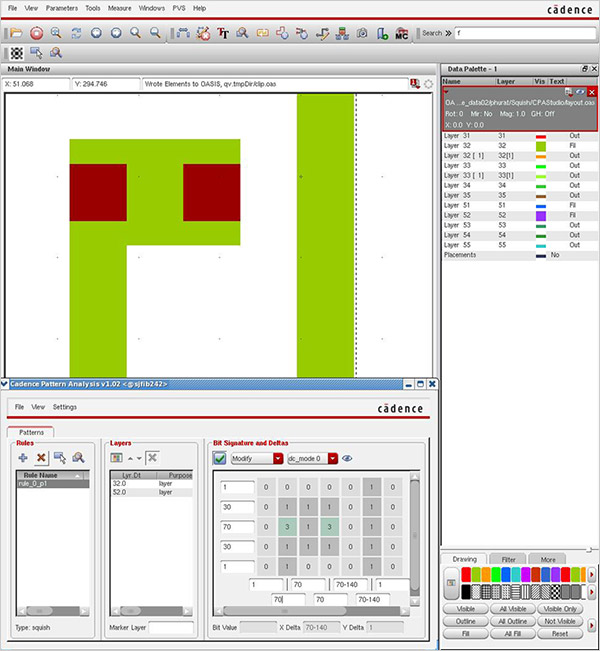

Cadence® Pegasus™ Computational Pattern Analytics (CPA) is an advanced high-performance, pattern-based technology suite comprising of mature production-proven flows and engines as well as new innovative approaches. Pegasus CPA includes feature rich capabilities in the pattern-search/classification/profiling domain while leveraging unique pattern engines such as Squish™ technology, machine-learning (ML), data analysis methods, Python-based scripting, and novel feature-extraction techniques. With Pegasus CPA, design and manufacturing teams can assess layout quality, automate design-quality improvements, accelerate design finishing prior to manufacturing, and develop powerful post-silicon layout analysis. Built-in features allow everyone from beginners to data scientists to leverage the power, capacity, and high performance of Pegasus CPA. Pegasus CPA delivers a richer feature set, more efficient processing capabilties,10-100X faster performance, and larger capacity than traditional DRC-based solutions.

Benefits

High performance

- Optimized algorithms and in-memory operations achieve unmatched processing speeds of up to 100X faster

- Full-chip analysis capability for the largest layout databases in most advanced nodes in hours, not days

- High-productivity CPA Studio GUI integrated in Pegasus Design Review enables faster analysis and dispositioning

Scalable

- Scales linearly with area and number of CPUs

- Easily handles from millions to billions of patterns, markers, and data sets

- Cloud production proven

High capacity

- Efficiently processes large full-chip layouts at the most advanced technology nodes

- Full-chip processing, optimization, data mining, model training, and pattern harvesting

- End-to-end flows have been developed to support up to billions of patterns with optimized CPU and memory usage

Production proven

- In production use at major foundries to screen incoming tapeouts

- Enables urgent and critical foundry production fixes

- Foundation of pattern databases used to gather, monitor, and mitigate yield detractors

- In-design optimizations using foundry kits improve the yield of incoming designs

Versatile applications

- Streamlined design optimization

- Single-pass, single-deck search and optimization

- Find exact or similar patterns based on pattern banks or ML models

- Automatically replace or optimize patterns during design implementation

- Score patterns based on built-in or customer criteria

- Increases recommended rules usage and DFM score using foundry kits to statistically improve yield

- Integrated in Innovus™ Implementation System, Virtuoso® Layout Suite, and Pegasus Design Review Environment

- Saves hours with automated DRC fixing

- Interactive layout analysis

- Interactive pattern capture, editing, search, profiling, and optimization integrated in Pegasus Design Review Environment

- Allows quick deck development, update, and validation

- Interactive GUI-driven flows with synchronized layout and results viewing

- Pattern analytics, profiling, and classification

- Automatically and quickly measures layout dimensions to generate pattern profiling reports and histograms

- Efficient layout feature extraction is fed into ML engine for powerful layout analytics

- Identifies most frequent patterns and outliers, and groups similar patterns

- Yield detractor monitoring

- ML-based hotspot prediction, feature extraction, and Python-based analytics

- Creation and maintenance of pattern database of yield detractors, including pattern scoring, complexity analysis, and similarity

- Enables systematic pattern-based dispositioning of yield detractors

- Pattern capture, generation, and enumeration

- Efficiently captures and compares full chip pattern databases with full coverage

- Pattern comparison identifies new layout patterns in incoming product

- Generates and varies patterns of interest within their context used for DRC deck validation and OPC calibration, and tests key generation for process hotspot coverage

- Hierarchy injection

- Creates hierarchical layout from flat layout or flattened layout

- Recovers hierarchy from layout that has been flattened

- Reduced database size and accelerates subsequent processing

Training and Support

Need Help?

Training

The Training Learning Maps help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.

Find Answers in cadence technical forums